集成沟道二极管与肖特基二极管的SiC-MOSFET器件及制备方法

本发明属于半导体器件,涉及一种集成沟道二极管与肖特基二极管的sic-mosfet器件。

背景技术:

1、功率半导体器件承担着开关、驱动以及整流器的作用,功率sic-mosfet具有开关转换频率高,输入阻抗大,热稳定性好等优良特性,而节能先进的功率sic-mosfet逐渐成为我国信息产业和效能经济的重要基石。功率sic-mosfet的应用在日常生活、各个行业非常广泛,有现代电子芯片的地方就有功率sic-mosfet,它是电子芯片安全高效且精确处理信息的重要一环。随着半导体行业在技术和工艺上的不断优化,不仅要求功率器件的静态特性优良,同样也要求其动态特性更好,故而对开关速度和开关损耗有了更高的要求。

2、近年来随着sic-mosfet电学特性、工艺制造技术以及可靠性的不断提升。相比于si双极功率器件,sic-mosfet的单极性导通的特点使其具有更优良的开关特性和更低的开关损耗,这使得sic-mosfet有望在高频应用中替代si-igbt。在许多电力电子系统应用中,例如电机驱动以及dc-dc变换器,需要使用续流二极管进行续流,理论上可以直接使用sic-mosfet体二极管充当续流二极管,但sic-mosfet高的体二极管导通压降和双极退化效应使得其在续流过程中会产生较大的损耗并且导致器件性能退化。因此,sic-mosfet在应用过程中,业界经常采取反并联肖特基二极管的方式进行续流,但这样一方面会增加模块的体积和成本,另一方面会引入寄生电感从而限制sic-mosfet的工作频率。

3、为了解决以上问题,本发明设计了一种集成沟道二极管和肖特基二极管结构的sic-mosfet器件。器件的第三象限导通压降显著降低,反向恢复特性显著提升,并消除了双极退化效应。同时,虚拟栅的引入可以有效减少电极间电容耦合,降低了器件的反馈电容和栅极电荷,提高器件的开关速度。

技术实现思路

1、有鉴于此,本发明的目的在于提供一种集成沟道二极管和肖特基二极管的sicmosfet器件,使器件的第三象限导通压降显著降低,反向恢复特性显著提升,提高器件的开关速度,并消除双极退化效应。

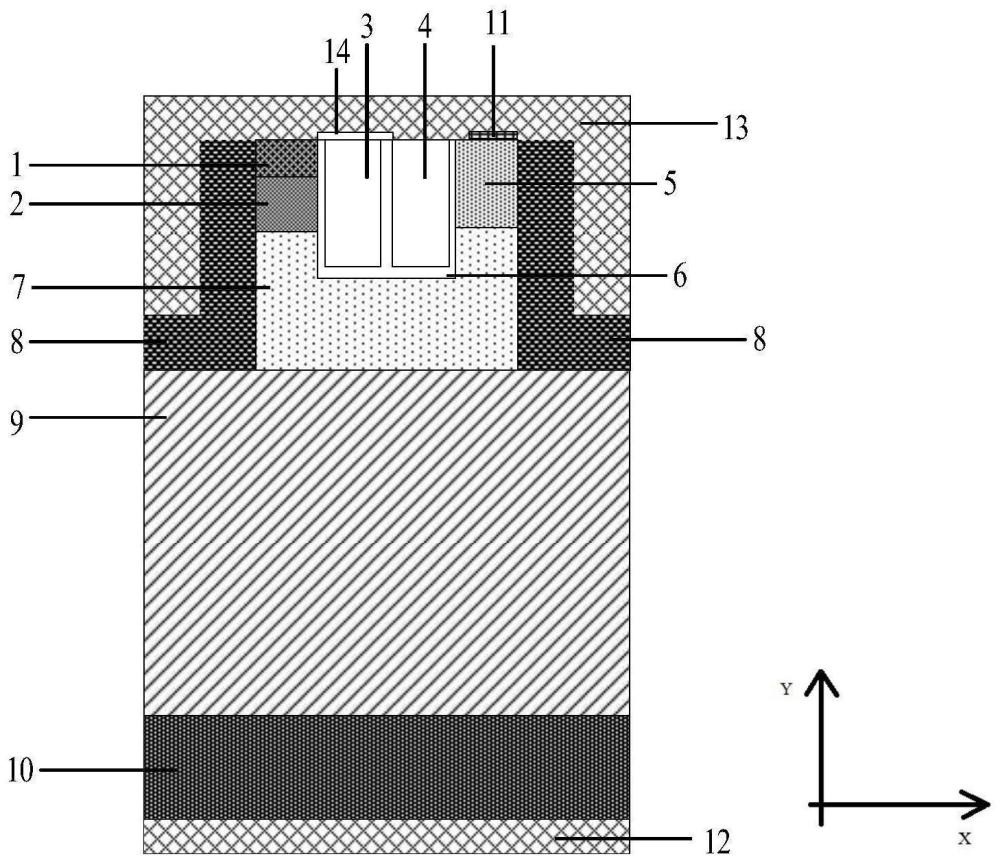

2、为达到上述目的,本发明一方面提供了一种集成沟道二极管与肖特基二极管的sic-mosfet器件,该器件包括:

3、n+衬底区;

4、漂移区,位于所述n+衬底区表面;

5、n-csl,位于所述漂移区表面;

6、源极p+区,位于所述漂移区表面,且位于所述n-csl两侧;

7、氧化层,位于所述n-csl中;

8、p-body,位于所述n-csl表面;

9、源极n+区,位于所述p-body表面;

10、n-区,位于所述n-csl表面;

11、沟槽栅极,位于所述氧化层中,通过所述氧化层与所述源极n+区、p-body和n-csl相隔;

12、虚拟栅,位于所述氧化层中,通过所述氧化层与所述沟槽栅极、n-区和n-csl相隔;以及

13、肖特基结,位于所述n-区表面。

14、进一步的,该器件的源极与源极n+区、n-区和源极p+区短接。

15、进一步的,虚拟栅、n-区、氧化层、漂移区和n+衬底区构成集成的沟道二极管,其中,n-区为该沟道二极管的漏极,n+衬底区为该沟道二极管的源极,虚拟栅为该沟道二极管的栅极。

16、进一步的,通过n-区表面的肖特基结实现沟道二极管与肖特基二极管的并联。且通过改变肖特基结在n-区表面的覆盖面积,可以改变虚拟栅对肖特基二极管提供反向电流的通道大小,具体地,在n-区表面全部淀积肖特基结时,虚拟栅将会为肖特基二极管增大反向电流的通道,使肖特基二级管更容易导通。

17、另一方面,本发明提供了一种集成沟道二极管与肖特基二极管的sic-mosfet器件的制备方法,该方法包括以下步骤:

18、s1、刻蚀衬底形成器件的源极、栅极以及n-csl的区域;

19、s2、在n-csl区域两侧进行离子注入形成源极p+区;

20、s3、通过双槽技术将两侧的源极p+区下拉;

21、s4、在n-csl区域刻蚀出氧化层区域;

22、s5、在源极p+区与氧化层区域之间的n-csl区域中,通过离子注入形成p-body、源极n+区和n-区,其中,源极n+区位于所述p-body之上,n-区通过氧化层与p-body和源极n+区相隔;

23、s6、在氧化层区域中进行氧化、多晶硅填充、氧化以形成沟槽栅极和虚拟栅;

24、s7、淀积金属电极形成肖特基结、源极、栅极和漏极。

25、本发明的有益效果在于:本发明在传统的sic-mosfet器件的基础上,改变栅极结构,将原本栅极一部分变为虚拟栅,同时,将右侧原本源极n+区与p-body区域变成n-区。将n-区作为漏极,n+衬底区作为源极,虚拟栅作为栅极,以形成沟道二极管,并在n-区上淀积金属形成肖特基结,从而集成了沟道二极管与肖特基二极管。

26、在反向恢复时,体二极管被沟道二极管与肖特基二极管抑制,大幅降低了寄生pn结二极管空穴的注入,消除sic-mosfet的双极退化效应,相比于传统sic-mosfet器件,反向恢复电荷降低了57.5%,反向峰值电流降低了53.4%,反向恢复时间降低了30%,最终改善了器件的反向恢复性能。同时,虚拟栅的引入可以有效减少电极间电容耦合,大幅降低了器件的反馈电容和栅极电荷,提高器件的开关速度,其中,相比较传统sic-mosfet器件,反馈电容降低了53%,栅极电荷降低了43.6%。此外,第三象限时,由于集成了沟道二极管与肖特基二极管,加宽反向电流流过的通道,在注入大电流的时候,沟道二极管与肖特基二极管共同承担大电流,成功抑制了体二极管开通。综上所述,通过设计了一种集成沟道二极管和肖特基二极管结构的sic-mosfet器件,提高了器件的第三象限特性,降低了器件的反向恢复电荷、反向峰值电流和反向恢复时间,最终改善了器件的反向恢复性能。

27、本发明的其他优点、目标和特征在某种程度上将在随后的说明书中进行阐述,并且在某种程度上,基于对下文的考察研究对本领域技术人员而言将是显而易见的,或者可以从本发明的实践中得到教导。本发明的目标和其他优点可以通过下面的说明书来实现和获得。

技术特征:

1.一种集成沟道二极管与肖特基二极管的sic-mosfet器件,其特征在于:该器件包括:

2.根据权利要求1所述的sic-mosfet器件,其特征在于:该器件的源极与源极n+区(1)、n-区(5)和源极p+区(8)短接。

3.根据权利要求1所述的sic-mosfet器件,其特征在于:所述虚拟栅(4)、n-区(5)、氧化层(6)、漂移区(9)和n+衬底区(10)构成所述沟道二极管,其中,所述n-区(5)为该沟道二极管的漏极,所述n+衬底区(10)为该沟道二极管的源极,所述虚拟栅(4)为该沟道二极管的栅极。

4.根据权利要求3所述的sic-mosfet器件,其特征在于:通过所述n-区(5)表面的肖特基结(11)实现沟道二极管与肖特基二极管的并联。

5.根据权利要求4所述的sic-mosfet器件,其特征在于:通过改变所述肖特基结(11)的覆盖面积,以改变虚拟栅(4)对肖特基二极管提供反向电流的通道大小。

6.一种集成沟道二极管与肖特基二极管的sic-mosfet器件的制备方法,其特征在于:该方法包括以下步骤:

技术总结

本发明涉及一种集成沟道二极管和肖特基二极管结构的SiC‑MOSFET器件及制备方法,属于半导体器件技术领域。该器件集成的沟道二极管由虚拟栅、N‑区、N‑drift区、N+衬底区以及栅氧化层组成,其中N‑区作为漏极,N+衬底区作为源极,虚拟栅作为栅极,形成沟道二极管。通过在低掺杂的N‑区上淀积金属形成肖特基结,并且可以通过改变肖特基结长度来改变虚拟栅的作用。该器件在反向恢复时,体二极管被沟道二极管与肖特基二极管抑制,大幅降低了寄生PN结二极管空穴的注入,消除SiC‑MOSFET的双极退化效应,同时虚拟栅的引入可以有效减少电极间电容耦合,使反馈电容和栅极电荷大大降低。

技术研发人员:陈伟中,肖宇凡,周扬淇,高升,黄义

受保护的技术使用者:重庆邮电大学

技术研发日:

技术公布日:2024/6/30

- 还没有人留言评论。精彩留言会获得点赞!