半导体器件的形成方法与流程

本发明涉及半导体,尤其是涉及一种半导体器件的形成方法。

背景技术:

1、请参照图1,现有技术的垂直功率器件包括:衬底101,依次位于衬底101内并且靠近衬底101表面的阱区102和源区103。从源区103的表面延伸至衬底101内部的沟槽,沟槽内形成有栅多晶硅104,栅多晶硅104与沟槽的侧壁之间通过栅氧化物层105隔开。还包括位于源区103的表面和栅多晶硅104的表面的层间介质层106,层间介质层106内形成有接触孔107,接触孔107穿过源区103延伸至阱区102的内部。其中,对栅多晶硅104和接触孔107以及漏区(位于衬底的背面,图中未示出)施加电压,就可以对垂直功率器件进行开启。开启模式根据需要一般有高开启电压模式、低开启电压模式和高电流开启模式。

2、然而,现有技术的高开启电压模式需要将栅氧化物层的厚度提高,低开启电压模式需要将栅氧化物层的厚度降低。高电流开启模式需要做成双通道。因此,无法在一个垂直功率管上完成。

技术实现思路

1、本发明的目的在于提供一种半导体器件的形成方法,可以在同一个垂直功率器件上同时实现高开启电压、低开启电压和高电流开启这三种模式的开启。

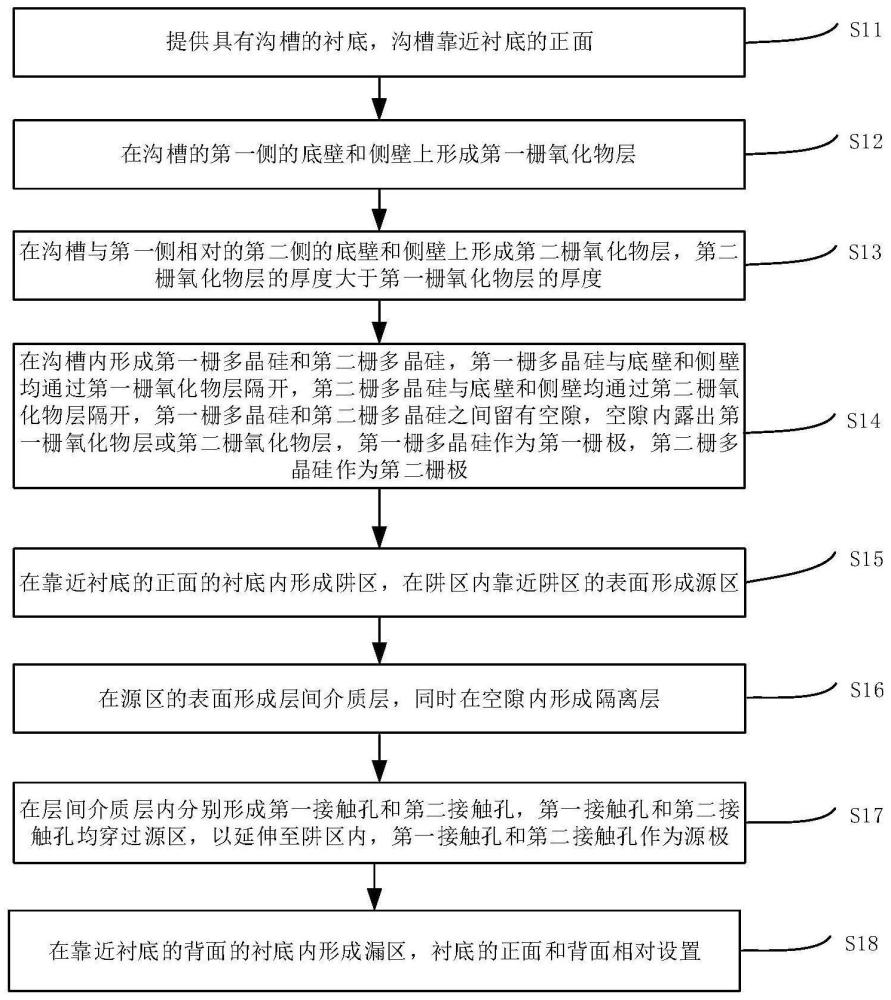

2、为了达到上述目的,本发明提供了一种半导体器件的形成方法,包括:

3、提供具有沟槽的衬底,所述沟槽靠近所述衬底的正面;

4、在所述沟槽的第一侧的底壁和侧壁上形成第一栅氧化物层;

5、在所述沟槽与所述第一侧相对的第二侧的底壁和侧壁上形成第二栅氧化物层,所述第二栅氧化物层的厚度大于所述第一栅氧化物层的厚度;

6、在所述沟槽内形成第一栅多晶硅和第二栅多晶硅,所述第一栅多晶硅与所述底壁和侧壁均通过所述第一栅氧化物层隔开,所述第二栅多晶硅与所述底壁和侧壁均通过所述第二栅氧化物层隔开,所述第一栅多晶硅和第二栅多晶硅之间留有空隙,空隙内露出所述第一栅氧化物层或第二栅氧化物层,所述第一栅多晶硅作为第一栅极,所述第二栅多晶硅作为第二栅极;

7、在靠近所述衬底的正面的衬底内形成阱区,在所述阱区内靠近所述阱区的表面形成源区;

8、在所述源区的表面形成层间介质层,同时在所述空隙内形成隔离层;

9、在所述层间介质层内分别形成第一接触孔和第二接触孔,所述第一接触孔和第二接触孔均穿过所述源区,以延伸至所述阱区内,所述第一接触孔和第二接触孔作为源极;

10、在靠近所述衬底的背面的衬底内形成漏区,所述衬底的正面和背面相对设置。

11、可选的,在所述的半导体器件的形成方法中,提供具有沟槽的衬底的方法包括:

12、提供衬底;

13、从所述衬底的正面开始向下刻蚀部分厚度的衬底,以在所述衬底内形成沟槽。

14、可选的,在所述的半导体器件的形成方法中,在所述沟槽的第一侧的底壁和侧壁上形成第一栅氧化物层的方法包括:

15、在所述沟槽的侧壁和内壁均形成氧化物;

16、去除所述第二侧的侧壁和底壁上的氧化物,以第一侧的底壁和侧壁上分别形成第一栅氧化物层。

17、可选的,在所述的半导体器件的形成方法中,在所述沟槽与所述第一侧相对的第二侧的底壁和侧壁上形成第二栅氧化物层的方法包括:

18、在所述第一栅氧化物层上形成氮化物;

19、自然氧化沟槽的侧壁,以在所述沟槽与所述第一侧相对的第二侧的底壁和侧壁上形成第二栅氧化物层;

20、去除所述氮化物

21、可选的,在所述的半导体器件的形成方法中,在所述沟槽内形成第一栅多晶硅和第二栅多晶硅,所述第一栅多晶硅与所述底壁和侧壁均通过所述第一栅氧化物层隔开,所述第二栅多晶硅与所述底壁和侧壁均通过所述第二栅氧化物层隔开,所述第一栅多晶硅和第二栅多晶硅之间留有空隙,空隙内露出所述第一栅氧化物层或第二栅氧化物层的方法包括:

22、向沟槽内填充多晶硅;刻蚀所述多晶硅使得所述多晶硅形成空隙,剩余的所述多晶硅形成第一栅多晶硅和第二栅多晶硅。

23、可选的,在所述的半导体器件的形成方法中,在所述源区的表面形成层间介质层,同时在所述空隙内形成隔离层的方法包括:

24、在所述衬底的表面沉积氧化物,以形成层间介质层,同时,所述氧化物填充空隙,以形成隔离层。

25、本发明还提供了一种半导体器件的形成方法,包括:

26、提供具有间隔的第一沟槽和第二沟槽的衬底,所述第一沟槽和第二沟槽均靠近所述衬底的正面;

27、在所述第一沟槽内形成第一栅氧化物层和第一栅多晶硅,所述第一栅多晶硅通过所述第一栅氧化物层与所述第一沟槽的侧壁及底壁均隔开;

28、在所述第二沟槽内形成第二栅氧化物层和第二栅多晶硅,所述第二栅多晶硅通过所述第二栅氧化物层与所述第二沟槽的侧壁及底壁均隔开,所述第二栅氧化物层的厚度大于所述第一栅氧化物层的厚度,所述第一栅多晶硅作为第一栅极,所述第二栅多晶硅作为第二栅极;

29、在靠近所述衬底的正面的衬底内形成阱区,在所述阱区内靠近所述阱区的表面形成源区;

30、在所述源区的表面形成层间介质层;

31、在所述层间介质层内分别形成第一接触孔和第二接触孔,所述第一接触孔和第二接触孔均穿过所述源区,以延伸至所述阱区内,所述第一接触孔和第二接触孔作为源极;

32、在靠近所述衬底的背面的衬底内形成漏区,所述衬底的正面和背面相对设置。

33、可选的,在所述的半导体器件的形成方法中,提供具有间隔的第一沟槽和第二沟槽的衬底的方法包括:

34、提供衬底;

35、从所述衬底的正面开始向下刻蚀部分厚度的衬底,以在所述衬底内形成间隔的第一沟槽和第二沟槽。

36、可选的,在所述的半导体器件的形成方法中,所述第一沟槽和第二沟槽的横截面均为条形状,所述第一沟槽和第二沟槽呈十字交叉的形式设置。

37、可选的,在所述的半导体器件的形成方法中,所述第一沟槽和第二沟槽的横截面均为条形状,所述第一沟槽和第二沟槽平行设置。

38、在本发明提供的半导体器件的形成方法中,在同一个半导体器件中同时形成第一栅多晶硅和第二栅多晶硅以及厚度较高的第一栅氧化物层和厚度较低的第二栅氧化物层。分别向第一栅多晶硅、第一接触孔和第二接触孔施加电压,即可形成高电压开启模式。分别向第二栅多晶硅、第一接触孔和第二接触孔施加电压,即可形成低电压开启模式。同时向第一栅多晶硅、第二栅多晶硅、第一接触孔和第二接触孔施加电压,即可形成厚栅氧化物层和薄栅氧化物层两侧同时开启的高电流开启模式。

39、进一步的,本发明为四端口器件,除源极和漏极外,本发明包含两个栅极端。在对半导体器件进行封装的时候,只需要变更打线模式分别向第一栅多晶硅、第二栅多晶硅、第一接触孔和第二接触孔其中不同的部位施加电压就可以形成不同的开启模式,从而达到了将多个开启模式集成在一个垂直功率管中的目的。

技术特征:

1.一种半导体器件的形成方法,其特征在于,包括:

2.如权利要求1所述的半导体器件的形成方法,其特征在于,提供具有沟槽的衬底的方法包括:

3.如权利要求1所述的半导体器件的形成方法,其特征在于,在所述沟槽的第一侧的底壁和侧壁上形成第一栅氧化物层的方法包括:

4.如权利要求1所述的半导体器件的形成方法,其特征在于,在所述沟槽与所述第一侧相对的第二侧的底壁和侧壁上形成第二栅氧化物层的方法包括:

5.如权利要求1所述的半导体器件的形成方法,其特征在于,在所述沟槽内形成第一栅多晶硅和第二栅多晶硅,所述第一栅多晶硅与所述底壁和侧壁均通过所述第一栅氧化物层隔开,所述第二栅多晶硅与所述底壁和侧壁均通过所述第二栅氧化物层隔开,所述第一栅多晶硅和第二栅多晶硅之间留有空隙,空隙内露出所述第一栅氧化物层或第二栅氧化物层的方法包括:

6.如权利要求1所述的半导体器件的形成方法,其特征在于,在所述源区的表面形成层间介质层,同时在所述空隙内形成隔离层的方法包括:

7.一种半导体器件的形成方法,其特征在于,包括:

8.如权利要求7所述的半导体器件的形成方法,其特征在于,提供具有间隔的第一沟槽和第二沟槽的衬底的方法包括:

9.如权利要求7所述的半导体器件的形成方法,其特征在于,所述第一沟槽和第二沟槽的横截面均为条形状,所述第一沟槽和第二沟槽呈十字交叉的形式设置。

10.如权利要求7所述的半导体器件的形成方法,其特征在于,所述第一沟槽和第二沟槽的横截面均为条形状,所述第一沟槽和第二沟槽平行设置。

技术总结

本发明提供了一种半导体器件的形成方法,包括:提供具有沟槽的衬底;在沟槽的第一侧的底壁和侧壁上形成第一栅氧化物层;在沟槽与第一侧相对的第二侧的底壁和侧壁上形成第二栅氧化物层,第二栅氧化物层的厚度大于第一栅氧化物层的厚度;在沟槽内形成第一栅多晶硅和第二栅多晶硅,第一栅多晶硅和第二栅多晶硅之间留有空隙,空隙内露出第一栅氧化物层或第二栅氧化物层,第一栅多晶硅作为第一栅极,第二栅多晶硅作为第二栅极;在靠近衬底的正面的衬底内形成阱区,在阱区内靠近阱区的表面形成源区;在源区的表面形成层间介质层,同时在空隙内形成隔离层;在层间介质层内分别形成第一接触孔和第二接触孔。

技术研发人员:颜树范

受保护的技术使用者:上海华虹宏力半导体制造有限公司

技术研发日:

技术公布日:2024/6/23

- 还没有人留言评论。精彩留言会获得点赞!