半导体器件的制作方法

本公开涉及半导体的领域,并且特别地涉及半导体器件。

背景技术:

1、功率电子应用中使用的晶体管器件常常用硅(si)半导体材料制造。用于功率应用的常见晶体管器件包括si si功率mosfet和si绝缘栅双极晶体管(igbt)。

2、用于功率应用的晶体管器件可以基于电荷补偿原理,并且可以包括有源单元场,该有源单元场包括多个沟槽,每个沟槽包括用于电荷补偿的场板。在一些设计中,沟槽和形成在相邻沟槽之间的台面各自具有细长条纹结构。在一些其它设计中,沟槽和场板各自具有柱状、针状形状。

3、进一步的改善将会是合乎期望的以进一步改善具有柱状场板的晶体管器件的性能,例如通过降低导通状态电阻rds(on)·面积。

技术实现思路

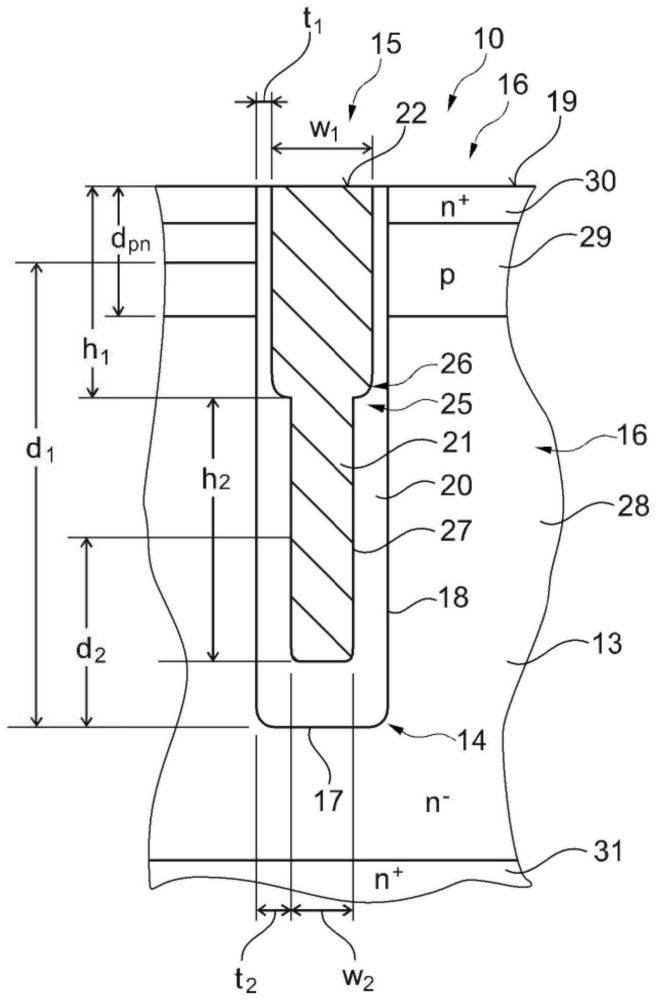

1、根据本发明的实施例,提供了一种晶体管器件,其包括具有第一主表面的半导体衬底和一个或多个晶体管单元。每个晶体管单元包括在半导体衬底中形成的柱状沟槽、布置在柱状沟槽中的柱状场板和围绕柱状沟槽布置的台面。柱状沟槽包括场电介质、基底和侧壁。侧壁从基底延伸到第一主表面,并且场电介质对柱状沟槽的基底和侧壁进行内衬。场电介质在距基底的第一距离处的第一厚度小于场电介质在距基底的第二距离处的第二厚度,其中第一距离大于第二距离。柱状场板在第一距离处的第一周长大于柱状场板在第二距离处的第二周长。

2、根据本发明的实施例,一种方法包括:在具有第一导电类型的半导体衬底的第一主表面中形成多个柱状沟槽,柱状沟槽各自具有基底和从基底延伸到第一主表面的侧壁;在柱状沟槽的基底和侧壁上形成第一电介质层;在第一电介质层上沉积第二电介质层;从柱状沟槽的上部去除第二电介质层的至少一部分;以及将导电材料插入柱状沟槽中以形成场板。

3、本领域技术人员在阅读以下详细描述时并在查看附图时将认识到附加的特征和优点。

技术特征:

1.一种晶体管器件,包括:

2.如权利要求1所述的晶体管器件,还包括至少部分地位于所述柱状沟槽内并且在所述场板和所述台面之间形成电气接触的触头。

3.如权利要求2所述的晶体管器件,其中,所述场板的中心区域保持被所述触头露出。

4.如权利要求1至3中任一项所述的晶体管器件,

5.如权利要求2至4中任一项所述的晶体管器件,其中,所述触头的宽度大于所述场电介质的第一厚度。

6.如权利要求1至5中任一项所述的晶体管器件,其中,所述台面包括:第一导电类型的漂移区域;与所述第一导电类型相对的第二导电类型的本体区域,所述本体区域布置在所述漂移区域上;以及所述第一导电类型的源极区域,布置在所述本体区域上。

7.如权利要求6所述的晶体管器件,其中,所述触头与所述场板、所述源极区域和所述本体区域电气接触。

8.如权利要求6或7所述的晶体管器件,其中,在所述漂移区域中并且与所述柱状沟槽相邻的掺杂浓度沿着从所述第一主表面指向所述半导体衬底的与所述第一主表面相对的第二主表面的方向增加。

9.如权利要求1至8中任一项所述的晶体管器件,其中,所述场板的侧面包括台阶,使得所述场板的上部的宽度大于所述场板的下部的宽度,并且使得所述场电介质在所述柱状沟槽的侧壁的第一区域中具有第一厚度t1,并且在所述柱状沟槽的侧壁的第二区域中具有第二厚度t2,其中,t1≤1.15t2或t1≤1.2t2或t1≤1.5t2。

10.如权利要求1至9中任一项所述的晶体管器件,其中,所述一个或多个柱状沟槽以偏移的行布置。

11.如前述权利要求中任一项所述的晶体管器件,其中,所述一个或多个晶体管单元还包括:

12.如权利要求1至10中任一项所述的晶体管器件,其中,所述一个或多个晶体管单元还包括:

13.如前述权利要求中任一项所述的晶体管器件,

14.一种方法,包括:

15.一种制造晶体管器件的方法,所述方法包括:

16.如权利要求15所述的方法,还包括:

17.如权利要求16所述的方法,还包括选择性地去除所述第一电介质内衬层的材料上的所述半导体衬底的材料,使得所述第一电介质内衬层的上部从所述环形开口的基底突出。

技术总结

本公开涉及半导体器件。根据实施例,提供了一种晶体管器件,其包括具有第一主表面的半导体衬底和一个或多个晶体管单元。每个晶体管单元包括在半导体衬底中形成的柱状沟槽、布置在柱状沟槽中的柱状场板和围绕柱状沟槽布置的台面。柱状沟槽包括场电介质、基底和侧壁。侧壁从基底延伸到第一主表面,并且场电介质对柱状沟槽的基底和侧壁进行内衬。场电介质在距基底的第一距离处的第一厚度小于场电介质在距基底的第二距离处的第二厚度,其中第一距离大于第二距离。柱状场板在第一距离处的第一周长大于柱状场板在第二距离处的第二周长。

技术研发人员:T·R·西米尼克,D·拉福雷特,C·阿尔斯塔特,H·霍弗

受保护的技术使用者:英飞凌科技奥地利有限公司

技术研发日:

技术公布日:2024/10/17

- 还没有人留言评论。精彩留言会获得点赞!