垂直型电容耦合栅控结型场效应晶体管及其制备方法与流程

本申请涉及半导体,具体地,涉及一种垂直型电容耦合栅控结型场效应晶体管及其制备方法。

背景技术:

1、碳化硅(silicon carbide,sic)材料是第三代宽禁带半导体,其禁带宽度3.2ev远大于传统硅材料1.1ev,临界击穿场强高于硅材料一个数量级,具有耐高温高压的优势,同时其饱和漂移速度快,适合制造快速响应的高温高压功率半导体器件,如vdmos(verticaldouble-diffused mosfet)和jfet(junction field-effect transistor,jfet)等器件。

2、垂直导通双扩散的mosfet(vertical double-diffused mosfet,vdmos)器件是一种垂直型半导体器件,同时具有双极晶体管和普通mos器件的优点。vdmos栅极和源极位于器件表面,漏极位于器件背面,其工作原理为栅极控制沟道开启和关断,实现电流从漏极经过体内以及器件表面反型的沟道流向源极,其导通沟道在器件表面。vdmos在开关应用和线性应用中都是理想的功率器件,主要应用于电子开关、适配器、驱动带能源和工业控制等。

3、结型场效应晶体管(junction field-effect transistor,jfet)也是一种三端口半导体器件,工作原理为利用栅极加压控制其与沟道的pn结的反偏实现漏极和源极的关断,栅不加压时通常为常开器件,其导通沟道在器件体内。它具有低噪音、小尺寸和高频响应等优点,常应用于开关器件、电源放大器件和数码电子电路中,满足不同电子设备的要求。

4、cn1238904c为jfet器件,如图1-1所示,单晶硅sic基片1,p-型外延层2,n-型外延层3,p+-型半导体层4,n+型源区层5,p+型栅层7,n+型漏区层9,源极10,栅极11,漏极12。jfet器件的导通沟道位于器件内部,导通沟道为n-型外延层3中,导通沟道在半导体材料内内部,避免sic材料表面迁移率低的问题。由于jfet器件为常开器件,即p+型栅层7(即栅极)上不施压电压情况下,器件是导通的(在图1中用虚线表示电流),必须通过p+型栅层7(即栅极)上施加负电压才能实现器件的关断,限制了其作为功率开关的应用。同时由于p+型栅层7(即栅极)和沟道是pn结的结构,p+型栅层7(即栅极)上无法施加高于3v的电压。对于sic材料,栅极施加3v以上的电压,栅极和沟道或者源极就会导通,导通电流很大影响漏到源的电流特性,栅极无法施加很高的电压导致栅极对沟道的夹断和开启较慢,限制了其作为功率开关的应用。

5、因此,传统的jfet器件的栅极对沟道的夹断和开启较慢,限制了其作为功率开关的应用的技术问题。

6、在背景技术中公开的上述信息仅用于加强对本申请的背景的理解,因此其可能包含没有形成为本领域普通技术人员所知晓的现有技术的信息。

技术实现思路

1、本申请实施例提供了一种垂直型电容耦合栅控结型场效应晶体管及其制备方法,以解决传统的jfet器件的栅极对沟道的夹断和开启较慢,限制了其作为功率开关的应用的技术问题。

2、根据本申请实施例的第一个方面,提供了一种垂直型电容耦合栅控结型场效应晶体管,包括第一掺杂类型的衬底和外延层、至少一个重复单元,其中,所述外延层位于所述衬底之上,所述衬底作为漏区;所述重复单元包括:

3、两个沟槽,所述沟槽自所述外延层的上表面向下形成,且两个所述沟槽在横向间隔设置;

4、栅极介质层,至少形成在所述沟槽的内底;

5、两个栅极,分别形成在两个沟槽的所述栅极介质层之上;

6、第一掺杂类型的源区,形成在两个所述沟槽之间;

7、第二掺杂类型沟道区,形成在所述源区之下;

8、第一掺杂类型沟道区,形成在所述第二掺杂类型沟道区内;

9、所述第一掺杂类型沟道区和所述第二掺杂类型沟道区形成jfet区域,同一个重复单元的jfet区域由两个所述栅极控制。

10、根据本申请实施例的第二个方面,提供了一种垂直型电容耦合栅控结型场效应晶体管的制备方法,包括如下步骤:

11、在第一掺杂类型的衬底之上形成第一掺杂类型的外延层,所述衬底作为漏区;

12、形成至少一个重复单元;

13、形成所述重复单元包括的步骤包括:

14、形成两个沟槽,所述沟槽自所述外延层的上表面向下形成,且两个所述沟槽在横向间隔设置;

15、形成栅极介质层,至少形成在所述沟槽的内底;

16、形成两个栅极,分别形成在两个沟槽的所述栅极介质层之上;

17、形成第一掺杂类型的源区,形成在两个所述沟槽之间。

18、本申请实施例由于采用以上技术方案,具有以下技术效果:

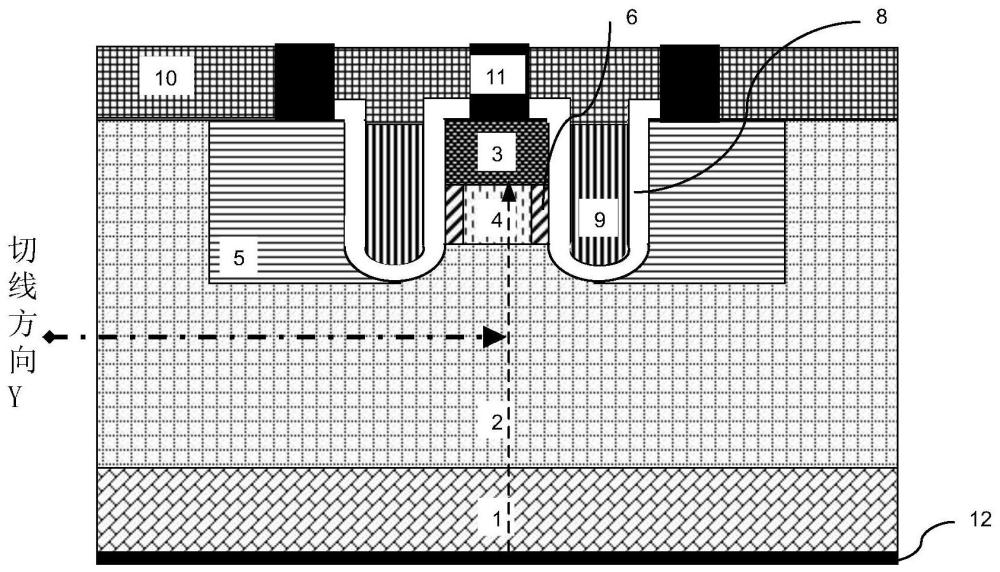

19、同一个重复单元内具有两个沟槽,每个沟槽的内底形成栅极介质层8,栅极9分别形成在两个沟槽的栅极介质层8之上,第一掺杂类型的源区3形成在两个所述沟槽之间;第二掺杂类型沟道区6形成在所述源区3之下;第一掺杂类型沟道区4形成在所述第二掺杂类型沟道区6内。两个沟槽之间的第一掺杂类型沟道区4和第二掺杂类型沟道区6形成jfet区域,其中沟道区4为jfet区域的沟道区,同一个重复单元的jfet区域由两个栅极9控制。同一个重复单元内有两个栅极9,两个栅极9共同对沟道的开启和夹断进行控制,进而实现了对漏区、源区和栅极形成的jfet区域的控制。由于第一掺杂类型沟道区4和第二掺杂类型沟道区6形成自耗尽,在两个栅极9不施加栅极电压的情况下,沟道处于夹断状态器件内部没有导通路径,器件关断。即图2为常关器件,图2中带箭头的虚线是电子流动的方向。在两个栅极9施加栅极电压的情况下,沟道被开启形成导通路径。本申请实施例的垂直型电容耦合栅控结型场效应晶体管,同一个重复单元内的设置有两个栅极9,共同对沟道进行开启和夹断的控制,进而实现对jfet区域的控制。两个栅极9共同控制的方式使得沟道的开启和夹断更快,控制能力较强。

技术特征:

1.一种垂直型电容耦合栅控结型场效应晶体管,其特征在于,包括第一掺杂类型的衬底(1)和外延层(2)、至少一个重复单元,其中,所述外延层位于所述衬底之上,所述衬底作为漏区;所述重复单元包括:

2.根据权利要求1所述的场效应晶体管,其特征在于,还包括:

3.根据权利要求2所述的场效应晶体管,其特征在于,所述第一掺杂类型沟道区(4)和所述第二掺杂类型沟道区(6)形成自耗尽。

4.根据权利要求3所述的场效应晶体管,其特征在于,所述第二掺杂类型沟道区(6)的下底高于所述沟槽的外底。

5.根据权利要求4所述的场效应晶体管,其特征在于,还包括:

6.一种垂直型电容耦合栅控结型场效应晶体管的制备方法,其特征在于,包括如下步骤:

7.根据权利要求6所述的制备方法,其特征在于,形成所述重复单元包括的步骤还包括:

8.根据权利要求7所述的制备方法,其特征在于,形成所述重复单元包括的步骤还包括:

9.根据权利要求8所述的制备方法,其特征在于,形成所述重复单元包括的步骤还包括:

技术总结

本申请实施例提供了一种垂直型电容耦合栅控结型场效应晶体管及其制备方法。器件包括衬底和外延层、至少一个重复单元,外延层位于衬底之上,衬底作为漏区;重复单元包括:两个沟槽,两个沟槽在横向间隔设置;栅极介质层,至少形成在沟槽的内底;两个栅极,分别形成在两个沟槽的栅极介质层之上;第一掺杂类型的源区,形成在两个沟槽之间;第二掺杂类型沟道区,形成在源区之下;第一掺杂类型沟道区,形成在第二掺杂类型沟道区内;第一掺杂类型沟道区和第二掺杂类型沟道区形成JFET区域,同一个重复单元的JFET区域由两个栅极控制。本申请实施例解决了传统的JFET器件的栅极对沟道的夹断和开启较慢,限制了其作为功率开关的应用的技术问题。

技术研发人员:顾鸣远,张晓宇,岳丹诚

受保护的技术使用者:苏州华太电子技术股份有限公司

技术研发日:

技术公布日:2024/7/11

- 还没有人留言评论。精彩留言会获得点赞!