半导体结构的制备方法及半导体结构与流程

本申请涉及半导体,特别是涉及一种半导体结构的制备方法及半导体结构。

背景技术:

1、相关技术中,浅沟槽隔离结构(shallow trench isolation,sti)的制备过程中,通常采用氮化硅(sin)作为掩膜,对衬底进行刻蚀以形成沟槽。这样,不可避免地会对氮化硅的表面进行刻蚀,导致氮化硅的厚度减小,进而导致后续在浅沟槽隔离结构上形成的台阶高度(step height)较小。在后续制程中,由于台阶高度较小,台阶容易在酸洗等工艺中被完全去除,浅沟槽隔离结构的顶表面也可能被部分刻蚀,进而导致浅沟槽隔离结构与器件的有源区(active area,aa)之间存在高度差(即浅沟槽隔离结构的顶表面低于有源区的顶表面),对器件的电学性能造成不利影响。

技术实现思路

1、有鉴于此,本申请实施例为解决背景技术中存在的至少一个问题而提供一种半导体结构的制备方法及半导体结构。

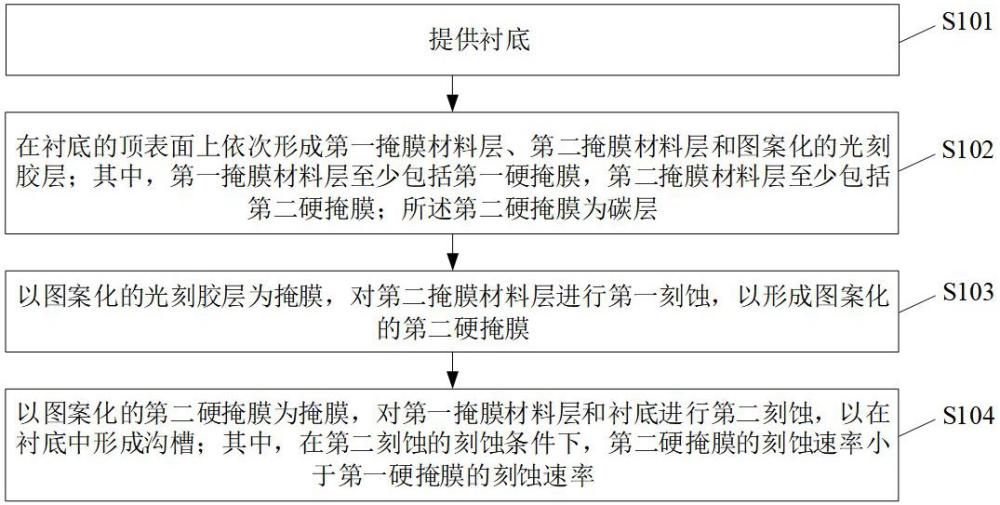

2、第一方面,本申请实施例提供了一种半导体结构的制备方法,包括:

3、提供衬底;

4、在所述衬底的顶表面上依次形成第一掩膜材料层、第二掩膜材料层和图案化的光刻胶层;其中,所述第一掩膜材料层至少包括第一硬掩膜,所述第二掩膜材料层至少包括第二硬掩膜;所述第二硬掩膜为碳层;

5、以所述图案化的光刻胶层为掩膜,对所述第二掩膜材料层进行第一刻蚀,以形成图案化的第二硬掩膜;

6、以所述图案化的第二硬掩膜为掩膜,对所述第一掩膜材料层和所述衬底进行第二刻蚀,以在所述衬底中形成沟槽;其中,在所述第二刻蚀的刻蚀条件下,所述第二硬掩膜的刻蚀速率小于所述第一硬掩膜的刻蚀速率。

7、结合本申请的第一方面,在一可选实施方式中,所述第二硬掩膜的厚度与所述沟槽的深度一致。

8、结合本申请的第一方面,在一可选实施方式中,所述第一硬掩膜为氮化硅层。

9、结合本申请的第一方面,在一可选实施方式中,所述第二刻蚀的刻蚀气体包括溴化氢、氯气和氧气;其中,所述溴化氢和所述氯气的流量比为2:1-5:1,且所述氧气和所述氯气的流量比为4.5:1-9.5:1。

10、结合本申请的第一方面,在一可选实施方式中,进行所述第二刻蚀时,刻蚀气体包括流量为60sccm-70sccm的溴化氢,流量为15sccm-25sccm的氯气和流量为120sccm-140sccm的氧气;反应腔压力设置为5mt-8mt,射频功率设置为400w-600w,偏置电压设置为300v-350v。

11、结合本申请的第一方面,在一可选实施方式中,所述第二掩膜材料层还包括位于所述图案化的光刻胶层和所述第二硬掩膜之间的抗反射层以及位于所述第二硬掩膜和所述第一硬掩膜之间的第一氧化层;所述进行第一刻蚀包括:以所述图案化的光刻胶层为掩膜,刻蚀所述抗反射层,以暴露所述第二硬掩膜的部分表面;以剩余的所述抗反射层为掩膜,刻蚀所述第二硬掩膜,以形成所述图案化的第二硬掩膜;和/或,

12、所述第一掩膜材料层还包括位于所述衬底和所述第一硬掩膜之间的第二氧化层;所述进行第二刻蚀包括:以所述图案化的第二硬掩膜为掩膜,依次刻蚀所述第二掩膜材料层中的位于所述第二硬掩膜和所述第一硬掩膜之间的第一氧化层、所述第一硬掩膜、所述第二氧化层和所述衬底,以形成所述沟槽。

13、结合本申请的第一方面,在一可选实施方式中,所述第二掩膜材料层还包括位于所述第二硬掩膜和所述第一硬掩膜之间的第一氧化层;在所述衬底中形成沟槽之后,所述半导体结构的制备方法还包括:

14、去除所述图案化的第二硬掩膜,以暴露所述第一氧化层的表面;

15、沉积隔离材料,所述隔离材料填充于所述沟槽中,并覆盖所述第一氧化层和所述第一掩膜材料层;

16、对所述隔离材料执行化学机械研磨工艺;其中,执行化学机械研磨后的位于所述沟槽中的所述隔离材料构成浅沟槽隔离结构,位于所述浅沟槽隔离结构上的所述隔离材料构成台阶;所述台阶的顶表面低于所述第一氧化层的顶表面且高于所述第一硬掩膜的顶表面。

17、结合本申请的第一方面,在一可选实施方式中,位于相邻的所述沟槽之间的所述衬底构成凸起结构,所述凸起结构的高度与所述凸起结构的最小线宽的比值为3-3.5,且所述凸起结构的最小线宽与所述凸起结构的最大线宽比值为2/3-3/4;所述凸起结构的线宽沿所述衬底的顶表面向所述衬底的底表面方向增大。

18、结合本申请的第一方面,在一可选实施方式中,所述凸起结构的侧壁所在平面与所述凸起结构的底部所在平面的夹角大于或等于85.5°。

19、第二方面,本申请实施例提供了一种半导体结构,所述半导体结构采用上述任一实施例所述的半导体结构的制备方法制备得到。

20、本申请实施例所提供的半导体结构的制备方法,通过在第一掩膜材料层上设置第二掩膜材料层,第二硬掩膜为碳层,并且,在第二刻蚀的刻蚀条件下,第二掩膜材料层中的第二硬掩膜的刻蚀速率小于第一掩膜材料层中的第一硬掩膜的刻蚀速率,使得第二硬掩膜可以在第二刻蚀中作为第一硬掩膜的保护层,完全保留第一硬掩膜的厚度。如此,可以在光刻胶层的厚度有限的情况下,避免第一硬掩膜的表面被刻蚀,导致第一硬掩膜厚度降低的问题。另外,通过增加第一硬掩膜的高度,进而可以增加后续形成的台阶的高度,使得浅沟槽隔离结构与器件的有源区之间的高度差得到有效保证,使得器件电学性能稳定。

21、本申请附加的方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本申请的实践了解到。

技术特征:

1.一种半导体结构的制备方法,其特征在于,所述半导体结构的制备方法包括:

2.根据权利要求1所述的半导体结构的制备方法,其特征在于,

3.根据权利要求1或2所述的半导体结构的制备方法,其特征在于,

4.根据权利要求1所述的半导体结构的制备方法,其特征在于,

5.根据权利要求1所述的半导体结构的制备方法,其特征在于,

6.根据权利要求1所述的半导体结构的制备方法,其特征在于,

7.根据权利要求1所述的半导体结构的制备方法,其特征在于,

8.根据权利要求1所述的半导体结构的制备方法,其特征在于,

9.根据权利要求8所述的半导体结构的制备方法,其特征在于,

10.一种半导体结构,其特征在于,所述半导体结构采用权利要求1至9任一项所述的半导体结构的制备方法制备得到。

技术总结

本申请实施例涉及一种半导体结构的制备方法及半导体结构。半导体结构的制备方法包括:提供衬底;在衬底的顶表面上依次形成第一掩膜材料层、第二掩膜材料层和图案化的光刻胶层;其中,第一掩膜材料层至少包括第一硬掩膜,第二掩膜材料层至少包括第二硬掩膜;以图案化的光刻胶层为掩膜,对第二掩膜材料层进行第一刻蚀,以形成图案化的第二硬掩膜;以图案化的第二硬掩膜为掩膜,对第一掩膜材料层和衬底进行第二刻蚀,以在衬底中形成沟槽;其中,在第二刻蚀的刻蚀条件下,第二硬掩膜的刻蚀速率小于第一硬掩膜的刻蚀速率。如此,可以增加第一硬掩膜的高度,进而增加台阶的高度,使得浅沟槽隔离结构与器件的有源区之间的高度差得到有效保证。

技术研发人员:郭祝,王宇,陈勇树

受保护的技术使用者:粤芯半导体技术股份有限公司

技术研发日:

技术公布日:2024/5/27

- 还没有人留言评论。精彩留言会获得点赞!