一种抑制漏极电压过冲的碳化硅VDMOS的制备方法与流程

本发明涉及一种抑制漏极电压过冲的碳化硅vdmos的制备方法。

背景技术:

1、碳化硅vdmos作为sic功率器件中的代表性器件,在电动汽车、航空航天、电力转换等领域有广泛的应用。在一些恶劣环境下,电源波动范围大,极少数的漏极电压过冲容易造成碳化硅vdmos的不可恢复损伤,造成器件的可靠性问题。在这种特殊情况,需要抑制漏极过冲的器件以实现漏极波动过冲的抑制,提高器件耐恶劣情况能力。

技术实现思路

1、本发明要解决的技术问题,在于提供一种抑制漏极电压过冲的碳化硅vdmos的制备方法,在漏极出现电压过冲时实现对栅极冲击的缓冲,提高器件的漏极耐压能力。

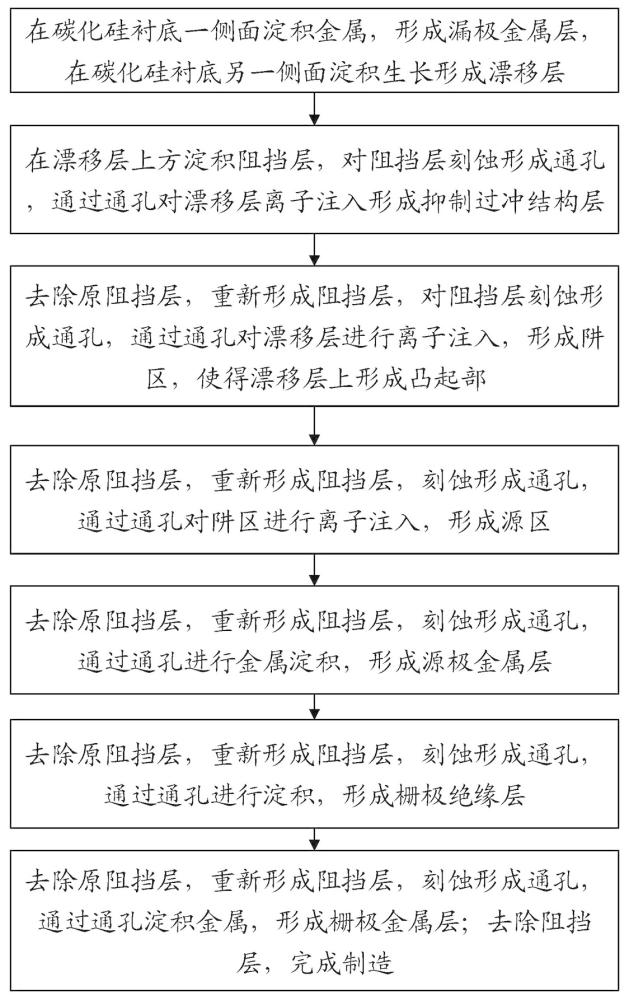

2、本发明是这样实现的:一种抑制漏极电压过冲的碳化硅vdmos的制备方法,其特征在于,包括如下步骤:

3、步骤1、在碳化硅衬底一侧面淀积金属,形成漏极金属层,在碳化硅衬底另一侧面淀积生长形成漂移层;

4、步骤2、在漂移层上方淀积阻挡层,对阻挡层刻蚀形成通孔,通过通孔对漂移层离子注入形成抑制过冲结构层;

5、步骤3、去除原阻挡层,重新形成阻挡层,对阻挡层刻蚀形成通孔,通过通孔对漂移层进行离子注入,形成阱区,使得漂移层上形成凸起部;

6、步骤4、去除原阻挡层,重新形成阻挡层,刻蚀形成通孔,通过通孔对阱区进行离子注入,形成源区;

7、步骤5、去除原阻挡层,重新形成阻挡层,刻蚀形成通孔,通过通孔进行金属淀积,形成源极金属层;

8、步骤6、去除原阻挡层,重新形成阻挡层,刻蚀形成通孔,通过通孔进行淀积,形成栅极绝缘层;

9、步骤7、去除原阻挡层,重新形成阻挡层,刻蚀形成通孔,通过通孔淀积金属,形成栅极金属层;去除阻挡层,完成制造。

10、本发明的优点在于:

11、一、在器件的栅极金属层下方构建了抑制过冲结构层,在漏极出现电压过冲时实现对栅极冲击的缓冲,提高器件的漏极耐压能力;

12、二、器件采用了平面栅结构,栅介质层上设有突起部,在控制沟道区导通部分,仍然保持低栅极介质厚度,以实现良好的栅控能力,在jfet区建立厚介质层,以提高器件的漏极过冲时器件栅极的抗冲击能力;

13、三、抑制过冲结构层在漂移层内部构建,其横向宽度占漂移层宽度的十分之一到六分之一,对器件导电特性影响小;

14、四、抑制过冲结构层到碳化硅衬底的距离为500nm,在器件漏极就实现漏极电压过冲的抑制,对器件的jfet区导电特性影响极小。

技术特征:

1.一种抑制漏极电压过冲的碳化硅vdmos的制备方法,其特征在于,包括如下步骤:

2.如权利要求1所述的一种抑制漏极电压过冲的碳化硅vdmos的制备方法,其特征在于,所述步骤6具体为:去除原阻挡层,重新形成阻挡层,刻蚀形成通孔,通过通孔进行淀积,形成栅极绝缘层,去除原阻挡层,重新形成阻挡层,刻蚀形成通孔,通过通孔进行淀积,形成突起部。

3.如权利要求1所述的一种抑制漏极电压过冲的碳化硅vdmos的制备方法,其特征在于,所述碳化硅衬底的掺杂浓度为2e18cm-3,所述漂移层的掺杂浓度为3e16cm-3,所述抑制过冲结构层的掺杂浓度为5e17cm-3,所述阱区的掺杂浓度为6e16cm-3,所述源区的掺杂浓度为5e19cm-3。

4.如权利要求1所述的一种抑制漏极电压过冲的碳化硅vdmos的制备方法,其特征在于,所述抑制过冲结构层的宽度等于凸起部的宽度。

5.如权利要求1所述的一种抑制漏极电压过冲的碳化硅vdmos的制备方法,其特征在于,所述抑制过冲结构层的宽度为漂移层宽度的十分之一至六分之一。

6.如权利要求1所述的一种抑制漏极电压过冲的碳化硅vdmos的制备方法,其特征在于,所述抑制过冲结构层底部至碳化硅衬底的距离为500nm。

7.如权利要求1所述的一种抑制漏极电压过冲的碳化硅vdmos的制备方法,其特征在于,所述碳化硅衬底、漂移层以及源区均为n型;所述抑制过冲结构层和阱区均为p型。

技术总结

本发明提供了一种抑制漏极电压过冲的碳化硅VDMOS的制备方法,包括:在碳化硅衬底一侧面淀积金属,形成漏极金属层,在碳化硅衬底另一侧面淀积生长形成漂移层;通过离子注入分别形成抑制过冲结构层、阱区以及源区;去除原阻挡层,重新形成阻挡层,刻蚀形成通孔,通过通孔进行金属淀积,形成源极金属层;去除原阻挡层,重新形成阻挡层,刻蚀形成通孔,通过通孔进行淀积,形成栅极绝缘层;去除原阻挡层,重新形成阻挡层,刻蚀形成通孔,通过通孔淀积金属,形成栅极金属层;去除阻挡层,完成制造,在漏极出现电压过冲时实现对栅极冲击的缓冲,提高器件的漏极耐压能力。

技术研发人员:李昀佶,杨光锐,施广彦,张长沙

受保护的技术使用者:泰科天润半导体科技(北京)有限公司

技术研发日:

技术公布日:2024/5/19

- 还没有人留言评论。精彩留言会获得点赞!