一种III-V族半导体超结器件及其制造方法与流程

本发明涉及一种半导体器件,特别地涉及一种iii-v族半导体超结器件及其制造方法。

背景技术:

1、硅的超结结构是指采用交替的pn结构替代传统功率器件中单一低掺杂漂移区作为耐压层。n柱和p柱具有接近一致的掺杂量。

2、图1是现有技术中超结结构示意图。其中电极111为漏极,电极112为栅极,电极113为源极,114为氧化层。在这之中,n代表n型轻掺杂区,n+代表n型重掺杂区,p代表p型轻掺杂区,p+代表p型重掺杂区。其中n区和p区形成了超结结构。

3、如图所示,在截止状态下,依靠p/n柱之间的电荷补偿,超结中的n柱和p柱被分别耗尽,耗尽层从n柱和p柱之间的界面延伸,由于n柱和p柱掺杂浓度相等,因此耗尽层延伸,并几乎完全耗尽从而能提高器件耐压。在导通状态,由于器件耐压与掺杂浓度无关,因此可以将超结器件漂移区的掺杂浓度提高,从而保持更低的导通电阻。超结结构应对n柱尺寸、p柱尺寸和掺杂浓度进行严格控制来保证电荷平衡。

4、早期超结结构的制备方法为多次注入、外延及退火工艺;随着高深宽比刻蚀工艺的发展,开始采用刻蚀深槽、填充及平坦化的方法完成。这些方法在gan超级器件的制备中存在较大问题,例如难以通过注入或生长的方法获得较高的p型有效掺杂;如果是刻蚀沟槽后二次外延,槽内gan填充过程中晶体生长效果不佳,容易形成空洞,且二次生长界面的杂质因素,也容易形成漏电通道。

技术实现思路

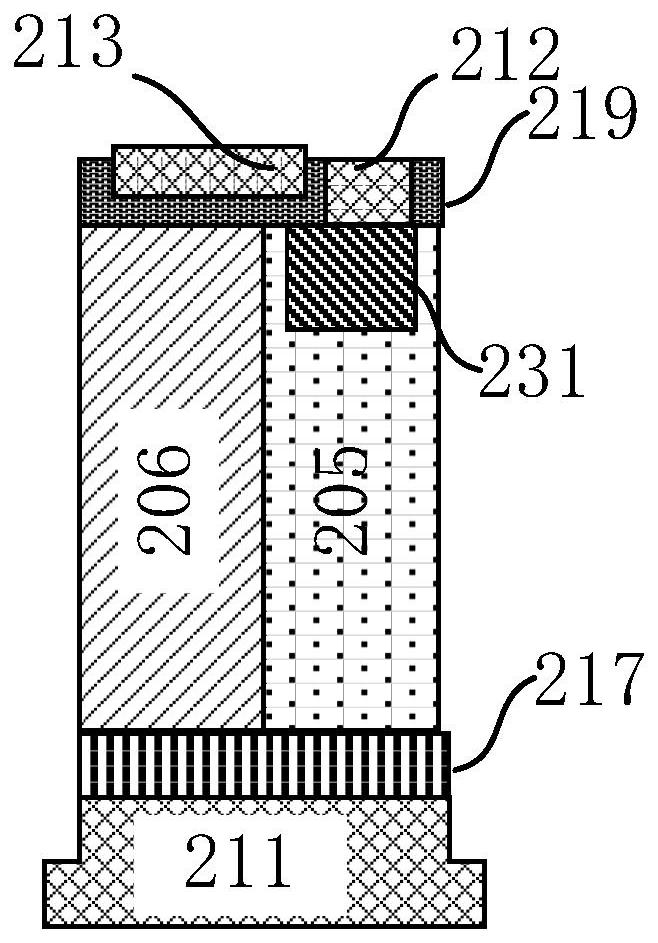

1、针对现有技术中存在的技术问题,本发明提出了一种iii-v族半导体超结器件,包括:第一掺杂柱,其为p-型掺杂;第二掺杂柱,其为n-型掺杂,所述第二掺杂柱和所述第一掺杂柱相邻并位于所述第一掺杂柱的一侧;第一掺杂区,其为n-型掺杂,设置在所述第一掺杂柱上方;第一电极,其设置在所述第一掺杂柱和所述第二掺杂柱下方,至少电耦合至所述第二掺杂柱;第二电极,其设置在所述第一掺杂柱上方,电耦合至所述第一掺杂柱;栅电极,其经配置以控制所述第二电极与所述第二掺杂柱之间的沟道;其中,所述第一掺杂柱和第二掺杂柱为经掺杂的iii-v族半导体材料,所述第一掺杂柱、所述第二掺杂柱与所述第一源电极、栅电极及漏电极形成垂直超结结构,所述第一掺杂柱与所述第二掺杂柱具有大致相同的晶体质量。

2、可选地,其中所述第一掺杂柱与所述第二掺杂柱具有大致相同的掺杂浓度。

3、可选地,其中所述源电极与所述漏电极之间的耐压大约为650v以上,850v以上,或者1200v以上,或者1500v以上。

4、可选地,进一步包括:第一掺杂层,其至少设置在第一掺杂柱和第二掺杂柱上方;第一掺杂区,设置在所述第一掺杂层内,与所述第二电极形成电连接;第二掺杂区,设置在所述第一掺杂层远离所述第一掺杂区的一侧。

5、可选地,进一步包括:第三掺杂柱,其为p-型掺杂,所述第三掺杂柱和所述第二掺杂柱相邻并位于所述第二掺杂柱的另一侧;第二掺杂层,其为p-型掺杂,设置在所述第三掺杂柱上方;第三掺杂区,设置在所述第一掺杂层内,与所述第二电极形成电连接。

6、可选地,进一步包括:第四掺杂柱,其为n-型掺杂,所述第四掺杂柱和所述第三掺杂柱相邻并位于所述第三掺杂柱的另一侧;第四掺杂区,设置在所述第四掺杂柱上方,位于所述第二掺杂层一侧;第二栅电极,设置在所述第二掺杂层上方,经配置以控制所述第三掺杂区和第四掺杂区之间的沟道。

7、可选地,进一步包括经第五掺杂区,其设置在所述第二掺杂柱和漏电极之间,所述间隔层为n型掺杂,其掺杂浓度大于所述第二掺杂柱的掺杂浓度。

8、本揭露还涉及一种超结器件的制造方法,包括:在基于垂直于衬底的界面的外延部分上再以外延生长形成第一掺杂区块,所述第一掺杂区块为p型掺杂;以外延生长方式在第一掺杂柱上形成第二掺杂区块,所述第二掺杂区块为n型掺杂;以所述第一掺杂区块和所述第二掺杂区块为基础,形成第一掺杂柱和第二掺杂柱,其中所述第一掺杂柱为p型掺杂,所述第二掺杂柱为n型掺杂,所述第二掺杂柱在所述第一掺杂柱一侧;形成第一电极;以及翻转所述第一掺杂柱、第二掺杂柱和第二电极,以外延生长方式在第一掺杂柱和第二掺杂柱上形成掺杂层;在掺杂层上形成第二电极,其中所述第一电极和第二电极分别在所述第一掺杂柱和第二掺杂柱的两侧;在掺杂层上形成栅电极,其经配置以控制所述第一源电极与所述第二掺杂柱之间的沟道。

9、可选地,其中,所述第一掺杂区块为p型掺杂,所述第二掺杂区块为n型掺杂,其中所述第一掺杂柱为p型掺杂,所述第二掺杂柱为n型掺杂;或者,所述第一掺杂区块为n型掺杂,所述第二掺杂区块为p型掺杂,其中所述第一掺杂柱为n型掺杂,所述第二掺杂柱为p型掺杂。

10、可选地,进一步包括:以外延生长方式在第二掺杂柱上形成第三掺杂区块,所述第三掺杂区块的掺杂类型与第一掺杂区块相同为p型掺杂;以及,以所述第三掺杂区块为基础,形成第三掺杂柱,其中所述第三掺杂柱的掺杂类型与第一掺杂柱相同为p型掺杂。

11、可选地,进一步包括:以外延生长方式在第三掺杂柱上形成第四掺杂区块,所述第四掺杂区块的掺杂类型与第二掺杂区块相同为n型掺杂;以及,以所述第四掺杂区块为基础,形成第四掺杂柱,其中所述第四掺杂柱的掺杂类型与第二掺杂柱相同为n型掺杂。

12、可选地,进一步包括:以所述垂直于衬底的界面为基础,以外延生长方式形成成核层和/或缓冲层。

技术特征:

1.一种iii-v族半导体超结器件,包括:

2.根据权利要求1所述的iii-v族半导体超结器件,其中所述第一掺杂柱与所述第二掺杂柱具有大致相同的掺杂浓度。

3.根据权利要求1所述的iii-v族半导体超结器件,其中所述源电极与所述漏电极之间的耐压大约为650v以上,850v以上,或者1200v以上,或者1500v以上。

4.根据权利要求1所述的iii-v族半导体超结器件,进一步包括:

5.根据权利要求4所述的iii-v族半导体超结器件,进一步包括:

6.根据权利要求5所述的iii-v族半导体超结器件,进一步包括:

7.根据权利要求1所述的iii-v族半导体超结器件,进一步包括经第五掺杂区,其设置在所述第二掺杂柱和第一电极之间,所述间隔层为n型掺杂,其掺杂浓度大于所述第二掺杂柱的掺杂浓度。

8.一种超结器件的制造方法,包括:

9.根据权利要求8所述的方法,其中,所述第一掺杂区块为p型掺杂,所述第二掺杂区块为n型掺杂,其中所述第一掺杂柱为p型掺杂,所述第二掺杂柱为n型掺杂;

10.根据权利要求8所述的方法,进一步包括:以外延生长方式在第二掺杂柱上形成第三掺杂区块,所述第三掺杂区块的掺杂类型与第一掺杂区块相同;以及,以所述第三掺杂区块为基础,形成第三掺杂柱,其中所述第三掺杂柱的掺杂类型与第一掺杂柱相同。

11.根据权利要求9所述的方法,进一步包括:以外延生长方式在第三掺杂柱上形成第四掺杂区块,所述第四掺杂区块的掺杂类型与第二掺杂区块相同;以及,以所述第四掺杂区块为基础,形成第四掺杂柱,其中所述第四掺杂柱的掺杂类型与第二掺杂柱相同。

12.根据权利要求1所述的方法,进一步包括:以所述垂直于衬底的界面为基础,以外延生长方式形成成核层和/或缓冲层。

技术总结

本发明涉及一种III‑V族半导体超结器件,包括:第一掺杂柱,其为P‑型掺杂;第二掺杂柱,其为N‑型掺杂,第二掺杂柱和第一掺杂柱相邻并位于第一掺杂柱的一侧;第一掺杂区,其为N‑型掺杂,设置在第一掺杂柱上方;第一电极,其设置在所述第一掺杂柱和所述第二掺杂柱下方,至少电耦合至所述第二掺杂柱;第二电极,其设置在所述第一掺杂柱上方,电耦合至所述第一掺杂柱;栅电极,其经配置以控制第一源电极与第二掺杂柱之间的沟道;其中,第一掺杂柱和第二掺杂柱为经掺杂的III‑V族半导体材料,第一掺杂柱、第二掺杂柱与第一源电极、栅电极及漏电极形成垂直超结结构,第一掺杂柱与第二掺杂柱具有大致相同的晶体质量。本申请进一步涉及一种超结器件的制造方法。

技术研发人员:陈龙,闫韶华,黎子兰

受保护的技术使用者:广东致能科技有限公司

技术研发日:

技术公布日:2024/6/13

- 还没有人留言评论。精彩留言会获得点赞!