一种堆叠纳米片环栅场效应晶体管及其制造方法

本申请涉及半导体领域,特别涉及一种堆叠纳米片环栅场效应晶体管及其制造方法。

背景技术:

1、随着集成电路特征尺寸持续微缩,传统三栅或双栅的鳍式场效应晶体管(finfield-effect transistor,finfet)在3nm以下节点受到限制,而与主流后高k金属栅finfet工艺兼容的纳米环栅晶体管(gate-all-around field-effect transistor,gaa-fet)将是实现尺寸微缩的下一代关键结构,gaa-fet的沟道主要为堆叠纳米片(stackednanosheet)结构。

2、在现有技术中,gaa-fet中具有包围沟道的功函数层(wfl),在工艺过程中,由于堆叠纳米片之间的空间限制,容易出现功函数层难以填充或者填充不均匀的现象,导致半导体器件的阈值电压难以精确调控,进而在实现器件多阈值集成时面临较大挑战。

技术实现思路

1、有鉴于此,本申请的目的在于提供一种堆叠纳米片环栅场效应晶体管及其制造方法,从而实现cmos器件多阈值与单种器件多阈值,以隔离层作为保护层,保护内侧的第一高k介质层不被损伤,本申请通过调整两层高k介质层的厚度,提高阈值电压调整的准确性和多样性。其具体方案如下:

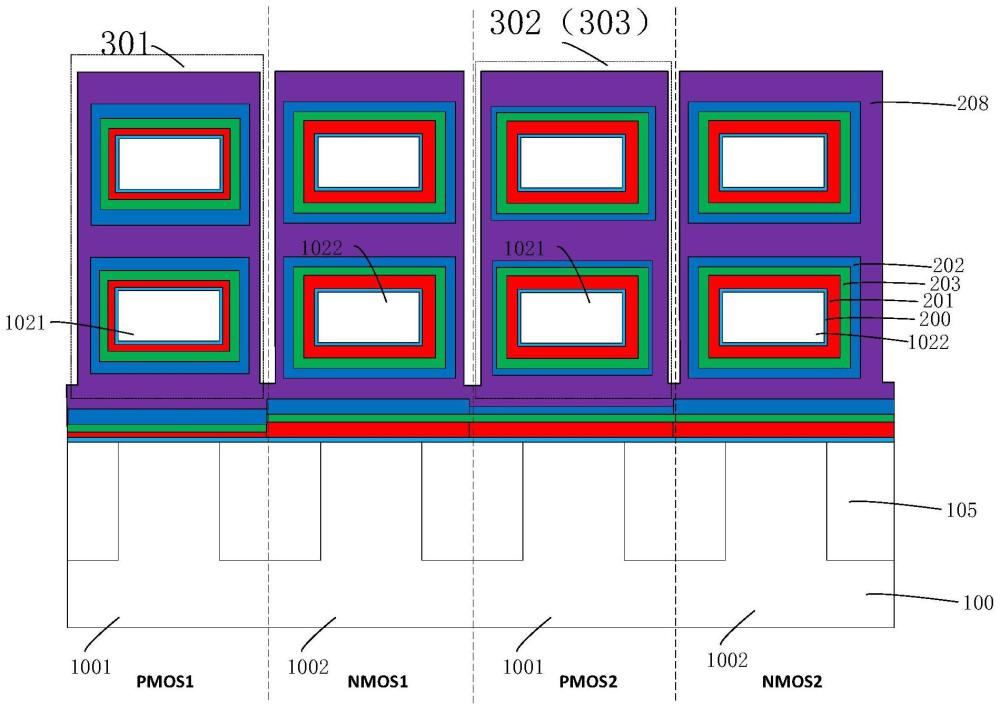

2、一方面,本申请提供了一种堆叠纳米片环栅场效应晶体管,包括:

3、衬底;所述衬底具有多个第一掺杂区域和多个第二掺杂区域,所述第一掺杂区域和所述第二掺杂区域的掺杂类型不同,所述掺杂类型为p型掺杂或n型掺杂,所述第一掺杂区域上方具有堆叠的多个第一半导体层,所述第二掺杂区域上方具有堆叠的多个第二半导体层;

4、在所述多个第一半导体层之间,具有依次包围所述第一半导体层的界面氧化层、第一高k介质层、隔离层、第二高k介质层和金属栅,在所述多个第二半导体层之间,具有依次包围所述第二半导体层的界面氧化层、第一高k介质层、隔离层、第二高k介质层和金属栅;所述第一高k介质层的静电偶极子的方向,与所述第二高k介质层的静电偶极子的方向相反;

5、位于第一目标区域内的第一高k介质层的第一厚度,与位于第二目标区域内的第一高k介质层的第二厚度不同,位于所述第一目标区域内的第二高k介质层的第三厚度,与位于第三目标区域内的第二高k介质层的第四厚度不同;所述第一目标区域、所述第二目标区域或所述第三目标区域为所述第一掺杂区域的上方或所述第二掺杂区域的上方。

6、又一方面,本申请实施例还提供了一种堆叠纳米片环栅场效应晶体管的制备方法,所述方法包括:

7、提供衬底;所述衬底具有多个第一掺杂区域和多个第二掺杂区域,所述第一掺杂区域和所述第二掺杂区域的掺杂类型不同,所述掺杂类型为p型掺杂或n型掺杂,所述第一掺杂区域上方具有堆叠的多个第一半导体层,所述第二掺杂区域上方具有堆叠的多个第二半导体层;

8、在所述多个第一半导体层之间和所述多个第二半导体层之间,同时形成依次包围所述第一半导体层的界面氧化层和第一高k介质层,以及依次包围所述第二半导体层的界面氧化层和第一高k介质层;

9、对位于第一目标区域内的第一高k介质层进行减薄处理,以使位于第一目标区域内的第一高k介质层的第一厚度,与位于第二目标区域的第一高k介质层的第二厚度不同;

10、形成依次包围所述第一半导体层的隔离层,以及依次包围所述第二半导体层的隔离层;

11、形成包围所述第一半导体层的第二高k介质层,以及包围所述第二半导体层的第二高k介质层;所述第一高k介质层的静电偶极子的方向,与所述第二高k介质层的静电偶极子的方向相反;

12、对位于第三目标区域内的第二高k介质层进行减薄处理,以使位于所述第一目标区域内的第二高k介质层的第三厚度,与位于第三目标区域内的第二高k介质层的第四厚度不同;所述第一目标区域、所述第二目标区域或所述第三目标区域为所述第一掺杂区域的上方或所述第二掺杂区域的上方;

13、形成包围所述第一半导体层的金属栅,以及包围所述第二半导体层的金属栅。

14、本申请实施例提供了一种堆叠纳米片环栅场效应晶体管及其制造方法,在本申请中第一高k介质层和第二高k介质层中的静电偶极子方向相反,即两层高k介质层中的静电电场强度的方向相反,且由于位于不同目标区域的第一高k介质层的厚度不同,这样,可以通过改变第一高k介质层的厚度,能够改变第一高k介质层中的静电电场强度的大小,位于不同目标区域的第二高k介质层的厚度也不相同,可以调整第二高k介质层中的静电电场强度的大小,进而在第一高k介质层的静电电场强度和第二高k介质层中的静电电场强度进行叠加时,能够调整叠加后的总静电电场强度,两层高k介质层中的静电电场强度都可以通过改变厚度进行调整,从而可以更加精确的调整器件的阈值电压。这样,对于同一种器件比如nmos器件或pmos器件能够实现多种阈值电压的集成,能够根据实际需求精确的调整单个器件的阈值电压,进而对于cmos器件也可以实现多种阈值电压的集成,从而实现cmos器件多阈值与单种器件多阈值,提高器件多阈值集成的准确度。另外,为了避免在对第二高k介质层进行减薄处理时损伤第一高k介质层,可以在二者之间形成隔离层,以隔离层作为保护层,保护内侧的第一高k介质层不被损伤,本申请能够通过调整两层高k介质层的厚度,提高阈值电压调整的准确性和多样性。

技术特征:

1.一种堆叠纳米片环栅场效应晶体管,其特征在于,包括:

2.根据权利要求1所述的堆叠纳米片环栅场效应晶体管,其特征在于,所述第二目标区域和所述第三目标区域为同一区域,所述第一目标区域和所述第二目标区域都位于第一掺杂区域的上方,或,所述第一目标区域和所述第二目标区域都位于第二掺杂区域的上方。

3.根据权利要求1或2所述的堆叠纳米片环栅场效应晶体管,其特征在于,所述第一高k介质层为第一类介质,所述第一类介质为laox、mgox、scox、yox、ndox、tbox和dyox中的至少一种,所述第二高k介质层为第二类介质,所述第二类介质为alox、mnox、zrox、tiox和moox中的至少一种。

4.根据权利要求1或2所述的堆叠纳米片环栅场效应晶体管,其特征在于,所述第一高k介质层为第二类介质,所述第二类介质为alox、mnox、zrox、tiox和moox中的至少一种,所述第二高k介质层为第一类介质,所述第一类介质为laox、mgox、scox、yox、ndox、tbox和dyox中的至少一种。

5.根据权利要求1所述的堆叠纳米片环栅场效应晶体管,其特征在于,所述第一高k介质层、所述第二高k介质层或所述隔离层的厚度大于或等于0.1nm,且小于或等于5nm。

6.一种堆叠纳米片环栅场效应晶体管的制备方法,其特征在于,所述方法包括:

7.根据权利要求6所述的方法,其特征在于,所述对位于第一目标区域内的第一高k介质层进行减薄处理,包括:

8.根据权利要求7所述的方法,其特征在于,所述第一介质腐蚀液为去离子水、酸性溶液或碱性溶液,所述第二介质腐蚀液为去离子水、酸性溶液或碱性溶液。

9.根据权利要求8所述的方法,其特征在于,所述第一介质腐蚀液或所述第二介质腐蚀液的溶质浓度大于或等于0.0001%,且小于100%。

10.根据权利要求6所述的方法,其特征在于,所述第一高k介质层为第一类介质或第二类介质中的一种,所述第二高k介质层为所述第一类介质或所述第二类介质中的另一种;所述第一类介质为laox、mgox、scox、yox、ndox、tbox和dyox中的至少一种,所述第二类介质为alox、mnox、zrox、tiox和moox中的至少一种。

技术总结

本申请提供一种堆叠纳米片环栅场效应晶体管及其制造方法,衬底具有多个第一掺杂区域和多个第二掺杂区域,在多个第一半导体层之间以及多个第二半导体层之间,具有依次包围的界面氧化层、第一高k介质层、隔离层、第二高k介质层和金属栅,位于第一目标区域内的第一高k介质层的第一厚度,与位于第二目标区域内的第一高k介质层的第二厚度不同,位于第一目标区域内的第二高k介质层的第三厚度,与位于第三目标区域内的第二高k介质层的第四厚度不同。从而实现CMOS器件多阈值与单种器件多阈值,以隔离层作为保护层,保护内侧的第一高k介质层不被损伤,本申请通过调整两层高k介质层的厚度,提高阈值电压调整的准确性和多样性。

技术研发人员:姚佳欣,魏延钊,王宇,张青竹,殷华湘

受保护的技术使用者:中国科学院微电子研究所

技术研发日:

技术公布日:2024/7/18

- 还没有人留言评论。精彩留言会获得点赞!