半导体装置的制作方法

本发明的实施方式涉及一种半导体装置及其制造方法。

背景技术:

1、当在衬底上方的较高的位置配置存储单元阵列的情况下,存在难以将衬底上的元件与存储单元阵列内的电极层连接的情况。

技术实现思路

1、实施方式提供一种能够容易地将衬底上的元件与存储单元阵列内的电极层连接的半导体装置及其制造方法。

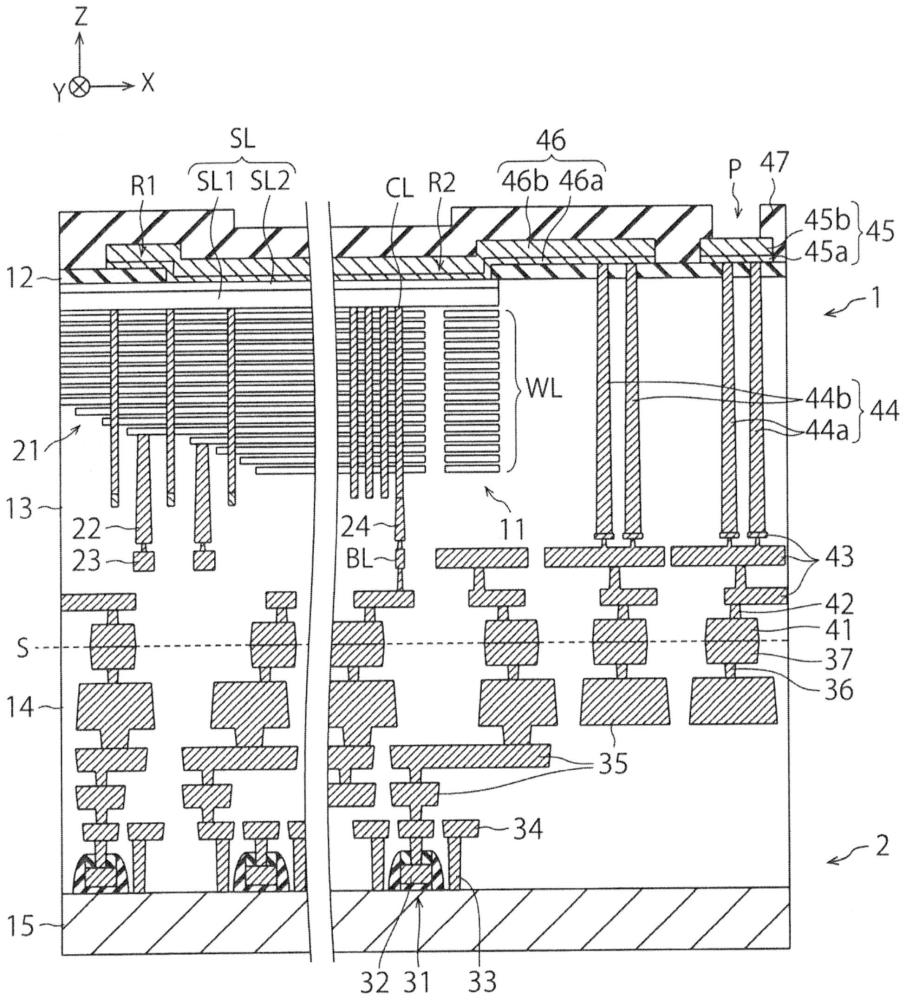

2、根据实施方式,半导体装置具备:第1衬底;逻辑电路,设置于所述第1衬底上;及存储单元阵列,设置于所述逻辑电路上方,且包含被积层的多个电极层、及设置于所述多个电极层上方的半导体层。所述装置还具备:第1及第2插塞,设置于所述逻辑电路的上方,且电连接于所述逻辑电路;焊盘,设置于所述第1插塞上;及金属配线层,设置于所述存储单元阵列上,电连接于所述半导体层,且电连接于所述第2插塞。

技术特征:

1.一种半导体装置,具备:

2.根据权利要求1所述的半导体装置,还具备:

3.根据权利要求2所述的半导体装置,其中所述第1及第2插塞在所述存储单元阵列的外部设置于所述存储单元阵列的侧方。

4.根据权利要求1或2所述的半导体装置,其中所述半导体层包含于源极线,所述金属配线层包含于源极配线层。

5.根据权利要求1或2所述的半导体装置,其中所述金属配线层设置于所述半导体层上。

6.根据权利要求5所述的半导体装置,其中所述金属配线层设置于所述半导体层的上表面及侧面。

7.根据权利要求1或2所述的半导体装置,其中所述金属配线层设置于所述半导体层上及所述第1插塞上。

8.根据权利要求1或2所述的半导体装置,其中

9.根据权利要求1或2所述的半导体装置,还具备:

10.根据权利要求2所述的半导体装置,具备

11.根据权利要求1所述的半导体装置,其中

12.一种半导体装置,具备:

13.根据权利要求12所述的半导体装置,还具备:

14.根据权利要求13所述的半导体装置,其中所述第1及第2插塞在所述存储单元阵列的外部设置于所述存储单元阵列的侧方。

15.根据权利要求12或13所述的半导体装置,其中所述半导体层包含于源极线,所述金属配线层包含于源极配线层。

16.根据权利要求12或13所述的半导体装置,其中所述金属配线层设置于所述半导体层上。

17.根据权利要求16所述的半导体装置,其中所述金属配线层设置于所述半导体层的上表面及侧面。

18.根据权利要求12或13所述的半导体装置,其中所述金属配线层设置于所述半导体层上及所述第1插塞上。

19.根据权利要求12或13所述的半导体装置,其中

20.根据权利要求13所述的半导体装置,具备:

21.根据权利要求12所述的半导体装置,具备

22.根据权利要求12所述的半导体装置,其中

23.一种半导体装置,具备:

24.根据权利要求23所述的半导体装置,还具备:

25.根据权利要求23或24所述的半导体装置,其中

26.根据权利要求23或24所述的半导体装置,其中

27.根据权利要求23所述的半导体装置,还具备:

28.根据权利要求27所述的半导体装置,其中所述第1及第2插塞在所述存储单元阵列的外部设置于所述存储单元阵列的侧方。

29.根据权利要求27所述的半导体装置,具备:

30.根据权利要求23所述的半导体装置,其中所述金属配线层设置于所述半导体层的上表面及侧面。

31.根据权利要求23或24所述的半导体装置,其中所述金属配线层设置于所述半导体层上及所述第1插塞上。

32.根据权利要求23或24所述的半导体装置,其中

33.根据权利要求23所述的半导体装置,其中

34.一种半导体装置,具备:

35.根据权利要求34所述的半导体装置,其中

36.根据权利要求34所述的半导体装置,其中

37.根据权利要求34所述的半导体装置,还具备:

38.根据权利要求37所述的半导体装置,其中所述第1及所述第2插塞在所述存储单元阵列的外部设置于所述存储单元阵列的侧方。

39.根据权利要求34所述的半导体装置,其中所述金属配线层设置于所述源极线的上表面及侧面。

40.根据权利要求34所述的半导体装置,其中所述第2部分与所述第1部分连续地设置。

技术总结

本发明的实施方式提供一种能够容易地将衬底上的元件与存储单元阵列内的电极层连接的半导体装置。根据实施方式,半导体装置具备:第1衬底;逻辑电路,设置于所述第1衬底上;及存储单元阵列,设置于所述逻辑电路的上方,且包含被积层的多个电极层及设置于所述多个电极层上方的半导体层。所述装置还具备:第1及第2插塞,设置于所述逻辑电路的上方,且电连接于所述逻辑电路;焊盘,设置于所述第1插塞上;及金属配线层,设置于所述存储单元阵列上,电连接于所述半导体层,且电连接于所述第2插塞。

技术研发人员:内山泰宏

受保护的技术使用者:铠侠股份有限公司

技术研发日:

技术公布日:2024/7/29

- 还没有人留言评论。精彩留言会获得点赞!