一种环栅晶体管的制造方法

本发明涉及半导体,尤其涉及一种环栅晶体管的制造方法。

背景技术:

1、随着半导体技术的发展,环栅晶体管应时而生。因环栅晶体管具有的栅堆叠结构不仅形成在沟道区的顶部和侧壁上、还形成在沟道区的底部,故与平面晶体管和鳍式场效应晶体管相比,环栅晶体管具有较强的栅控能力,利于抑制短沟道效应。另外,与硅材料相比,含锗半导体材料具有较高的载流子迁移率,因此当采用含锗半导体材料制造环栅晶体管包括的沟道区时,利于提高环栅晶体管包括的沟道区的导通特性。

2、但是,采用现有的制造方法所形成的上述环栅晶体管的良率较低,不利于提高环栅晶体管的工作性能。

技术实现思路

1、本发明的目的在于提供一种环栅晶体管的制造方法,用于在环栅晶体管包括的纳米结构的材料含有锗的情况下,提高环栅晶体管的良率,利于提升环栅晶体管的工作性能。

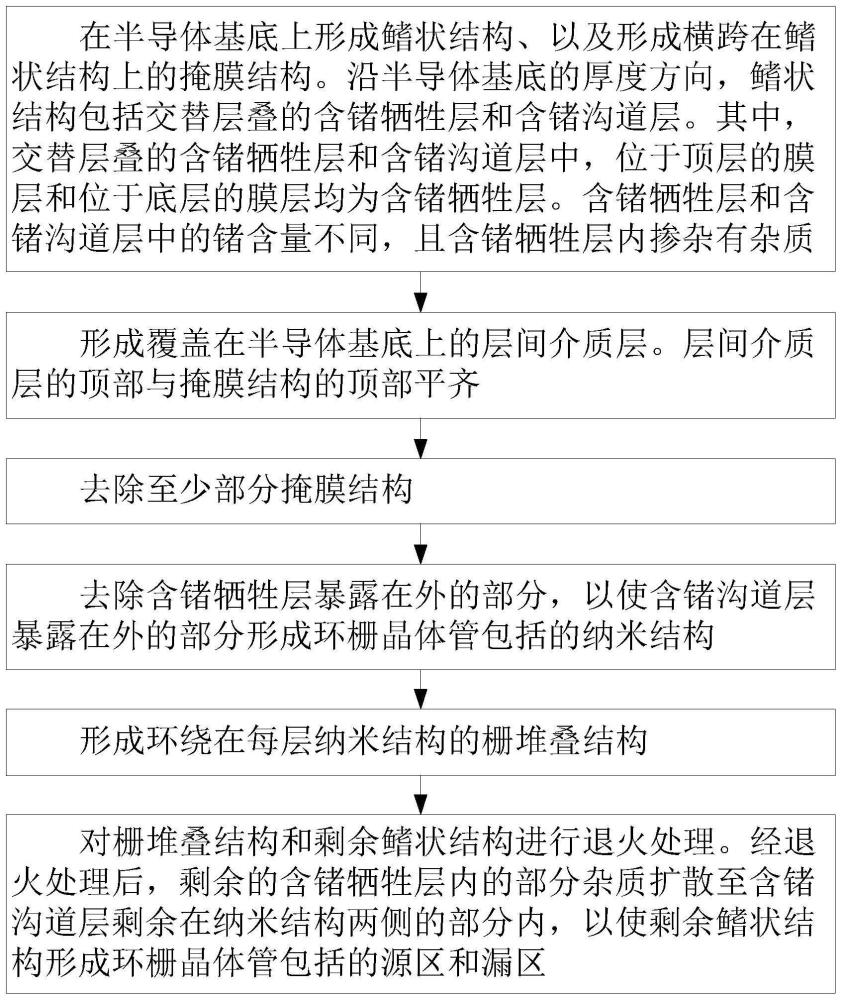

2、为了实现上述目的,本发明提供了一种环栅晶体管的制造方法,该环栅晶体管的制造方法包括:首先,在半导体基底上形成鳍状结构、以及形成横跨在鳍状结构上的掩膜结构。沿半导体基底的厚度方向,鳍状结构包括交替层叠的含锗牺牲层和含锗沟道层。其中,交替层叠的含锗牺牲层和含锗沟道层中,位于顶层的膜层和位于底层的膜层均为含锗牺牲层。含锗牺牲层和含锗沟道层中的锗含量不同,且含锗牺牲层内掺杂有杂质。接下来,形成覆盖在半导体基底上的层间介质层。层间介质层的顶部与掩膜结构的顶部平齐。接下来,去除至少部分掩膜结构。接下来,去除含锗牺牲层暴露在外的部分,以使含锗沟道层暴露在外的部分形成环栅晶体管包括的纳米结构。接下来,形成环绕在每层纳米结构的栅堆叠结构。然后,对栅堆叠结构和剩余鳍状结构进行退火处理。经退火处理后,剩余的含锗牺牲层内的部分杂质扩散至含锗沟道层剩余在纳米结构两侧的部分内,以使剩余鳍状结构形成环栅晶体管包括的源区和漏区。

3、采用上述技术方案的情况下,在半导体基底上形成的鳍状结构包括交替层叠的含锗牺牲层和含锗沟道层。该含锗沟道层被掩膜结构覆盖的部分用于制造环栅晶体管包括的纳米结构,此时纳米结构内也含有锗元素。因与硅材料相比,含锗的半导体材料具有更高的载流子迁移率,故在纳米结构内含有锗元素的情况下,利于提升纳米结构的导通特性,提高环栅晶体管的电学性能。

4、其次,在形成横跨在鳍状结构上的掩膜结构的过程中,因鳍状结构中位于顶层的膜层为含锗牺牲层,该含锗牺牲层并非用于制造纳米结构的膜层,因此可以通过位于顶层的含锗牺牲层对位于自身下方的含锗沟道层进行保护,防止刻蚀形成掩膜结构的刻蚀剂对含锗沟道层造成影响,提高纳米结构的形成质量。另外,在形成了覆盖在半导体基底上的层间介质层后,在去除至少部分掩膜结构、以及去除含锗牺牲层暴露在外的部分并形成纳米结构的过程中,层间介质层的存在可以保护位于纳米结构两侧的剩余鳍状结构不受刻蚀和清洗等操作的影响。再者,本发明提供的制造方法是在形成栅堆叠结构后,对栅堆叠结构进行退火处理的同时,对剩余鳍状结构进行退火处理。经退火处理后,剩余的含锗牺牲层内的部分杂质扩散至含锗沟道层剩余在纳米结构两侧的部分内,以在使剩余鳍状结构形成环栅晶体管包括的源区和漏区,提高环栅晶体管制造效率、简化环栅晶体管的制造流程的同时,因与纳米结构接触、且暴露在层间介质层外的含锗牺牲层已被去除掉,故在退火处理时剩余的含锗牺牲层内的部分杂质仅会扩散至含锗沟道层剩余在纳米结构两侧的部分内,而不会扩散到纳米结构内,并且也不会导致纳米结构内的锗元素受热扩散,确保纳米结构具有较高的形成质量,进一步提高环栅晶体管的工作性能。

5、在一种示例中,上述含锗牺牲层内杂质的掺杂浓度大于等于5e19cm-3、且小于等于3e20cm-3。

6、在一种示例中,上述含锗沟道层为本征含锗沟道层。

7、在一种示例中,上述含锗沟道层内掺杂有杂质,且含锗沟道层和含锗牺牲层的导电类型相反。含锗沟道层内的杂质掺杂浓度小于含锗牺牲层内的杂质掺杂浓度。

8、在一种示例中,在含锗沟道层内掺杂有杂质的情况下,含锗沟道层内的杂质掺杂浓度大于0、且小于等于1e18cm-3。

9、在一种示例中,上述含锗沟道层内的锗含量小于含锗牺牲层内的锗含量。

10、在一种示例中,上述含锗沟道层内的锗含量与含锗牺牲层内的锗含量的差值大于等于20%、且小于等于50%。

11、在一种示例中,上述含锗沟道层内的锗含量大于等于50%、且小于等于80%。

12、在一种示例中,上述含锗牺牲层内的锗含量大于等于70%、且小于等于100%。

13、在一种示例中,上述交替层叠的含锗牺牲层和含锗沟道层中,位于顶层的含锗牺牲层的厚度大于其余层含锗牺牲层的厚度。

14、在一种示例中,上述交替层叠的含锗牺牲层和含锗沟道层中,位于顶层的含锗牺牲层的厚度大于等于20nm、且小于等于40nm。

15、在一种示例中,沿半导体基底的厚度方向,半导体基底靠近鳍状结构的部分内掺杂有与含锗牺牲层内杂质导电类型相反的杂质,半导体基底靠近鳍状结构的部分内杂质的掺杂浓度大于等于1e18 cm-3、且小于等于7e18cm-3。

16、在一种示例中,上述半导体基底包括半导体衬底、以及形成在半导体基底上的含锗应变缓冲层。含锗应变缓冲层内的锗含量大于等于50%、且小于等于100%。

17、在一种示例中,上述含锗应变缓冲层包括沿半导体基底的厚度方向交替层叠的第一含锗应变缓冲子层和第二含锗应变缓冲子层。其中,

18、第一含锗应变缓冲子层和第二含锗应变缓冲子层的形成温度和/或锗含量不同。

19、在一种示例中,上述掩膜结构包括牺牲栅、以及至少位于牺牲栅沿自身长度方向两侧的栅极侧墙。并且,上述去除至少部分掩膜结构,包括:去除牺牲栅。

技术特征:

1.一种环栅晶体管的制造方法,其特征在于,包括:

2.根据权利要求1所述的环栅晶体管的制造方法,其特征在于,所述含锗牺牲层内杂质的掺杂浓度大于等于5e19cm-3、且小于等于3e20cm-3。

3.根据权利要求1所述的环栅晶体管的制造方法,其特征在于,所述含锗沟道层为本征含锗沟道层;或,

4.根据权利要求3所述的环栅晶体管的制造方法,其特征在于,在所述含锗沟道层内掺杂有杂质的情况下,所述含锗沟道层内的杂质掺杂浓度大于0、且小于等于1e18cm-3。

5.根据权利要求1所述的环栅晶体管的制造方法,其特征在于,所述含锗沟道层内的锗含量小于所述含锗牺牲层内的锗含量;和/或,

6.根据权利要求1所述的环栅晶体管的制造方法,其特征在于,所述交替层叠的含锗牺牲层和所述含锗沟道层中,位于顶层的所述含锗牺牲层的厚度大于其余层所述含锗牺牲层的厚度;和/或,

7.根据权利要求1所述的环栅晶体管的制造方法,其特征在于,沿所述半导体基底的厚度方向,所述半导体基底靠近所述鳍状结构的部分内掺杂有与所述含锗牺牲层内杂质导电类型相反的杂质,所述半导体基底靠近所述鳍状结构的部分内杂质的掺杂浓度大于等于1e18 cm-3、且小于等于7e18cm-3。

8.根据权利要求1所述的环栅晶体管的制造方法,其特征在于,所述半导体基底包括半导体衬底、以及形成在所述半导体基底上的含锗应变缓冲层;所述含锗应变缓冲层内的锗含量大于等于50%、且小于等于100%。

9.根据权利要求8所述的环栅晶体管的制造方法,其特征在于,所述含锗应变缓冲层包括沿所述半导体基底的厚度方向交替层叠的第一含锗应变缓冲子层和第二含锗应变缓冲子层;其中,

10.根据权利要求1~9任一项所述的环栅晶体管的制造方法,其特征在于,所述掩膜结构包括牺牲栅、以及至少位于所述牺牲栅沿自身长度方向两侧的栅极侧墙;

技术总结

本发明公开一种环栅晶体管的制造方法,涉及半导体技术领域,以在环栅晶体管包括的纳米结构的材料含有锗的情况下,提高环栅晶体管的良率。所述环栅晶体管的制造方法包括:在半导体基底上形成鳍状结构、以及形成横跨在鳍状结构上的掩膜结构。接下来,形成覆盖在半导体基底上的层间介质层。去除至少部分掩膜结构。去除含锗牺牲层暴露在外的部分,以使含锗沟道层暴露在外的部分形成环栅晶体管包括的纳米结构。接下来,形成环绕在每层纳米结构的栅堆叠结构。然后,对栅堆叠结构和剩余鳍状结构进行退火处理。经退火处理后,剩余的含锗牺牲层内的部分杂质扩散至含锗沟道层剩余在纳米结构两侧的部分内,以使剩余鳍状结构形成环栅晶体管包括的源区和漏区。

技术研发人员:李永亮,刘昊炎,张曦,罗军

受保护的技术使用者:中国科学院微电子研究所

技术研发日:

技术公布日:2024/8/21

- 还没有人留言评论。精彩留言会获得点赞!