一种嵌入式肖特基MOSFET制作方法与流程

本发明涉及半导体制造,具体涉及一种嵌入式肖特基mosfet制作方法。

背景技术:

1、传统屏蔽栅器件,反向恢复从体二极管漏端走到源端。通过并联肖特基二极管(schottky barrier diode,简称sbd)方式,有效降低寄生管开启电压,从而降低恢复速度,提高转换效率。如图1所示,mos器件m1和m2作为核心开关器件,通过控制芯片来实现直流-直流转换,其中,m1和m2种本身存在寄生二极管d1、d2(由包围源极的阱区/漏极构成),为有效降低高频开关损耗,提高直流转化效率,在m1的源极s与漏极d之间并联肖特基二极管sbd(如图2所示)。由于肖特基二极管sbd与寄生二极管d1(pn结)相比,具有更低的开启电压(肖特基二极管0.3v左右,pn结二极管0.7v左右),如在m1的源极s与漏极d之间并联一肖特基二极管sbd,可以有效减少由于高开启电压造成的损耗,有效降低高频开关过程种开关损耗,提高转换效率。

2、现有嵌入式肖特基的形成工艺分为两种:如图3和图4所示,第一种是阱注入,第二种是深接触孔挖穿阱区。但这两种方法都有不足之处,第一种需额外光刻掩模,而且受器件尺寸限制,第二种接触孔到外延距离较深,降低了击穿电压。

技术实现思路

1、有鉴于此,本发明提供一种嵌入式肖特基mosfet制作方法,用以改善现有肖特基嵌入工艺。

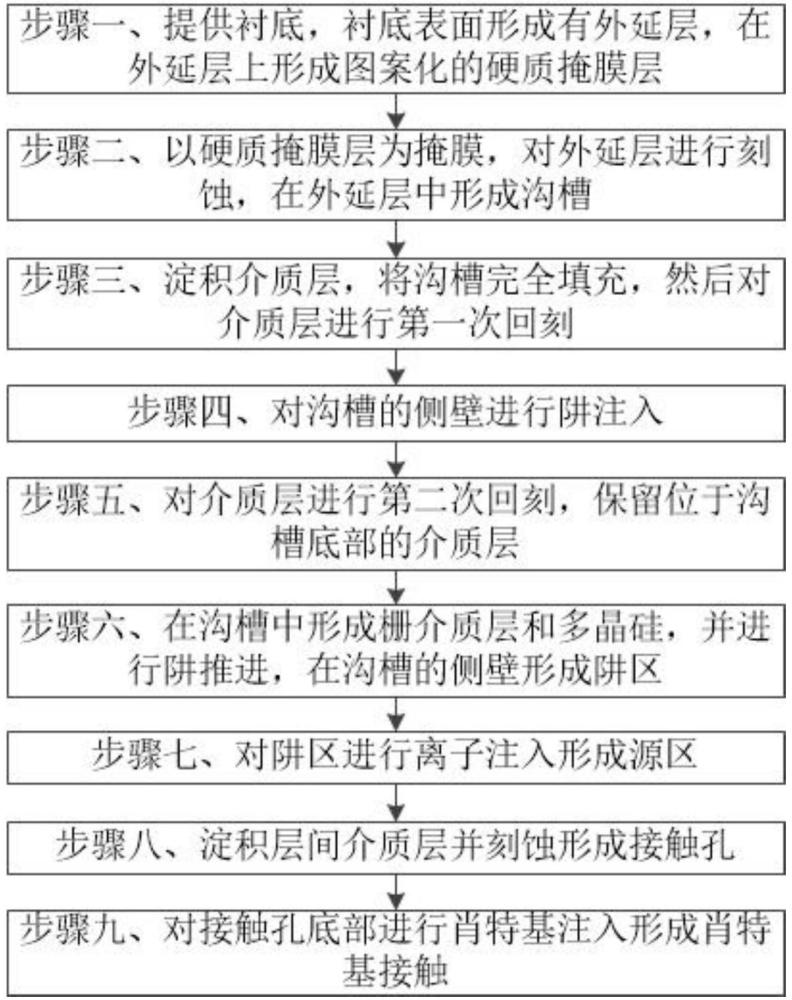

2、本发明提供一种嵌入式肖特基mosfet制作方法,包括以下步骤:

3、步骤一、提供衬底,所述衬底表面形成有外延层,在所述外延层上形成图案化的硬质掩膜层;

4、步骤二、以所述硬质掩膜层为掩膜,对所述外延层进行刻蚀,在所述外延层中形成沟槽;

5、步骤三、淀积介质层,将所述沟槽完全填充,然后对所述介质层进行第一次回刻;

6、步骤四、对所述沟槽的侧壁进行阱注入;

7、步骤五、对所述介质层进行第二次回刻,保留位于所述沟槽底部的所述介质层;

8、步骤六、在所述沟槽中形成栅介质层和多晶硅,并进行阱推进,在所述沟槽的侧壁形成阱区;

9、步骤七、对所述阱区进行离子注入形成源区;

10、步骤八、淀积层间介质层并刻蚀形成接触孔;

11、步骤九、对所述接触孔底部进行肖特基注入形成肖特基接触。

12、优选地,步骤一中所述衬底为硅衬底。

13、优选地,步骤一中所述硬质掩膜层的材料为氮化硅。

14、优选地,步骤二和步骤四中所述刻蚀为干法刻蚀工艺。

15、优选地,步骤三中所述介质层为氧化层。

16、优选地,步骤五中所述栅介质层形成于所述沟槽的底部表面和侧面。

17、优选地,步骤五中所述多晶硅将所述沟槽完全填充。

18、优选地,步骤五中还包括去除所述硬质掩膜层。

19、优选地,步骤七中所述接触孔的深度不超过所述阱区。

20、本发明采用沟槽内介质层填充后分步回刻,分别实现仅在沟槽侧壁阱区的接触孔肖特基结构和底部厚氧化层结构,提升开关速度的同时提升恢复速度,实现方法简易且可操作性强,并且无需额外双阱阻挡光刻版,达到了改善现有肖特基嵌入工艺的目的。

技术特征:

1.一种嵌入式肖特基mosfet制作方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的嵌入式肖特基mosfet制作方法,其特征在于,步骤一中所述衬底为硅衬底。

3.根据权利要求1所述的嵌入式肖特基mosfet制作方法,其特征在于,步骤一中所述硬质掩膜层的材料为氮化硅。

4.根据权利要求1所述的嵌入式肖特基mosfet制作方法,其特征在于,步骤二中所述刻蚀为干法刻蚀工艺。

5.根据权利要求1所述的嵌入式肖特基mosfet制作方法,其特征在于,步骤三中所述介质层为氧化层。

6.根据权利要求1所述的嵌入式肖特基mosfet制作方法,其特征在于,步骤六中所述栅介质层形成于所述沟槽的底部表面和侧面。

7.根据权利要求1所述的嵌入式肖特基mosfet制作方法,其特征在于,步骤六中所述多晶硅将所述沟槽完全填充。

8.根据权利要求1所述的嵌入式肖特基mosfet制作方法,其特征在于,步骤六还包括去除所述硬质掩膜层。

9.根据权利要求1所述的嵌入式肖特基mosfet制作方法,其特征在于,步骤八中所述接触孔的深度不超过所述阱区。

技术总结

本发明提供一种嵌入式肖特基MOSFET制作方法,包括提供衬底,衬底表面形成有外延层,在外延层上形成图案化的硬质掩膜层;以硬质掩膜层为掩膜,对外延层进行刻蚀,在外延层中形成沟槽;淀积介质层,将沟槽完全填充,然后对介质层进行第一次回刻;对沟槽的侧壁进行阱注入;对介质层进行第二次回刻,保留位于沟槽底部的介质层;在沟槽中形成栅介质层和多晶硅,并进行阱推进,在沟槽的侧壁形成阱区;对阱区进行离子注入形成源区;淀积层间介质层并刻蚀形成接触孔;对接触孔底部进行肖特基注入形成肖特基接触。本发明采用沟槽内介质层填充后分步回刻,分别实现仅在沟槽侧壁阱区的接触孔肖特基结构和底部厚氧化层结构,提升开关速度的同时提升恢复速度。

技术研发人员:颜树范,张鑫,胡瑞华

受保护的技术使用者:上海华虹宏力半导体制造有限公司

技术研发日:

技术公布日:2024/9/5

- 还没有人留言评论。精彩留言会获得点赞!