ESD防护器件的制作方法

本申请涉及半导体制造,具体涉及一种esd防护器件。

背景技术:

1、先进集成电路,会引入金属硅化物工艺,这对esd保护来说不是有利选项。常用的mos结构,当作为i/o器件或者电源保护器件时,会在漏端增加一道sab(金属硅化物阻挡)工艺,通常是淀积金属硅化物阻挡材料层,防止金属硅化物的形成。其中,金属硅化物阻挡材料层主要起镇流电阻作用,为充分发挥mos器件的esd性能,sab层(金属硅化物阻挡材料层)的宽度会增加到2μm甚至更高,导致mos器件的尺寸面积增加明显。尤其是当i/o端口较多时,所有的i/o端口均对应需要sab层来防止金属硅化物的形成,这更是会增大芯片的设计面积。

技术实现思路

1、本申请提供了一种esd防护器件,可以解决目前esd防护器件中的覆盖漏端部分表面的金属硅化物阻挡材料层所占面积较大的问题。

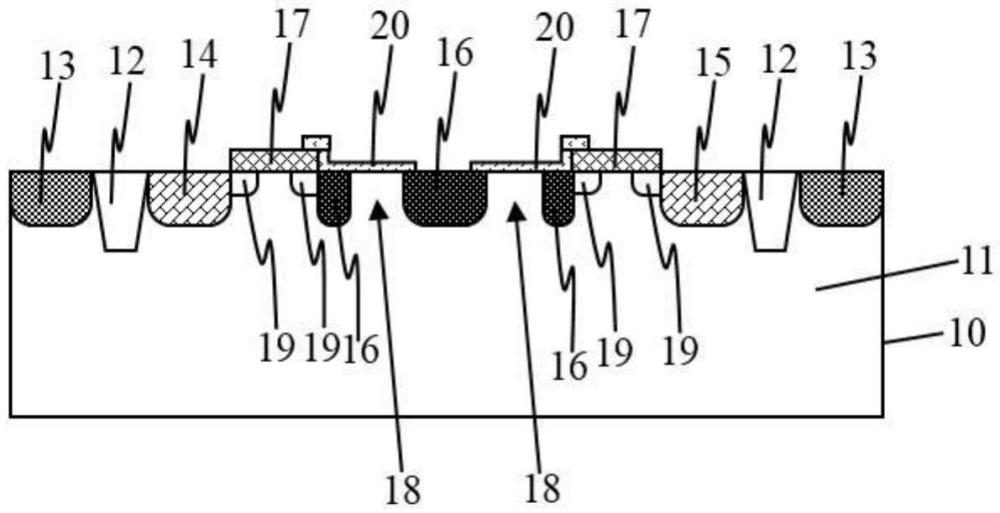

2、本申请实施例提供了一种esd防护器件,包括:衬底、阱区、呈环状的浅沟槽隔离结构、呈环状的衬底引出端和mos单元,其中,

3、所述mos单元包括:栅端多晶硅层、两个源端重掺杂区、一个漏端重掺杂区、金属硅化物阻挡层,其中,

4、所述阱区位于所述衬底中,所述衬底引出端位于所述阱区中且环绕所述mos单元设置;所述浅沟槽隔离结构位于所述衬底引出端和mos单元之间的阱区中,所述源端重掺杂区和所述漏端重掺杂区间隔设置于所述阱区中并且两个源端重掺杂区位于所述漏端重掺杂区两相对侧,所述栅端多晶硅层覆盖所述源端重掺杂区和所述漏端重掺杂区之间的阱区表面,所述金属硅化物阻挡层覆盖所述漏端重掺杂区和所述栅端多晶硅层构成的台阶表面;

5、所述漏端重掺杂区中形成有若干未重掺杂块,所述未重掺杂块按i行j列形式排布于所述金属硅化物阻挡层底部的漏端重掺杂区中,其中,i为大于或者等于2的整数,j为2。

6、可选的,在所述esd防护器件中,同一行中,两列所述未重掺杂块基于所述漏端重掺杂区的中心位置对称。

7、可选的,在所述esd防护器件中,所述mos单元还包括:若干块状隔离结构,所述块状隔离结构填充所述未重掺杂块所在的位置。

8、可选的,在所述esd防护器件中,所述块状隔离结构的材质为二氧化硅。

9、可选的,在所述esd防护器件中,所述mos单元还包括:多个轻掺杂漏区,所述轻掺杂漏区分别位于所述源端重掺杂区侧以及所述漏端重掺杂区侧并且延伸至所述栅端多晶硅层底部。

10、可选的,在所述esd防护器件中,所述esd防护器件还包括:第一至第四导电插塞,第一导电插塞连接所述栅端多晶硅层,第二导电插塞连接所述源端重掺杂区,第三导电插塞连接所述漏端重掺杂区,第四导电插塞连接所述衬底引出端。

11、可选的,在所述esd防护器件中,所述阱区中掺杂离子的导电类型为p型,所述衬底引出端中掺杂离子的导电类型为p型,所述源端重掺杂区中掺杂离子的导电类型为n型,所述漏端重掺杂区中掺杂离子的导电类型为n型。

12、可选的,在所述esd防护器件中,所述阱区中掺杂离子的导电类型为n型,所述衬底引出端中掺杂离子的导电类型为n型,所述源端重掺杂区中掺杂离子的导电类型为p型,所述漏端重掺杂区中掺杂离子的导电类型为p型。

13、可选的,在所述esd防护器件中,在所述esd防护器件工作时,所述栅端多晶硅层、源端重掺杂区和所述衬底引出端均连接低电平,漏端重掺杂区连接高电平。

14、本申请技术方案,至少包括如下优点:

15、本申请在漏端重掺杂区的有源区中,设置阵列排布的未重掺杂块,以使未重掺杂块和漏端有源区交替排列,使得每行mos结构中的esd电流仅能从两个未重掺杂块之间流过,减少了漏端有源区面积,增大了整流电阻,从而可以缩减金属硅化物阻挡层覆盖漏端重掺杂区的横向尺寸,在不增加任何成本的情况下缩小器件整体面积,提高了芯片的集成度,同时也可以减小mos器件的导通电阻。

技术特征:

1.一种esd防护器件,其特征在于,包括:衬底、阱区、呈环状的浅沟槽隔离结构、呈环状的衬底引出端和mos单元,其中,

2.根据权利要求1所述的esd防护器件,其特征在于,同一行中,两列所述未重掺杂块基于所述漏端重掺杂区的中心位置对称。

3.根据权利要求1所述的esd防护器件,其特征在于,所述mos单元还包括:若干块状隔离结构,所述块状隔离结构填充所述未重掺杂块所在的位置。

4.根据权利要求3所述的esd防护器件,其特征在于,所述块状隔离结构的材质为二氧化硅。

5.根据权利要求1所述的esd防护器件,其特征在于,所述mos单元还包括:多个轻掺杂漏区,所述轻掺杂漏区分别位于所述源端重掺杂区侧以及所述漏端重掺杂区侧并且延伸至所述栅端多晶硅层底部。

6.根据权利要求1所述的esd防护器件,其特征在于,所述esd防护器件还包括:第一至第四导电插塞,第一导电插塞连接所述栅端多晶硅层,第二导电插塞连接所述源端重掺杂区,第三导电插塞连接所述漏端重掺杂区,第四导电插塞连接所述衬底引出端。

7.根据权利要求1-6中任一项所述的esd防护器件,其特征在于,所述阱区中掺杂离子的导电类型为p型,所述衬底引出端中掺杂离子的导电类型为p型,所述源端重掺杂区中掺杂离子的导电类型为n型,所述漏端重掺杂区中掺杂离子的导电类型为n型。

8.根据权利要求1-6中任一项所述的esd防护器件,其特征在于,所述阱区中掺杂离子的导电类型为n型,所述衬底引出端中掺杂离子的导电类型为n型,所述源端重掺杂区中掺杂离子的导电类型为p型,所述漏端重掺杂区中掺杂离子的导电类型为p型。

9.根据权利要求1-6中任一项所述的esd防护器件,其特征在于,在所述esd防护器件工作时,所述栅端多晶硅层、源端重掺杂区和所述衬底引出端均连接低电平,漏端重掺杂区连接高电平。

技术总结

本申请提供一种ESD防护器件,包括:衬底、阱区、呈环状的浅沟槽隔离结构、呈环状的衬底引出端和MOS单元,其中,MOS单元包括:栅端多晶硅层、两个源端重掺杂区、一个漏端重掺杂区、金属硅化物阻挡层,其中,漏端重掺杂区中形成有若干未重掺杂块,未重掺杂块按阵列形式排布于金属硅化物阻挡层底部。本申请在漏端重掺杂区的有源区中,设置阵列排布的未重掺杂块,以使未重掺杂块和漏端有源区交替排列,使得每行MOS结构中的ESD电流仅能从两个未重掺杂块之间流过,减少了漏端有源区面积,增大了整流电阻,从而可以缩减金属硅化物阻挡层覆盖漏端重掺杂区的横向尺寸,在不增加任何成本的情况下缩小器件整体面积,提高了芯片的集成度。

技术研发人员:范炜盛

受保护的技术使用者:华虹半导体(无锡)有限公司

技术研发日:

技术公布日:2024/8/26

- 还没有人留言评论。精彩留言会获得点赞!