高效能运算装置及其制造方法与流程

本发明是关于运算装置的结构及其制造方法,特别是有关高效能运算装置的结构及其制造方法。

背景技术:

1、在先进半导体制造技术中,装置尺寸的持续减小及电路配置的日益复杂,使得集成电路(ic)的设计及制造更具挑战性且成本更高。在追求装置效能更好、足迹更小及功率消耗更低的持续过程中,已经探索出使线宽减小的先进半导体制造技术,包括使用环绕式栅极(gaa)型晶体管的技术。环绕式栅极型晶体管可用于与其前身显著不同的结构中,系因可以更有效且可控的方式操纵通道电流,从而提高包括环绕式栅极型晶体管之装置的电效能。

2、虽然用于制造基于环绕式栅极型晶体管之半导体装置的技术确实已有一些改进,但此类技术仍无法满足市场需求。举例而言,在先进应用中不断尝试减小装置尺寸会对半导体装置的积体化产生困难。高效能运算(hpc)装置(诸如图形处理单元(gpu)芯片)需要在环绕式栅极芯片上形成高速及低功耗晶体管。环绕式栅极芯片的核心电路主要用于运算目的,而环绕式栅极芯片的非核心电路(例如,输入/输出电路)则用于方便核心电路的操作。然而,环绕式栅极芯片的非核心电路需要厚的栅极介电材料以满足大的电压下降需求,而核心电路的每个半导体通道材料奈米片之间的有限奈米片间距(inter nanosheetspacing)无法容纳厚的栅极介电材料。

3、因此,需要解决用于制造基于环绕式栅极型晶体管之半导体装置的积体化问题。

技术实现思路

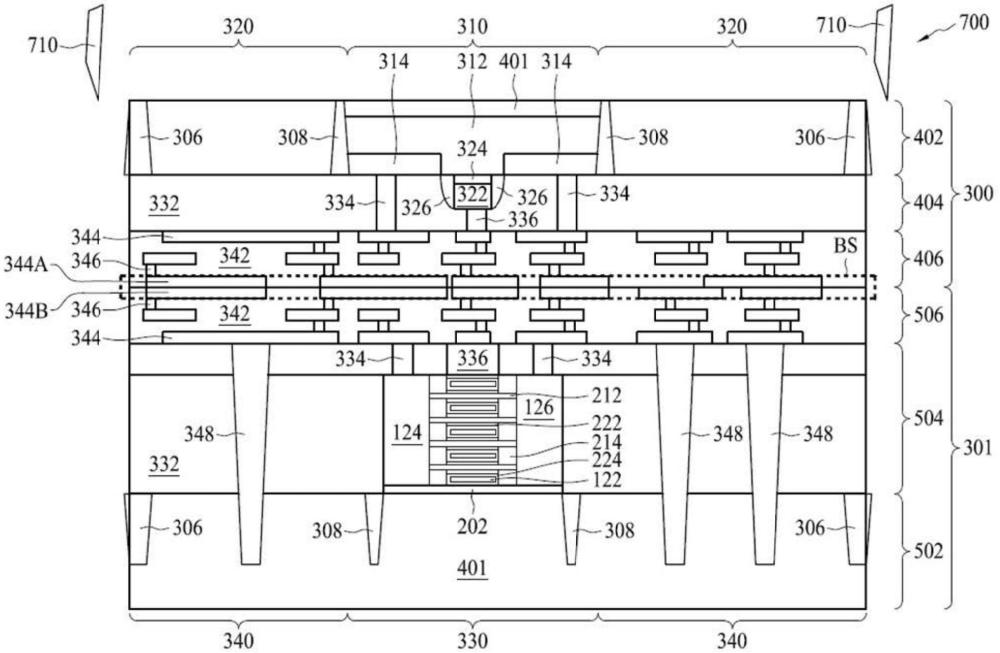

1、根据本揭示内容之一态样,一半导体装置包括:一第一基板,其包括由平面型晶体管或鳍型晶体管形成的复数个第一型晶体管,其中平面型晶体管之每一者的一栅极氧化硅层具有一第一厚度,且鳍型晶体管之每一者的一栅极氧化硅层具有一第二厚度;以及一第二基板,其接合至第一基板,并包括由环绕式栅极(gaa)型晶体管形成的复数个第二型晶体管,其中环绕式栅极型晶体管之每一者的一栅极氧化硅层具有一第三厚度。第三厚度小于第一厚度或第二厚度。

2、根据本揭示内容之一态样,一半导体装置包括:一第一基板,其包括由平面型晶体管或鳍型晶体管形成的复数个第一型晶体管,其中第一型晶体管在一第一电压下操作,且其中复数个第一型晶体管之每一者具有与一第一高介电常数介电层堆栈的一第一栅极氧化硅层,第一栅极氧化硅层与第一高介电常数介电层具有一第一组合厚度;以及一第二基板,其接合至第一基板,并包括由环绕式栅极(gaa)型晶体管形成的复数个第二型晶体管,其中第二型晶体管在小于第一电压的一第二电压下操作,且其中复数个第二型晶体管之每一者具有与一第二高介电常数介电层堆栈的一第二栅极氧化硅层,第二栅极氧化硅层与第二高介电常数介电层具有一第二组合厚度。第一组合厚度大于第二组合厚度。

3、根据本揭示内容之一态样,一方法包括:在一第一半导体晶圆上形成复数个第一晶粒区,其中第一晶粒区之每一者包含由平面型晶体管或鳍型晶体管形成的复数个第一型晶体管,其中平面型晶体管之每一者的一栅极氧化硅层具有一第一厚度,且鳍型晶体管之每一者的一栅极氧化硅层具有一第二厚度;邻近第一晶粒区形成一第一互联机区域;在一第二半导体晶圆上形成复数个第二晶粒区,其中第二晶粒区之每一者包含由环绕式栅极(gaa)型晶体管形成的复数个第二型晶体管,其中环绕式栅极型晶体管之每一者的一栅极氧化硅层具有一第三厚度;邻近第二晶粒区形成一第二互联机区域;以及藉由将第一晶粒区之每一者电耦合至第二晶粒区之对应体而将第一半导体晶圆接合至第二半导体晶圆。第三厚度小于第一厚度或第二厚度。

技术特征:

1.一种半导体结构,其包含:

2.根据权利要求1的半导体结构,其中该第三厚度小于约1nm。

3.根据权利要求1的半导体结构,其中该第二厚度实质上等于或大于约1.5nm。

4.根据权利要求1的半导体结构,其中该第一厚度实质上等于或大于约1.8nm。

5.根据权利要求1的半导体结构,其中该等第一型晶体管在一第一电压下操作,且该等第二型晶体管在小于该第一电压的一第二电压下操作。

6.根据权利要求1的半导体结构,更包含:

7.根据权利要求6的半导体结构,其中该等第一型晶体管与该等第二型晶体管进一步互连,以允许从该输入端输入的该电力信号或该电信号在通过该接合结构之前藉由进入该等第一型晶体管而到达该等第二型晶体管。

8.根据权利要求7的半导体结构,其中该等第一型晶体管与该等第二型晶体管进一步互连,以允许从该等第二型晶体管输出至一输出端的该电力信号或该电信号藉由首先通过该接合结构而到达该输出端。

9.根据权利要求6的半导体结构,更包含位于该第一基板及该第二基板之至少一者中的一基板通路,其电连接至该接合结构。

10.根据权利要求6的半导体结构,其中该接合结构包含一混合接合层、一凸块下金属、一导电凸块、或一微凸块之一者。

11.根据权利要求1的半导体结构,其中该等第二型晶体管形成用于人工智能机器学习或人工智能深度学习的应用的一处理器。

12.根据权利要求1的半导体结构,其中该第二基板包含一输入/输出电路、一模拟电路、一电源电路、及一内存电路之至少一者。

13.一种半导体装置,其包含:

14.根据权利要求13的半导体装置,其中该第二电压经由该等第一型晶体管并通过该第一基板与该第二基板之间的一接合结构而提供至等该第二型晶体管。

15.根据权利要求14的半导体装置,其中该接合结构包含一混合接合层、一凸块下金属、一导电凸块、或一微凸块之一者。

16.根据权利要求13的半导体装置,其中该第二组合厚度小于该第一组合厚度至少50%。

17.根据权利要求13的半导体装置,其中该第一基板及该第二基板之至少一者包含电耦合至该第一基板及该第二基板之另一者的一基板通路。

18.一种方法,其包含:

19.根据权利要求18的方法,其更包含:

20.根据权利要求18的方法,在将该第一半导体晶圆接合至该第二半导体晶圆之前,更包含:

技术总结

本发明所申请内容揭示半导体装置、半导体结构以及形成半导体装置的方法,其中所述半导体结构包括一第一基板及一第二基板。第一基板具有由平面型晶体管或鳍型晶体管形成的复数个第一型晶体管,其中平面型晶体管之每一者的一栅极氧化硅层具有一第一厚度,且鳍型晶体管之每一者的一栅极氧化硅层具有一第二厚度。第二基板接合至第一基板,并包括由环绕式栅极型晶体管形成的复数个第二型晶体管,其中环绕式栅极型晶体管之每一者的一栅极氧化硅层具有一第三厚度。第三厚度小于第一厚度或第二厚度。

技术研发人员:陈文良

受保护的技术使用者:爱普科技股份有限公司

技术研发日:

技术公布日:2024/12/19

- 还没有人留言评论。精彩留言会获得点赞!