包括多个焊盘的存储器装置和检测其焊盘的裂纹的方法与流程

本文描述的本发明构思的各种示例实施例涉及半导体存储器装置,更具体地,涉及包括多个焊盘的存储器装置和检测该存储器装置的焊盘裂纹的方法。

背景技术:

1、半导体存储器可以被主要分为易失性存储器或非易失性存储器。易失性存储器(例如dram或sram)的读取速度和写入速度较快,但是当电源被关闭时,存储在易失性存储器中的数据消失。相反,即使在电源被关闭时,非易失性存储器也可以保持数据。因此,非易失性存储器可用于存储无论是否被供电都必须保存的内容。

2、半导体存储器可以包括当形成封装件时暴露于外部的多个焊盘。当测试半导体存储器时,多个焊盘可能受到诸如探针或布线接合的各种原因的应力。当由于各种应力而在焊盘中的一个中出现裂纹时,半导体存储器的操作可能受到影响。

技术实现思路

1、本发明构思的各种示例实施例提供了一种存储器装置和一种焊盘裂纹检测方法,在该方法中裂纹检测结构布置在包括在存储器装置中的焊盘下方,并基于发送到裂纹检测结构的脉冲信号的延迟来检查在焊盘中是否已经出现裂纹。

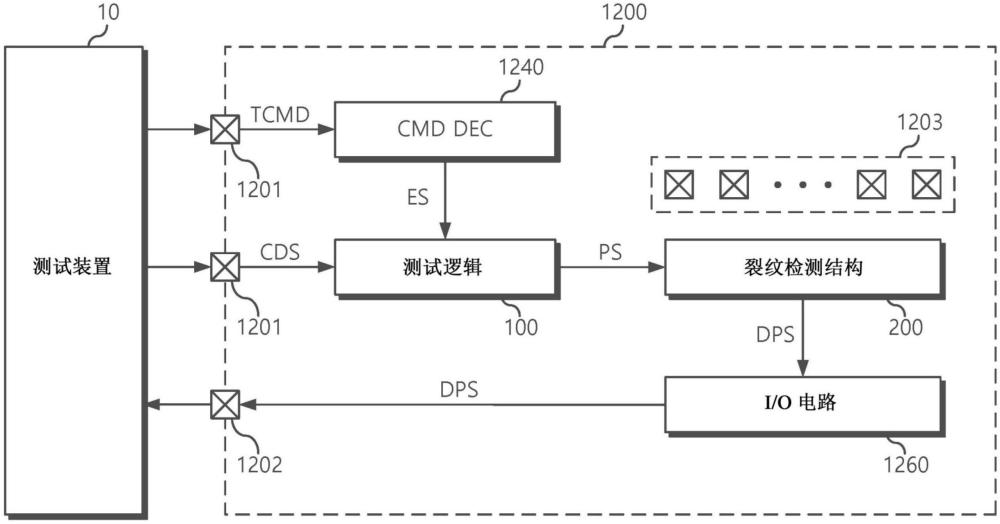

2、本发明构思的一些示例实施例提供了一种存储器装置,包括:存储器单元阵列;第一焊盘,其被配置为从外部装置接收命令;第二焊盘,其被配置为与外部装置交换数据;第三焊盘;测试逻辑,其被配置为基于通过第一焊盘接收的测试命令来产生测试脉冲信号;以及

3、裂纹检测结构,其布置在第三焊盘下方并且被配置为包括从测试逻辑串联连接到第二焊盘的线。基于当测试脉冲信号通过裂纹检测结构时改变的延迟脉冲信号的延迟来检测在第三焊盘中出现的裂纹。

4、本发明构思的一些示例实施例提供了一种检测存储器装置中的裂纹的方法,该方法包括:将测试命令从测试装置发送到存储器装置;基于测试命令产生测试脉冲信号;发送通过布置在测试目标焊盘下方的裂纹检测结构的测试脉冲信号;经由存储器装置的数据焊盘将已经通过裂纹检测结构的延迟脉冲信号输出到测试装置;以及比较测试脉冲信号和延迟脉冲信号,以基于延迟脉冲信号的延迟来确定测试目标焊盘是否包含裂纹。

5、本发明构思的一些示例实施例提供了一种存储器装置,包括:测试目标焊盘;测试逻辑,其被配置为基于从外部装置接收的测试命令来产生测试脉冲信号;裂纹检测结构,其布置在测试目标焊盘下方,并且包括横跨测试目标焊盘串联连接的线;以及裂纹检测电路,其被配置为基于当测试脉冲信号通过裂纹检测结构时改变的延迟脉冲信号的延迟来检测在测试目标焊盘中是否出现裂纹。

技术特征:

1.一种存储器装置,包括:

2.根据权利要求1所述的存储器装置,其中,所述裂纹检测结构包括:

3.根据权利要求2所述的存储器装置,其中,所述第三焊盘在第一金属层上,

4.根据权利要求2所述的存储器装置,其中,所述第一线部分中的每一个的长度被配置为长于所述第二线部分中的每一个的长度。

5.根据权利要求2所述的存储器装置,其中,所述第一线部分平行地布置并且以指定的间隔间隔开。

6.根据权利要求1所述的存储器装置,其中,所述裂纹检测结构包括:

7.根据权利要求1所述的存储器装置,其中,当所述延迟脉冲信号的延迟大于参考值时,确定在所述第三焊盘中存在裂纹。

8.根据权利要求1所述的存储器装置,其中,当所述延迟脉冲信号的边缘斜率小于参考值时,确定在所述第三焊盘中存在裂纹。

9.根据权利要求1所述的存储器装置,还包括:

10.根据权利要求1所述的存储器装置,还包括:

11.一种检测存储器装置中的裂纹的方法,所述方法包括:

12.根据权利要求11所述的方法,其中,确定所述测试目标焊盘是否包含裂纹包括当所述延迟脉冲信号的延迟大于参考值时确定在所述测试目标焊盘中存在裂纹。

13.根据权利要求11所述的方法,其中,确定所述测试目标焊盘是否包含裂纹包括当所述延迟脉冲信号的边缘斜率小于参考值时确定在所述测试目标焊盘中存在裂纹。

14.根据权利要求11所述的方法,其中,确定所述测试目标焊盘是否包含裂纹包括当所述延迟脉冲信号的延迟值偏离正态分布时确定在所述测试目标焊盘中存在裂纹。

15.根据权利要求11所述的方法,其中,所述裂纹检测结构包括:

16.根据权利要求11所述的方法,其中,所述裂纹检测结构包括:

17.一种存储器装置,包括:

18.根据权利要求17所述的存储器装置,还包括:

19.根据权利要求18所述的存储器装置,其中,所述裂纹检测结构包括:

20.根据权利要求19所述的存储器装置,其中,

技术总结

公开了一种存储器装置和一种检测存储器装置中的裂纹的方法。该存储器装置包括:存储器单元阵列;第一焊盘,其被配置为从外部装置接收命令;第二焊盘,其被配置为与外部装置交换数据;第三焊盘;测试逻辑,其被配置为基于通过第一焊盘接收的测试命令来产生测试脉冲信号;以及裂纹检测结构,其形成在第三焊盘下方,并被配置为包括从测试逻辑串联连接到第二焊盘的线。基于当测试脉冲信号通过裂纹检测结构时改变的延迟脉冲信号的延迟来检测在第三焊盘中出现的裂纹。

技术研发人员:千道宗,金正旭,朴玟秀,权志锡,李硕宰

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/12/5

- 还没有人留言评论。精彩留言会获得点赞!