CMOS器件的制备方法与流程

本申请涉及半导体制造,具体涉及一种cmos器件的制备方法。

背景技术:

1、为了在单位面积内集成更多的门电路,工艺制程越来越先进,先进制程中的一个特点是栅极材料(例如多晶硅材料)越来越薄,栅极材料的厚度限制了高压cmos(例如5vcmos)自对准注入ldd(轻掺杂漏区)的最大能量,从而限制了器件的击穿电压(breakdownvoltage,bv),因为通常情况下,ldd注入能量越大,bv越高。

2、在开发5v cmos的时候,为了形成更加缓变的ldd结,提高器件的bv,ldd注入通常采用尽可能大的能量和最大的离子注入倾斜角度(45°)倾斜注入。传统的自对准ldd注入时,栅极材料也会直接面对ldd注入,为了避免ldd进入沟道,ldd能量被栅极材料厚度限制,这又与先进制程中栅极材料越来越薄的需求相悖。但是在很多应用中,受栅极材料厚度限制,对先进制程节点高压cmos(例如5v cmos)器件的bv的要求却没有降低。

技术实现思路

1、本申请提供了一种cmos器件的制备方法,可以解决先进制程节点中,高压cmos器件区的ldd注入能量太高打穿器件栅极、高压cmos器件的bv不够高等问题中的至少一个问题。

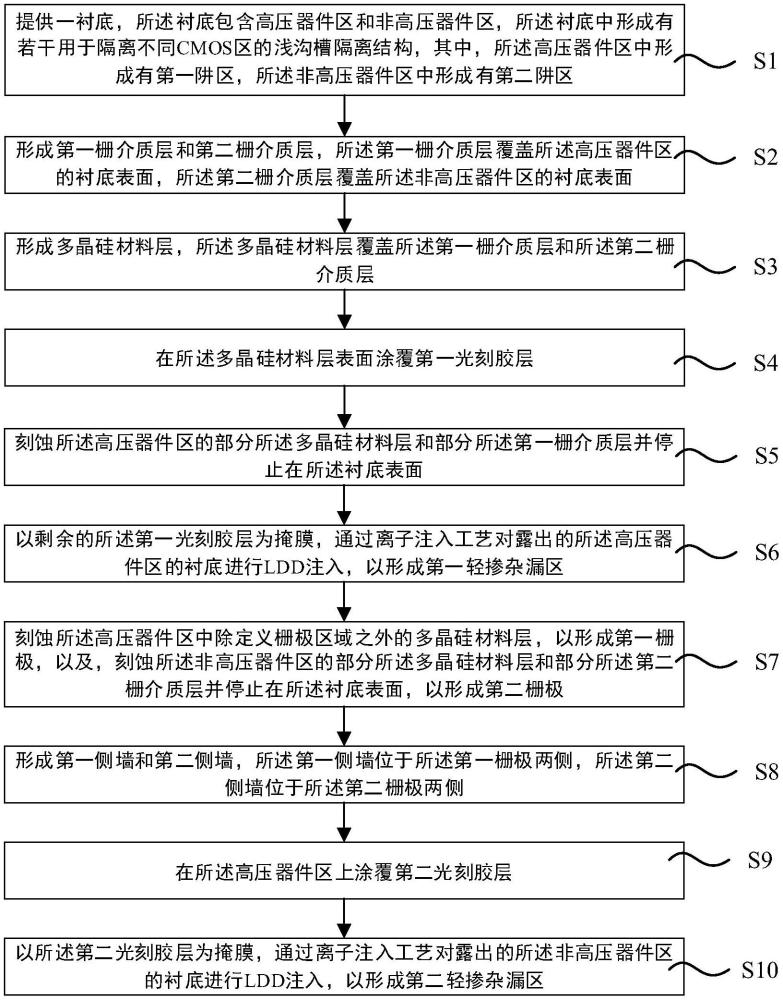

2、本申请实施例提供了一种cmos器件的制备方法,包括:

3、步骤s1:提供一衬底,所述衬底包含高压器件区和非高压器件区,所述衬底中形成有若干用于隔离不同cmos区的浅沟槽隔离结构,其中,所述高压器件区中形成有第一阱区,所述非高压器件区中形成有第二阱区;

4、步骤s2:形成第一栅介质层和第二栅介质层,所述第一栅介质层覆盖所述高压器件区的衬底表面,所述第二栅介质层覆盖所述非高压器件区的衬底表面;

5、步骤s3:形成多晶硅材料层,所述多晶硅材料层覆盖所述第一栅介质层和所述第二栅介质层;

6、步骤s4:在所述多晶硅材料层表面涂覆第一光刻胶层;

7、步骤s5:刻蚀所述高压器件区的部分所述多晶硅材料层和部分所述第一栅介质层并停止在所述衬底表面;

8、步骤s6:以剩余的所述第一光刻胶层为掩膜,通过离子注入工艺对露出的所述高压器件区的衬底进行ldd注入,以形成第一轻掺杂漏区;

9、步骤s7:刻蚀所述高压器件区中除定义栅极区域之外的多晶硅材料层,以形成第一栅极,以及,刻蚀所述非高压器件区的部分所述多晶硅材料层和部分所述第二栅介质层并停止在所述衬底表面,以形成第二栅极;

10、步骤s8:形成第一侧墙和第二侧墙,所述第一侧墙位于所述第一栅极两侧,所述第二侧墙位于所述第二栅极两侧;

11、步骤s9:在所述高压器件区上涂覆第二光刻胶层;以及

12、步骤s10:以所述第二光刻胶层为掩膜,通过离子注入工艺对露出的所述非高压器件区的衬底进行ldd注入,以形成第二轻掺杂漏区。

13、可选的,在所述cmos器件的制备方法中,在以剩余的所述第一光刻胶层为掩膜,通过离子注入工艺对露出的所述高压器件区的衬底进行ldd注入,以形成第一轻掺杂漏区的过程中,离子注入能量为20kev~150kev;离子注入角度为7°~45°;离子注入剂量为5e12/cm2~1e14/cm2。

14、可选的,在所述cmos器件的制备方法中,在以所述第二光刻胶层为掩膜,通过离子注入工艺对露出的所述非高压器件区的衬底进行ldd注入,以形成第二轻掺杂漏区的过程中,离子注入能量为5kev~40kev;离子注入角度为0°~45°;离子注入剂量为5e12/cm2~1e14/cm2。

15、可选的,在所述cmos器件的制备方法中,在形成第二轻掺杂漏区之后,所述cmos器件的制备方法还包括:去除所述第二光刻胶层。

16、可选的,在所述cmos器件的制备方法中,在形成第二轻掺杂漏区之后,所述cmos器件的制备方法还包括:

17、形成第四侧墙和第五侧墙,所述第四侧墙位于所述第一侧墙侧,所述第五侧墙位于所述第二侧墙侧。

18、可选的,在所述cmos器件的制备方法中,在形成第四侧墙和第五侧墙之后,所述cmos器件的制备方法还包括:

19、通过离子注入工艺对露出的所述高压器件区的衬底和非高压器件区的衬底分别进行离子注入,以在所述第一轻掺杂漏区中形成第一重掺杂区以及在所述第二轻掺杂漏区中形成第二重掺杂区。

20、可选的,在所述cmos器件的制备方法中,所述高压器件区包括:高压nmos区和高压pmos区。

21、可选的,在所述cmos器件的制备方法中,所述非高压器件区包括:中压nmos区、中压pmos区、低压nmos区和低压pmos区中的至少一种。

22、本申请技术方案,至少包括如下优点:

23、本申请提供了一种cmos器件的制备方法,首先刻蚀高压器件区的部分多晶硅材料层,然后在不去胶情况下进行离子注入形成高压的第一轻掺杂漏区(ldd),接着再进行非高压器件区的栅极光刻,刻蚀部分多晶硅材料层形成非高压器件区的第二栅极,同时刻蚀高压器件区的除定义栅极区域之外的多晶硅材料层形成完整的高压器件区的第一栅极,最后在不去胶情况下再进行离子注入形成非高压的第二轻掺杂漏区。本申请通过将高压cmos器件区的第一栅极部分刻蚀与非高压器件区的第二栅极刻蚀分开进行,并且分区域进行ldd注入,这样既可以在栅极厚度较薄以及不增加成本/不增加光罩的情况下,不打穿(损伤)栅极,又可以直接、有效地增加器件的ldd注入的能量,尤其是高压器件区的ldd注入的能量,改善先进制程中高压cmos器件的bv,提高器件的抗高压击穿性能,提高产品的竞争力。

技术特征:

1.一种cmos器件的制备方法,其特征在于,包括:

2.根据权利要求1所述的cmos器件的制备方法,其特征在于,在以剩余的所述第一光刻胶层为掩膜,通过离子注入工艺对露出的所述高压器件区的衬底进行ldd注入,以形成第一轻掺杂漏区的过程中,离子注入能量为20kev~150kev;离子注入角度为7°~45°;离子注入剂量为5e12/cm2~1e14/cm2。

3.根据权利要求1所述的cmos器件的制备方法,其特征在于,在以所述第二光刻胶层为掩膜,通过离子注入工艺对露出的所述非高压器件区的衬底进行ldd注入,以形成第二轻掺杂漏区的过程中,离子注入能量为5kev~40kev;离子注入角度为0°~45°;离子注入剂量为5e12/cm2~1e14/cm2。

4.根据权利要求1所述的cmos器件的制备方法,其特征在于,在形成第二轻掺杂漏区之后,所述cmos器件的制备方法还包括:去除所述第二光刻胶层。

5.根据权利要求1或4所述的cmos器件的制备方法,其特征在于,在形成第二轻掺杂漏区之后,所述cmos器件的制备方法还包括:

6.根据权利要求5所述的cmos器件的制备方法,其特征在于,在形成第四侧墙和第五侧墙之后,所述cmos器件的制备方法还包括:

7.根据权利要求1所述的cmos器件的制备方法,其特征在于,所述高压器件区包括:高压nmos区和高压pmos区。

8.根据权利要求1所述的cmos器件的制备方法,其特征在于,所述非高压器件区包括:中压nmos区、中压pmos区、低压nmos区和低压pmos区中的至少一种。

技术总结

本申请提供一种CMOS器件的制备方法,首先刻蚀高压器件区的部分多晶硅材料层,然后在不去胶情况下进行离子注入形成高压的第一轻掺杂漏区,接着再进行非高压器件区的栅极光刻,刻蚀部分多晶硅材料层,以形成非高压器件区的第二栅极,同时刻蚀高压器件区的除定义栅极区域之外的多晶硅材料层,以形成完整的高压器件区的第一栅极,最后再进行离子注入形成非高压的第二轻掺杂漏区。本申请通过将高压CMOS器件区的第一栅极部分刻蚀与非高压器件区的第二栅极刻蚀分开进行,并且分区域进行LDD注入,这样既可以在栅极厚度较薄的情况下,不打穿栅极,又可以直接、有效地增加LDD注入的能量,改善先进制程中高压CMOS器件的BV。

技术研发人员:许昭昭

受保护的技术使用者:华虹半导体(无锡)有限公司

技术研发日:

技术公布日:2024/9/26

- 还没有人留言评论。精彩留言会获得点赞!