半导体装置及其制造方法与流程

本公开涉及半导体装置及其制造方法。

背景技术:

1、已知在具有指状的源电极、栅电极以及漏电极的场效应晶体管(fet:fieldeffect transistor)中,在电极的延伸方向配置多个具有源电极、栅电极以及漏电极的单位fet(例如专利文献1、专利文献2)。

2、现有技术文献

3、专利文献

4、专利文献1:日本特开2002-299351号公报

5、专利文献2:美国专利第9786660号说明书

6、在专利文献1和专利文献2中,通过在电极的延伸方向上配置多个单位fet,能缩短单位fet中的栅电极的宽度。因此,能抑制栅极电阻。但是,将栅极焊盘与离栅极焊盘远的栅电极电连接的栅极布线设于单位fet的上方。由此,栅极布线与漏电极之间的寄生电容变大,增益等特性会劣化。另一方面,若将栅极布线配置为不与单位fet重叠,则半导体装置会大型化。

技术实现思路

1、本公开是鉴于上述问题而完成的,其目的在于抑制特性的劣化并且实现小型化。

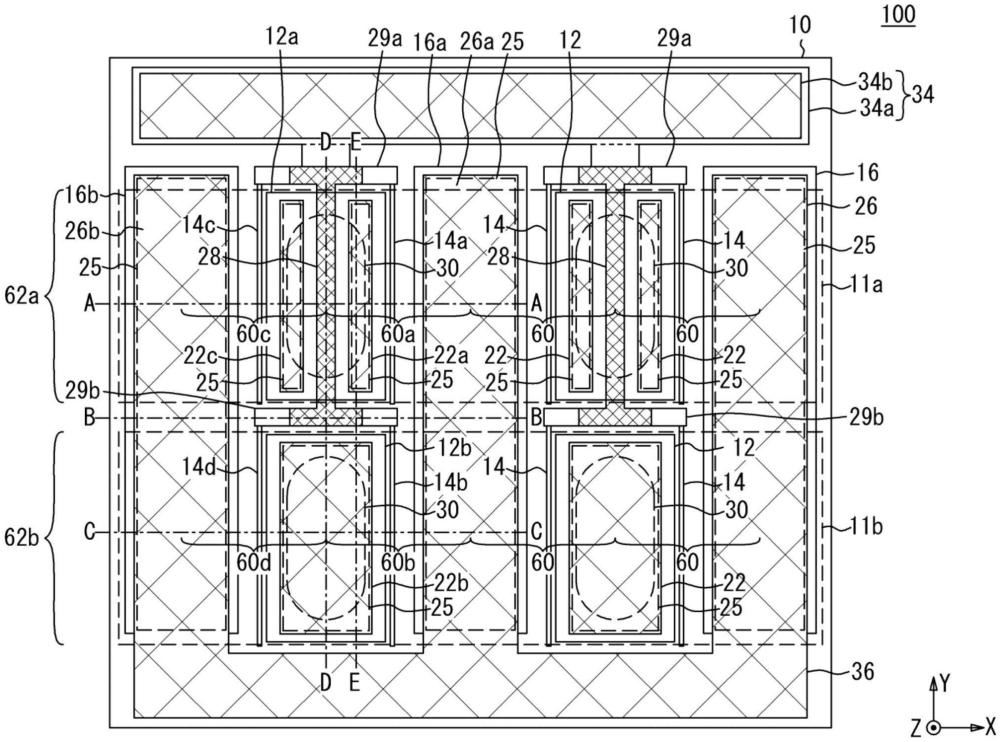

2、本公开的一个实施方式是半导体装置,该半导体装置具备:基板;第一单位fet,设于所述基板上,具备在第一方向延伸的第一源电极、在所述第一方向延伸的第一漏电极以及在所述第一方向延伸并且设于与所述第一方向交叉的第二方向上的所述第一源电极与所述第一漏电极之间的第一栅电极;第二单位fet,相对于所述第一单位fet设于所述第一方向上的所述基板上,具备在所述第一方向延伸的第二源电极、在所述第一方向延伸的第二漏电极以及在所述第一方向延伸并且设于所述第二方向上的所述第二源电极与所述第二漏电极之间的第二栅电极;第一源极布线,在所述第一方向延伸并且设于所述第一源电极上,与所述第一源电极电接触;栅极母线,以在所述第一方向上使所述第一栅电极配置于所述栅极母线与所述第二栅电极之间的方式设置,并且所述栅极母线与所述第一栅电极电连接;以及栅极布线,以与所述第一源电极非接触的方式设于所述第一源电极的上方,在所述第二方向上使所述第一源极布线配置于所述栅极布线与所述第一漏电极之间,所述栅极布线在所述第一方向延伸,将所述栅极母线与所述第二栅电极电连接,所述第一源极布线与所述第一源电极接触的区域的所述第一方向上的最大宽度大于等于在从所述基板的厚度方向观察时所述第一源极布线与所述第一源电极重叠的区域的所述第一方向上的最大宽度的1/2倍。

3、本公开的一个实施方式是半导体装置的制造方法,该制造方法具备以下工序:在基板上形成第一单位fet和第二单位fet,其中,该第一单位fet具备在第一方向延伸的第一源电极、在所述第一方向延伸的第一漏电极以及在所述第一方向延伸并且设于与所述第一方向交叉的第二方向上的所述第一源电极与所述第一漏电极之间的第一栅电极,该第二单位fet相对于所述第一单位fet位于所述第一方向上,具备在所述第一方向延伸的第二源电极、在所述第一方向延伸的第二漏电极以及在所述第一方向延伸并且设于所述第二方向上的所述第二源电极与所述第二漏电极之间的第二栅电极;同时形成第一源极布线、第二源极布线以及第一漏极布线,其中,该第一源极布线在所述第一方向延伸并且设于所述第一源电极上,与所述第一源电极电接触,该第二源极布线在所述第一方向延伸并且设于所述第二源电极上,与所述第二源电极电接触,该第一漏极布线在所述第一方向延伸并且设于所述第一漏电极上,与所述第一漏电极电接触;以及形成栅极布线,其中,该栅极布线以与所述第一源电极非接触的方式设于所述第一源电极的上方,在所述第二方向上使所述第一源极布线配置于所述栅极布线与所述第一漏电极之间,所述栅极布线在所述第一方向延伸,将栅极母线与所述第二栅电极电连接。

4、发明效果

5、根据本公开,能抑制特性的劣化并且实现小型化。

技术特征:

1.一种半导体装置,具备:

2.根据权利要求1所述的半导体装置,其中,

3.根据权利要求1或2所述的半导体装置,其中,

4.根据权利要求1或2所述的半导体装置,其中,

5.根据权利要求1或2所述的半导体装置,具备:

6.根据权利要求5所述的半导体装置,其中,

7.根据权利要求1或2所述的半导体装置,其中,

8.根据权利要求1或2所述的半导体装置,其中,

9.根据权利要求8所述的半导体装置,其中,

10.根据权利要求8所述的半导体装置,具备:

11.根据权利要求1或2所述的半导体装置,具备:

12.一种半导体装置的制造方法,具备以下工序:

技术总结

本公开涉及半导体装置及其制造方法。半导体装置具备:基板;第一单位FET,设于基板上,具备第一源电极、第一漏电极以及第一栅电极;第二单位FET,相对于第一单位FET设于第一方向上的基板上,具备第二源电极、第二漏电极以及第二栅电极;第一源极布线,在第一方向延伸并且设于第一源电极上,与第一源电极电接触;栅极母线,以在第一方向上使第一栅电极配置于栅极母线与第二栅电极之间的方式设置,并且栅极母线与第一栅电极电连接;以及栅极布线,以与第一源电极非接触的方式设于第一源电极的上方,在第二方向上使第一源极布线配置于栅极布线与第一漏电极之间,栅极布线在第一方向延伸,将栅极母线与第二栅电极电连接。

技术研发人员:堤优也

受保护的技术使用者:住友电工光电子器件创新株式会社

技术研发日:

技术公布日:2025/1/2

- 还没有人留言评论。精彩留言会获得点赞!