图像传感器的制作方法

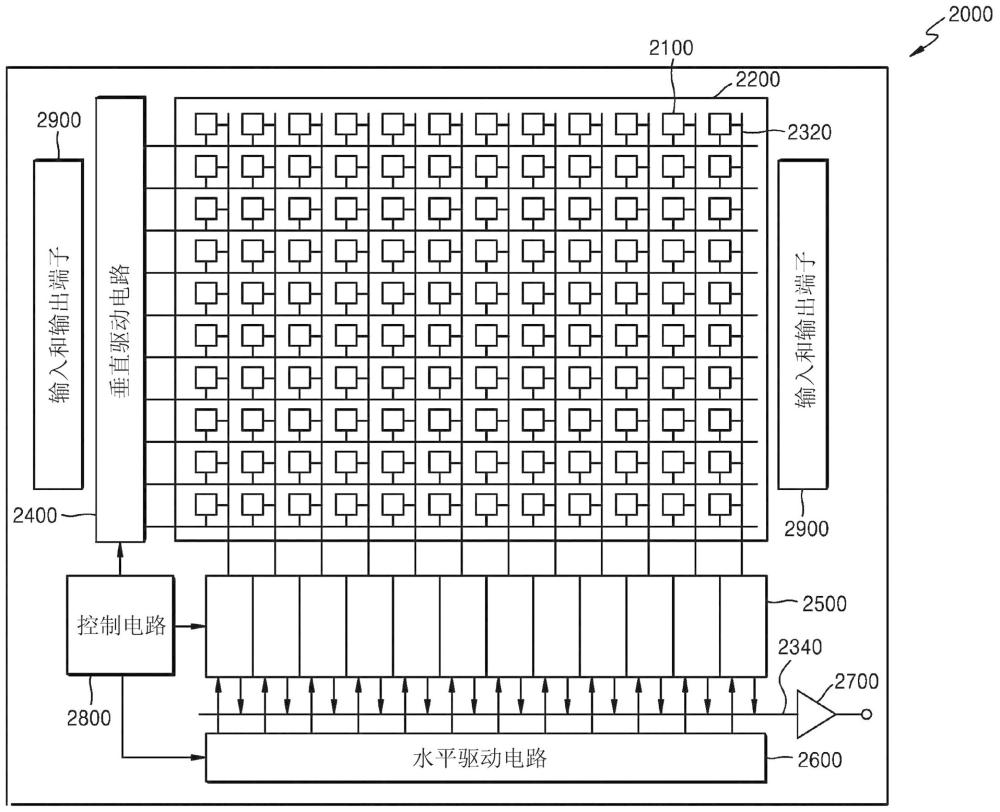

公开的示例实施例涉及图像传感器,并且更具体地,涉及包括深沟槽隔离结构的图像传感器。

背景技术:

1、图像传感器是将光学图像信号转换为电信号的装置。图像传感器包括多个像素,并且多个像素中的每个包括光电二极管区域和像素电路,光电二极管区域接收入射光并且将接收的光转换为电信号,像素电路通过使用由光电二极管区域生成的电荷来输出像素信号。随着图像传感器的集成度增大,每个像素的尺寸被减小,由此,存在难以减小或防止暗电流的问题。

技术实现思路

1、公开的示例实施例提供可减小暗电流并且可减少或防止光学串扰的图像传感器。

2、根据示例实施例的一个方面,一种图像传感器包括:半导体基底,包括第一表面和与第一表面背对的第二表面,半导体基底还包括光电转换区域;传输栅极,设置在半导体基底的第一表面上;掩埋绝缘层,设置在半导体基底的第一表面上以覆盖传输栅极;以及像素隔离结构,设置在像素隔离沟槽中,像素隔离沟槽从半导体基底的第一表面朝向半导体基底的第二表面延伸,像素隔离沟槽穿过掩埋绝缘层,像素隔离结构限定半导体基底中的多个像素,像素隔离结构的一部分被掩埋绝缘层覆盖。

3、根据示例实施例的一个方面,一种图像传感器包括:半导体基底,包括第一表面和与第一表面背对的第二表面,半导体基底还包括光电转换区域;传输栅极,设置在半导体基底的第一表面上;蚀刻停止层,设置在半导体基底的第一表面上以覆盖传输栅极;以及像素隔离结构,设置在像素隔离沟槽中,像素隔离沟槽从半导体基底的第一表面朝向半导体基底的第二表面延伸,像素隔离结构包括导电层,导电层包括反射金属材料,其中,蚀刻停止层的端部设置在导电层上,并且像素隔离结构和蚀刻停止层彼此不垂直叠置。

4、根据示例实施例的一个方面,一种图像传感器包括:半导体基底,包括第一表面和与第一表面背对的第二表面,半导体基底还包括光电转换区域;传输栅极,设置在半导体基底的第一表面上;以及像素隔离结构,设置在像素隔离沟槽中,像素隔离沟槽从半导体基底的第一表面延伸直到半导体基底的第二表面,其中,像素隔离结构包括导电层、阻挡导电层、像素隔离绝缘层和绝缘衬里,导电层设置在像素隔离沟槽中,导电层在与半导体基底的第一表面垂直的垂直方向上延伸,阻挡导电层在像素隔离沟槽中设置在导电层的侧壁上,像素隔离绝缘层在像素隔离沟槽中设置在导电层和阻挡导电层上,绝缘衬里在像素隔离沟槽的内壁上沿垂直方向延伸,绝缘衬里覆盖像素隔离绝缘层的侧壁和阻挡导电层的侧壁,并且像素隔离绝缘层的上表面设置在比半导体基底的第一表面高的水平处。

技术特征:

1.一种图像传感器,包括:

2.根据权利要求1所述的图像传感器,其中,像素隔离结构包括:

3.根据权利要求2所述的图像传感器,其中,像素隔离沟槽包括穿过半导体基底的第一部分和穿过掩埋绝缘层的第二部分,并且绝缘衬里设置在像素隔离沟槽的第一部分和第二部分中的每个的内壁上,

4.根据权利要求2所述的图像传感器,其中,像素隔离结构的上表面设置在与掩埋绝缘层的上表面相同的水平处。

5.根据权利要求2所述的图像传感器,其中,导电层包括反射金属材料。

6.根据权利要求2所述的图像传感器,其中,导电层包括铝、铜、银、钴、钨、铂、金、铬、钛、镍、钼、铁、镁、铱、钯和钌中的至少一种。

7.根据权利要求2所述的图像传感器,还包括:

8.根据权利要求7所述的图像传感器,其中,导电层的上表面设置在比器件隔离层的底表面低的水平处。

9.根据权利要求7所述的图像传感器,其中,导电层的上表面设置在比器件隔离层的底表面高且比器件隔离层的上表面低的水平处。

10.根据权利要求7所述的图像传感器,其中,导电层的上表面设置在比器件隔离层的上表面高的水平处。

11.根据权利要求2所述的图像传感器,其中,像素隔离绝缘层包括在像素隔离绝缘层中的空隙。

12.根据权利要求1至11中的任一项所述的图像传感器,其中,半导体基底在垂直方向上具有第一高度,并且

13.一种图像传感器,包括:

14.根据权利要求13所述的图像传感器,其中,像素隔离结构还包括:

15.根据权利要求14所述的图像传感器,还包括:

16.根据权利要求15所述的图像传感器,其中,蚀刻停止层的端部与器件隔离层的侧壁对齐,并且

17.根据权利要求16所述的图像传感器,其中,绝缘衬里设置在像素隔离沟槽的整个内壁上,并且

18.根据权利要求13至17中的任一项所述的图像传感器,其中,导电层包括铝、铜、银、钴、钨、铂、金、铬、钛、镍、钼、铁、镁、铱、钯和钌中的至少一种。

19.一种图像传感器,包括:

20.根据权利要求19所述的图像传感器,还包括:

技术总结

提供了图像传感器。所述图像传感器包括:半导体基底,包括第一表面和与第一表面背对的第二表面,半导体基底还包括光电转换区域;传输栅极,设置在半导体基底的第一表面上;掩埋绝缘层,设置在半导体基底的第一表面上以覆盖传输栅极;以及像素隔离结构,设置在像素隔离沟槽中,像素隔离沟槽从半导体基底的第一表面朝向半导体基底的第二表面延伸,像素隔离沟槽穿过掩埋绝缘层,像素隔离结构限定半导体基底中的多个像素,像素隔离结构的一部分被掩埋绝缘层覆盖。

技术研发人员:柳制亨,林夏珍,全宅洙

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2025/1/2

- 还没有人留言评论。精彩留言会获得点赞!