半导体器件的制作方法

各种示例实施方式涉及半导体器件和/或制造半导体器件的方法。

背景技术:

1、晶体管是执行电切换功能的半导体器件并用于各种集成电路(ic)器件(包括存储器、驱动ic、逻辑器件等中的一种或更多种)。为了提高ic器件的集成度,已经减小由ic器件中包括的晶体管所占据的空间,并且正在进行研究以在保持晶体管的性能的同时减小晶体管的尺寸。

2、氧化物半导体器件是透明半导体器件,其特征在于3.0ev或更大的宽带隙,并且已经研究多年。用于大面积显示驱动装置的氧化物半导体器件具有诸如低关断电流、高开/关比等电特性的特性。通过将具有上述特性的氧化物半导体器件应用于存储器或逻辑器件或者将氧化物半导体器件堆叠在si基器件上,可以提高集成度。

3、然而,由于氧化物半导体器件的按比例缩小而产生的短沟道效应可能使氧化物半导体器件的性能劣化。例如,随着沟道层的宽度、长度、厚度等中的一个或更多个减小,难以控制阈值电压(vth),并且沟道层和源极/漏极之间的减小的接触面积可能使接触电阻增大。更具体地,当通过使用前体在由金属材料形成的源极/漏极上形成氧化物半导体层时,在前体和金属材料之间的反应可能使接触电阻增大。

技术实现思路

1、提供一种包括金属氮化物层的半导体器件。

2、另外的方面将部分地在下面的描述中阐述,并且部分地将从该描述变得明显,或者可以通过实践本公开的所呈现的实施方式而获知。

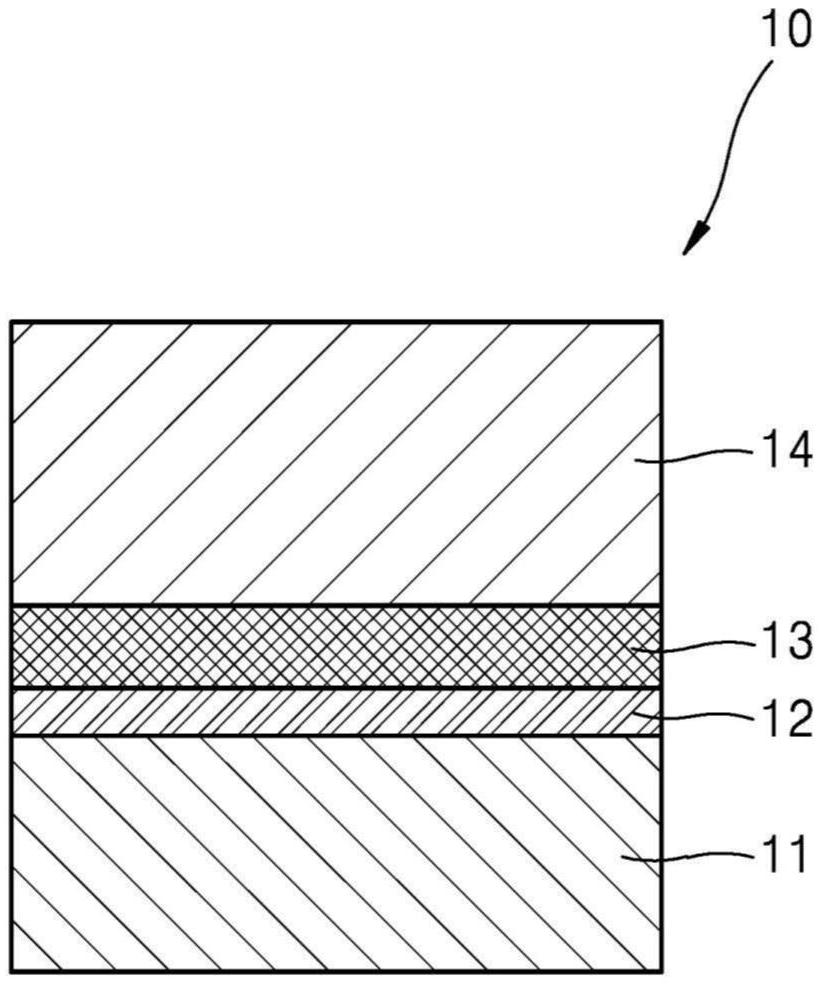

3、根据一些实例实施方式,一种半导体器件包括:氧化物半导体层;第一电极和第二电极,分别与氧化物半导体层相邻并彼此间隔开;金属氧化物层,在第一电极和第二电极中的至少一个和氧化物半导体层之间;金属氮化物层,在金属氧化物层和氧化物半导体层之间;栅电极,与氧化物半导体层间隔开;以及栅极绝缘层,布置在氧化物半导体层和栅电极之间。

4、金属氮化物层可以包括氧。金属氧化物层的厚度和金属氮化物层的厚度中的至少一个可以小于氧化物半导体层的厚度。

5、氧化物半导体层的厚度可以为10nm或更小。

6、氧化物半导体层的长度可以小于1微米。

7、金属氧化物层的厚度可以为5nm或更小。

8、金属氧化物层的厚度可以为约0.5nm至约3.5nm。

9、金属氮化物层的厚度可以为10nm或更小。

10、金属氧化物层的厚度可以是金属氮化物层的厚度的0.2倍至2倍。

11、金属氧化物层的厚度可以小于或等于第一电极的厚度的25%。金属氧化物层可以包括与包括在与金属氧化物层接触的电极中的金属相同的金属,所述电极来自第一电极和第二电极。

12、金属氧化物层可以包括w、co、ni、fe、ti、mo、cr、zr、hf、nb、ta、ag、au、al、cu、sn、v、ru、pt、zn和mg中的至少一种。

13、金属氮化物层可以包括ga、w、zn、v和ti中的至少一种。

14、第一电极和第二电极中的至少一个的表面可以通过金属氧化物层形成台阶。

15、金属氮化物层的宽度可以大于或等于氧化物半导体层的宽度。

16、氧化物半导体层的宽度和金属氮化物层的宽度之差可以大于或等于氧化物半导体层的宽度和金属氧化物层的宽度之差。

17、第一电极、金属氧化物层、金属氮化物层、氧化物半导体层和第二电极可以在第一电极的厚度方向上依次布置。

18、金属氧化物层可以包括布置在第一电极和氧化物半导体层之间的第一金属氧化物层以及布置在第二电极和氧化物半导体层之间的第二金属氧化物层,金属氮化物层可以布置在第一金属氧化物层和第二金属氧化物层中的至少一个和氧化物半导体层之间。

19、金属氮化物层可以包括在第一金属氧化物层和氧化物半导体层之间的第一金属氮化物层以及布置在第二金属氧化物层和氧化物半导体层之间的第二金属氮化物层。

20、第一金属氧化物层的厚度可以与第二金属氧化物层的厚度不同。

21、半导体器件可以通过原子层沉积工艺制造。

技术特征:

1.一种半导体器件,包括:

2.根据权利要求1所述的半导体器件,其中所述金属氮化物层包括氧。

3.根据权利要求1所述的半导体器件,其中所述金属氧化物层的厚度和所述金属氮化物层的厚度中的至少一个小于所述氧化物半导体层的厚度。

4.根据权利要求1所述的半导体器件,其中所述氧化物半导体层的厚度为10nm或更小。

5.根据权利要求1所述的半导体器件,其中所述氧化物半导体层的长度小于1微米。

6.根据权利要求1所述的半导体器件,其中所述金属氧化物层的厚度为5nm或更小。

7.根据权利要求1所述的半导体器件,其中所述金属氧化物层的厚度为0.5nm至3.5nm。

8.根据权利要求1所述的半导体器件,其中所述金属氮化物层的厚度为10nm或更小。

9.根据权利要求1所述的半导体器件,其中所述金属氧化物层的厚度为所述金属氮化物层的厚度的0.2倍至2倍。

10.根据权利要求1所述的半导体器件,其中所述金属氧化物层的厚度小于或等于所述第一电极的厚度的25%。

11.根据权利要求1所述的半导体器件,其中所述金属氧化物层包括与包括在与所述金属氧化物层接触的电极中的金属相同的金属,所述电极选自所述第一电极和所述第二电极。

12.根据权利要求8所述的半导体器件,其中所述金属氧化物层包括w、co、ni、fe、ti、mo、cr、zr、hf、nb、ta、ag、au、al、cu、sn、v、ru、pt、zn和mg中的至少一种。

13.根据权利要求12所述的半导体器件,其中所述金属氮化物层包括ga、w、zn、v和ti中的至少一种。

14.根据权利要求1所述的半导体器件,其中所述第一电极和所述第二电极中的至少一个的表面通过所述金属氧化物层形成台阶。

15.根据权利要求1所述的半导体器件,其中所述金属氮化物层的宽度大于或等于所述氧化物半导体层的宽度。

16.根据权利要求1所述的半导体器件,其中在所述氧化物半导体层的宽度和所述金属氮化物层的宽度之差大于或等于在所述氧化物半导体层的所述宽度和所述金属氧化物层的宽度之差。

17.根据权利要求1所述的半导体器件,其中所述第一电极、所述金属氧化物层、所述金属氮化物层、所述氧化物半导体层和所述第二电极在所述第一电极的厚度方向上依次布置。

18.根据权利要求1所述的半导体器件,其中所述金属氧化物层包括:

19.根据权利要求18所述的半导体器件,其中所述金属氮化物层包括:

20.根据权利要求18所述的半导体器件,其中所述第一金属氧化物层的厚度不同于所述第二金属氧化物层的厚度。

21.根据权利要求1所述的半导体器件,其中如果所述氧化物半导体层和所述金属氧化物层彼此直接接触,则在所述氧化物半导体层和所述金属氧化物层之间存在界面电阻。

技术总结

一种半导体器件包括:氧化物半导体层;第一电极和第二电极,彼此间隔开地布置并分别与氧化物半导体层相邻;金属氧化物层,布置在第一电极和第二电极中的至少一个和氧化物半导体层之间;以及金属氮化物层,布置在金属氧化物层和氧化物半导体层之间。

技术研发人员:杨智恩,金尚昱,车映官

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/12/30

- 还没有人留言评论。精彩留言会获得点赞!