一种封装结构以及相应的制备方法与流程

本发明涉及封装,具体为一种封装结构以及相应的制备方法。

背景技术:

1、先进封装技术的不断演进,晶圆级封装越来越得到广泛的应用;晶圆级封装可以在有限的空间内实现更高密度的集成(包括更高的密度或者更多的功能),在单个封装体内实现一个完整的系统功能;随着封装结构的日益复杂,供电对信号的干扰越来越受到关注,会导致逻辑错误,最终可能会显著降低平台整体电压与功耗。

技术实现思路

1、本发明的目的在于克服现有封装结构的供电对信号的干扰,会显著降低平台整体电压与功耗的问题,提供了一种封装结构以及相应的制备方法。

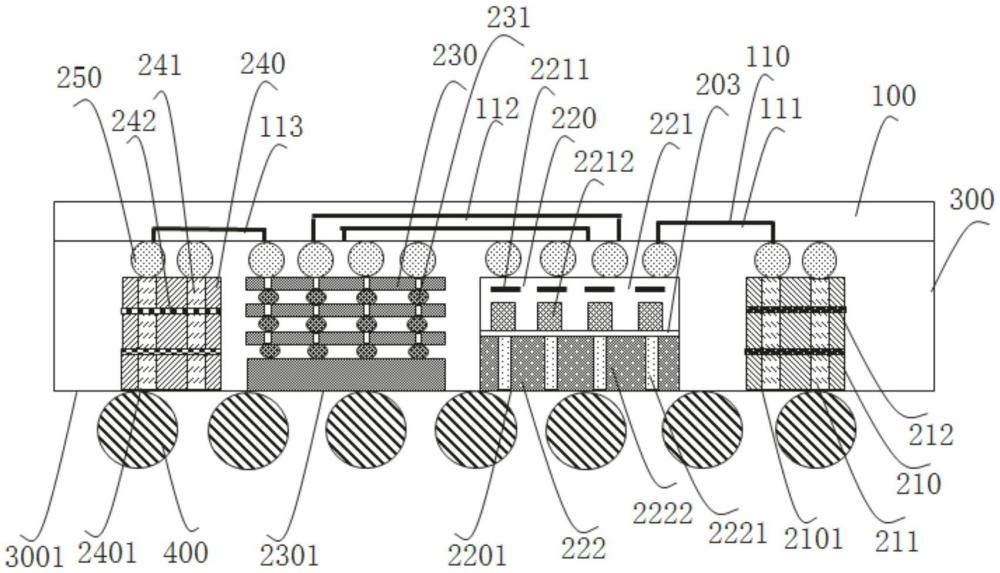

2、为了实现上述目的,本发明提供一种封装结构,包括:

3、中介层;

4、位于所述中介层表面的逻辑芯片结构、信号通道结构和塑封层;所述塑封层用于对所述逻辑芯片结构、所述信号通道结构进行包封,所述逻辑芯片结构远离所述中介层的一侧表面和所述信号通道结构远离所述中介层的一侧表面暴露于所述塑封层;

5、位于所述逻辑芯片结构远离所述中介层的一侧表面和所述信号通道结构远离所述中介层的一侧表面的导电结构;

6、其中,所述逻辑芯片结构包括位于所述中介层表面的逻辑芯片和位于所述逻辑芯片表面的电源通道结构,所述逻辑芯片具有信号层和电源层,所述逻辑芯片的电源层靠近所述电源通道结构并通过所述电源通道结构和相应的导电结构进行电连接实现供电,所述逻辑芯片的信号层靠近所述中介层并通过所述中介层、所述信号通道结构和相应的导电结构进行信号连接实现信号传输。

7、作为一种可实施方式,所述逻辑芯片结构和所述信号通道结构的高度相一致。

8、作为一种可实施方式,所述逻辑芯片的电源层包括多个电源区,所述电源通道结构包括衬底和贯穿所述衬底的多个导电柱,所述导电柱的两端分别连接对应的电源区和对应的导电结构。

9、作为一种可实施方式,所述逻辑芯片和所述电源通道结构通过第一混合键合层实现连接。

10、作为一种可实施方式,所述信号通道结构包括堆叠的至少一个信号通道芯片,相邻信号通道芯片之间通过第二混合键合层实现连接。

11、作为一种可实施方式,还包括:

12、位于所述中介层表面的内存芯片结构和导流通道结构,所述塑封层还用于对所述内存芯片结构和所述导流通道结构进行塑封,所述导流通道结构远离所述中介层的一侧表面暴露于所述塑封层,所述导流通道结构远离所述中介层的一侧表面具有导电结构;

13、其中,所述内存芯片结构通过所述中介层、所述导流通道结构和相应的导电结构进行电连接实现供电;所述内存芯片结构通过所述中介层、所述逻辑芯片的信号层、所述信号通道结构和相应的导电结构进行信号连接实现信号传输。

14、作为一种可实施方式,所述逻辑芯片结构、所述信号通道结构、所述导流通道结构的高度和所述内存芯片结构的高度相一致。

15、作为一种可实施方式,所述导流通道结构包括堆叠的至少一个导流通道芯片,相邻导流通道芯片通过第三混合键合层实现连接。

16、作为一种可实施方式,所述逻辑芯片结构、所述信号通道结构、所述内存芯片结构和所述导流通道结构通过第一焊料凸块和所述中介层实现连接。

17、作为一种可实施方式,所述内存芯片结构包括堆叠的至少一个内存芯片,相邻内存芯片通过第二焊料凸块实现连接。

18、作为一种可实施方式,所述内存芯片结构远离所述中介层的一侧表面暴露于所述塑封层,所述内存芯片结构远离所述中介层的一侧表面和所述塑封层远离所述中介层的一侧表面都具有导电结构。

19、相应的,本发明还提供一种封装结构的制备方法,包括:

20、形成中介层;

21、将逻辑芯片结构、信号通道结构设于所述中介层表面;

22、使用塑封料对所述逻辑芯片结构、所述信号通道结构进行塑封形成塑封层,且所述逻辑芯片结构远离所述中介层的一侧表面和所述信号通道结构远离所述中介层的一侧表面暴露于所述塑封层;

23、将导电结构设于所述逻辑芯片结构远离所述中介层的一侧表面和所述信号通道结构远离所述中介层的一侧表面;

24、其中,所述逻辑芯片结构包括位于所述中介层表面的逻辑芯片和位于所述逻辑芯片表面的电源通道结构;所述逻辑芯片具有信号层和电源层,所述逻辑芯片的电源层靠近所述电源通道结构并通过所述电源通道结构和相应的导电结构进行电连接实现供电,所述逻辑芯片的信号层靠近所述中介层并通过所述中介层、所述信号通道结构和相应的导电结构进行信号连接实现信号传输。

25、作为一种可实施方式,所述逻辑芯片的电源层包括多个电源区,所述电源通道结构包括衬底和贯穿所述衬底的多个导电柱,所述导电柱的两端分别用于连接对应的电源区和对应的导电结构。

26、作为一种可实施方式,所述信号通道结构包括堆叠的至少一个信号通道芯片,相邻信号通道芯片之间通过第二混合键合层实现连接

27、作为一种可实施方式,在将逻辑芯片结构、信号通道结构设于所述中介层表面的过程中,还包括将内存芯片结构、导流通道结构设于所述中介层表面;且在后续形成塑封层的过程中,还包括使用塑封料对所述内存芯片结构和所述导流通道结构进行塑封,且所述导流通道结构远离所述中介层的一侧表面暴露于所述塑封层;在后续设置导电结构的过程中,还包括将导电结构设于所述导流通道结构远离所述中介层的一侧表面;

28、其中,所述内存芯片结构通过所述中介层、所述导流通道结构和相应的导电结构进行电连接实现供电;所述内存芯片结构通过所述中介层、所述逻辑芯片的信号层、所述信号通道结构和相应的导电结构进行信号连接实现信号传输。

29、作为一种可实施方式,所述导流通道结构包括堆叠的至少一个导流通道芯片,相邻导流通道芯片通过第三混合键合层实现连接。

30、作为一种可实施方式,将所述逻辑芯片结构、所述信号通道结构、所述内存芯片结构和所述导流通道结构设于所述中介层表面的步骤包括:

31、将所述逻辑芯片结构、所述信号通道结构、所述内存芯片结构和所述导流通道结构通过第一焊料凸块设于所述中介层表面。

32、本发明的有益效果:

33、本发明提供了一种封装结构以及相应的制备方法,包括中介层和位于中介层表面的逻辑芯片结构、信号通道结构,逻辑芯片结构包括位于中介层表面的逻辑芯片和位于逻辑芯片表面的电源通道结构,通过将逻辑芯片的电源层靠近电源通道结构并通过电源通道结构和相应的导电结构进行电连接实现供电,逻辑芯片的信号层靠近中介层并通过中介层、信号通道结构和相应的导电结构进行信号连接实现信号传输,解决了供电干扰信号造成的问题,防止逻辑错误;而且,整体的电压与功耗可以显著降低,从而提升封装成品的效能。

技术特征:

1.一种封装结构,其特征在于,包括:

2.根据权利要求1所述的封装结构,其特征在于,所述逻辑芯片结构和所述信号通道结构的高度相一致。

3.根据权利要求1所述的封装结构,其特征在于,所述逻辑芯片的电源层包括多个电源区,所述电源通道结构包括衬底和贯穿所述衬底的多个导电柱,所述导电柱的两端分别连接对应的电源区和对应的导电结构。

4.根据权利要求1所述的封装结构,其特征在于,所述逻辑芯片和所述电源通道结构通过第一混合键合层实现连接。

5.根据权利要求1所述的封装结构,其特征在于,所述信号通道结构包括堆叠的至少一个信号通道芯片,相邻信号通道芯片之间通过第二混合键合层实现连接。

6.根据权利要求1所述的封装结构,其特征在于,还包括:

7.根据权利要求6所述的封装结构,其特征在于,所述逻辑芯片结构、所述信号通道结构、所述导流通道结构的高度和所述内存芯片结构的高度相一致。

8.根据权利要求6所述的封装结构,其特征在于,所述导流通道结构包括堆叠的至少一个导流通道芯片,相邻导流通道芯片通过第三混合键合层实现连接。

9.根据权利要求6所述的封装结构,其特征在于,所述逻辑芯片结构、所述信号通道结构、所述内存芯片结构和所述导流通道结构通过第一焊料凸块和所述中介层实现连接。

10.根据权利要求6所述的封装结构,其特征在于,所述内存芯片结构包括堆叠的至少一个内存芯片,相邻内存芯片通过第二焊料凸块实现连接。

11.根据权利要求6所述的封装结构,其特征在于,所述内存芯片结构远离所述中介层的一侧表面暴露于所述塑封层,所述内存芯片结构远离所述中介层的一侧表面和所述塑封层远离所述中介层的一侧表面都具有导电结构。

12.一种封装结构的制备方法,其特征在于,包括:

13.根据权利要求12所述的封装结构的制备方法,其特征在于,所述逻辑芯片的电源层包括多个电源区,所述电源通道结构包括衬底和贯穿所述衬底的多个导电柱,所述导电柱的两端分别用于连接对应的电源区和对应的导电结构。

14.根据权利要求12所述的封装结构的制备方法,其特征在于,所述信号通道结构包括堆叠的至少一个信号通道芯片,相邻信号通道芯片之间通过第二混合键合层实现连接。

15.根据权利要求12所述的封装结构的制备方法,其特征在于,在将逻辑芯片结构、信号通道结构设于所述中介层表面的过程中,还包括将内存芯片结构、导流通道结构设于所述中介层表面;且在后续形成塑封层的过程中,还包括使用塑封料对所述内存芯片结构和所述导流通道结构进行塑封,且所述导流通道结构远离所述中介层的一侧表面暴露于所述塑封层;在后续设置导电结构的过程中,还包括将导电结构设于所述导流通道结构远离所述中介层的一侧表面;

16.根据权利要求15所述的封装结构的制备方法,其特征在于,所述导流通道结构包括堆叠的至少一个导流通道芯片,相邻导流通道芯片通过第三混合键合层实现连接。

17.根据权利要求15所述的封装结构的制备方法,其特征在于,将所述逻辑芯片结构、所述信号通道结构、所述内存芯片结构和所述导流通道结构设于所述中介层表面的步骤包括:

技术总结

本发明涉及封装技术领域,提供了一种封装结构以及相应的制备方法,包括中介层和位于中介层表面的逻辑芯片结构、信号通道结构,逻辑芯片结构包括位于中介层表面的逻辑芯片和位于逻辑芯片表面的电源通道结构,通过将逻辑芯片的电源层靠近电源通道结构并通过电源通道结构和相应的导电结构进行电连接实现供电,逻辑芯片的信号层靠近中介层并通过中介层、信号通道结构和相应的导电结构进行信号连接实现信号传输,使得解决了供电干扰信号造成的问题,防止逻辑错误;而且,整体的电压与功耗可以显著降低,从而提升封装成品的效能。

技术研发人员:陈海杰,谢皆雷

受保护的技术使用者:江阴长电先进封装有限公司

技术研发日:

技术公布日:2024/10/17

- 还没有人留言评论。精彩留言会获得点赞!