半导体封装模块、导电连接元件及其制造方法与流程

本发明涉及一种电子封装模块及其导电连接元件,特别涉及一种半导体封装模块的导电连接元件及其制造方法。

背景技术:

1、当半导体封装模块包含两层以上的线路基板时,必须通过设置于线路基板之间的导电连接元件,例如中介元件(interposer),来电性连接这些线路基板。现今所采用的中介元件主要有两种:邮票孔(stamp hole)形式的印刷电路板以及排针连接器(pin header)。邮票孔形式的印刷电路板的侧表面具有多个导电通孔的截面,这些导电通孔的截面可以作为线路基板之间互相电性连接的通路。由于导电通孔的截面凹凸不平,故在半导体封装模块的组装流程中,尚且需要通过导电胶或锡膏等材料进行填孔,以补平这些导电通孔的截面。

2、另一方面,排针连接器中各个排针的两端会凸出于排针连接器封装层的表面,故排针连接器的两侧也非平整面。在使用表面贴装(surface mount technology;smt)置件机台将排针连接器设置于线路基板上时,必须在排针端加上一层聚酯薄膜(mylar),以形成暂时性的平整表面,使smt置件机台的真空吸嘴得以顺利吸取排针连接器。根据上述,难以降低这两种中介元件在封装过程中的复杂程度以及制造成本。

3、除此之外,排针连接器外层的封装材料必须具有一定的厚度(至少0.3mm)。因此,在不增加排针连接器的厚度且其内部铜柱(pin)的截面积有限的情况下,排针连接器可承载的电流范围亦会受限。

技术实现思路

1、因此,本发明至少一实施例提供了一种半导体封装模块,可以提升此半导体封装模块内部的可承载电流。

2、本发明至少一实施例还提供了一种设置于上述的半导体封装模块中的导电连接元件及其制造方式,有利于简化导电连接元件的工艺。

3、本发明至少一实施例提供了一种导电连接元件,此导电连接元件包含多个图案化金属层以及一密封层。图案化金属层在一方向上互相堆叠,而密封层包覆图案化金属层。密封层具有相对两个第一表面,这些第一表面沿着前述的方向延伸。每一个图案化金属层的相对两个端面分别暴露于密封层的两个第一表面,且各图案化金属层的两个端面分别与对应的两个第一表面切齐。

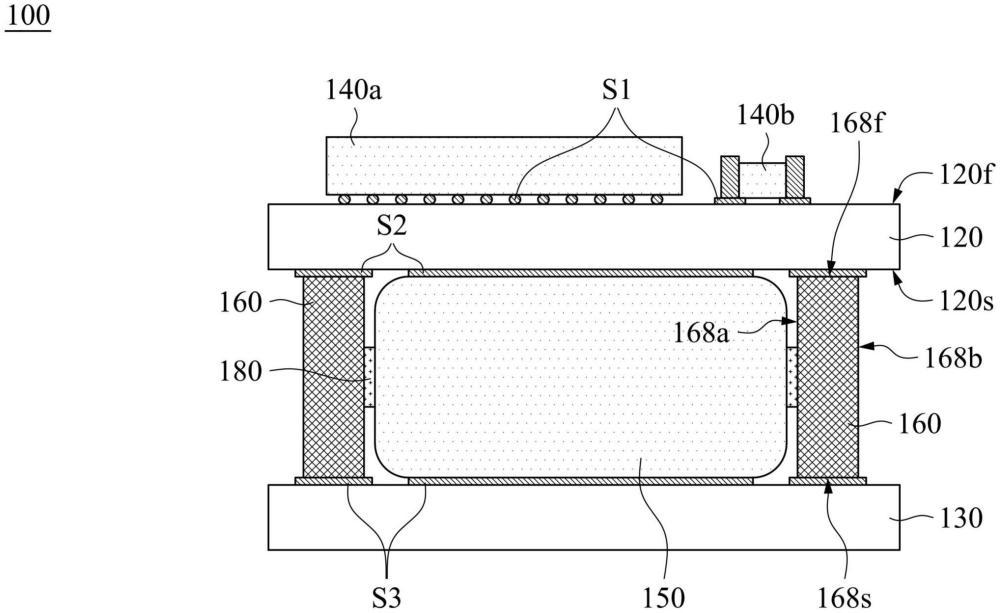

4、本发明至少一实施例还提供一种半导体封装模块,此半导体封装模块包含相对设置的第一线路基板与第二线路基板、一第一电子元件、一第二电子元件以及一上述导电连接元件。第二线路基板具有彼此相对的一第三表面与一第四表面。第一电子元件设置于第二线路基板的第三表面,并且电性连接至第二线路基板。第二电子元件设置于第二线路基板的第四表面,第二电子元件位于第一线路基板以及第二线路基板之间,并且电性连接至第一线路基板以及第二线路基板。导电连接元件设置于第二线路基板的第四表面,并且位于第一线路基板以及第二线路基板之间。导电连接元件中图案化金属层的端面分别连接第一线路基板以及第二线路基板,且第一线路基板通过导电连接元件的图案化金属层而电性连接至第二线路基板。

5、本发明至少一实施例还提供一种导电连接元件的制造方法,包含提供多个初始图案化金属层;沿着初始图案化金属层的法线方向堆叠初始图案化金属层;在堆叠初始图案化金属层之后,在初始图案化金属层上形成一初始密封层,此初始密封层包覆初始图案化金属层;以及在形成初始密封层之后,切割初始密封层以及初始图案化金属层,以形成一密封层以及多个图案化金属层,且密封层具有相对两个第一表面,而第一表面沿着前述法线方向延伸。每一个图案化金属层的相对两个端面分别暴露于密封层的相对两个第一表面,各图案化金属层的两个端面分别与对应的两个第一表面切齐。

6、基于上述,本发明至少一实施例的导电连接元件包含多个互相堆叠的图案化金属层以及一层包覆这些图案化金属层的密封层,此密封层用以固定这些图案化金属层,以使图案化金属层不易移位。由于堆叠后的图案化金属层不易移位,在导电连接元件的制造过程中,得以在不影响图案化金属层固定的前提下缩减密封层的厚度。如此一来,当导电连接元件厚度不变时,可以增加导电连接元件中的图案化金属层的厚度,进而提高导电连接元件的可承载电流。

技术特征:

1.一种导电连接元件,其特征在于,包含:

2.如权利要求1所述的导电连接元件,其特征在于,所述图案化金属层的每一者为一导线架。

3.如权利要求2所述的导电连接元件,其特征在于,所述导线架的每一者包含:

4.如权利要求3所述的导电连接元件,其特征在于,各所述图案化金属层的所述导线的相邻两者之间具有一间距,而所述导线的所述宽度与所述间距的比值大于1.0。

5.如权利要求4所述的导电连接元件,其特征在于,所述导线的相邻两者之间的所述间距小于0.3mm。

6.如权利要求1至5中任一所述的导电连接元件,其特征在于,所述密封层还具有两个相对的第二表面,所述第二表面邻接于所述第一表面,其中相邻于所述第二表面的所述图案化金属层分别具有一平面,且所述平面与所述第二表面之间的最小距离小于0.2mm。

7.如权利要求6所述的导电连接元件,其特征在于,所述图案化金属层的其中一者的所述平面暴露于所述密封层的所述第二表面的其中一者。

8.一种半导体封装模块,其特征在于,包含:

9.如权利要求8所述的半导体封装模块,其特征在于,还包含:

10.一种导电连接元件的制造方法,其特征在于,包含:

技术总结

提供了半导体封装模块、导电连接元件及其制造方法。导电连接元件包含多个图案化金属层以及密封层。图案化金属层在一方向上互相堆叠,而具有相对两个表面的密封层包覆图案化金属层。这些表面沿着图案化金属层堆叠的方向而延伸,每一个图案化金属层的相对两个端面分别暴露于密封层的相对两个表面,且各图案化金属层的端面分别与密封层的相对两个表面切齐。如此一来,得以提升半导体封装模块内部的可承载电流。

技术研发人员:沈里正,廖国宪,蔡弘毅,汪朝轩

受保护的技术使用者:环鸿电子(昆山)有限公司

技术研发日:

技术公布日:2024/10/31

- 还没有人留言评论。精彩留言会获得点赞!