一种半导体器件结构及其制备方法与流程

本发明属于半导体,涉及一种半导体器件结构及其制备方法。

背景技术:

1、随着半导体技术的发展,gan(氮化镓)基的hemt(high electron mobilitytransistors,高电子迁移率晶体管)因其高电子迁移率、高击穿电压和良好的热稳定性而在高频、高功率应用中显示出巨大的潜力。然而,gan材料在生长过程中不可避免地引入了大量位错和缺陷,这些缺陷不仅影响了器件的性能,还导致了栅电极漏电现象,进而引发了电流崩塌问题,限制了gan hemt在高性能电子设备中的应用。

2、栅电极漏电现象主要源于gan材料表面的电荷复合,这些表面态与栅电极相互作用,导致电流在栅极电压控制之外的非预期路径上流动,这种现象被称为栅极电流泄漏。栅极电流泄漏不仅降低了器件的开关速度,还增加了功耗,影响了器件的整体性能和可靠性。为了解决这一问题,研究者们尝试了多种方法,其中包括使用al2o3、si3n4和sio2等介质材料作为钝化层,以减少表面态的影响并抑制栅电极漏电。尽管这些介质钝化层在减少栅极电流泄漏方面取得了一定的进展,但现有的解决方案仍存在局限性。介质层的制备工艺需要精确控制,以确保其均匀性和完整性,任何不均匀或缺陷都可能导致漏电问题。而界面特性的不匹配可能导致电荷陷阱的形成,影响钝化效果,进一步加剧漏电。此外,介质层的化学稳定性和热稳定性也是影响其长期性能的关键因素。

3、因此,如何在增强钝化效果的同时降低栅电极漏电,进而提升gan hemt的性能和可靠性,成为本领域技术人员亟待解决的一个重要技术问题。

4、应该注意,上面对技术背景的介绍只是为了方便对本申请的技术方案进行清楚、完整的说明,并方便本领域技术人员的理解而阐述的。不能仅仅因为这些方案在本申请的背景技术部分进行了阐述而认为上述技术方案为本领域技术人员所公知。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种半导体器件结构及其制备方法,用于解决现有技术中gan hemt中的栅电极漏电和钝化层性能不足的问题。

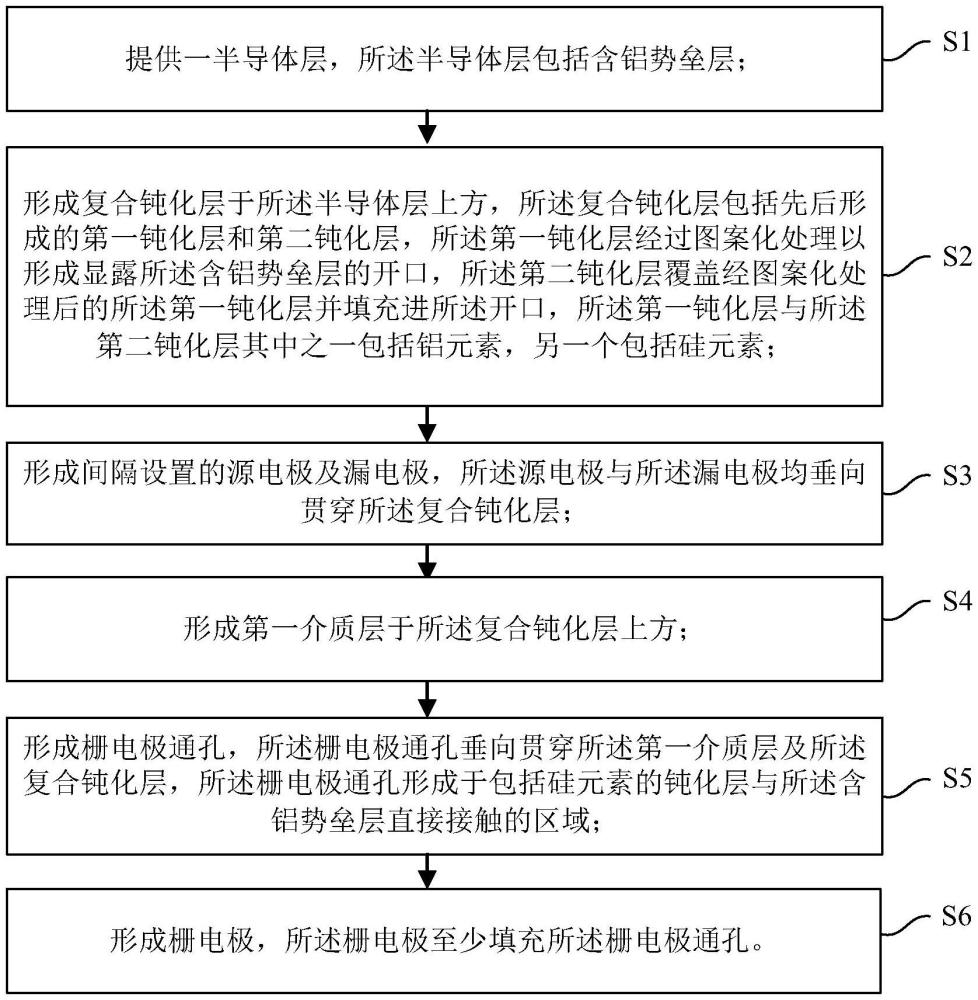

2、为实现上述目的及其他相关目的,本发明提供一种半导体器件结构的制备方法,包括以下步骤:

3、提供一半导体层,所述半导体层包括含铝势垒层;

4、形成复合钝化层于所述半导体层上方,所述复合钝化层包括先后形成的第一钝化层和第二钝化层,所述第一钝化层经过图案化处理以形成显露所述含铝势垒层的开口,所述第二钝化层覆盖经图案化处理后的所述第一钝化层并填充进所述开口,所述第一钝化层与所述第二钝化层其中之一包括铝元素,另一个包括硅元素;

5、形成间隔设置的源电极及漏电极,所述源电极与所述漏电极均垂向贯穿所述复合钝化层;

6、形成第一介质层于所述复合钝化层上方;

7、形成栅电极通孔,所述栅电极通孔垂向贯穿所述第一介质层及所述复合钝化层,所述栅电极通孔形成于包括硅元素的钝化层与所述含铝势垒层直接接触的区域;

8、形成栅电极,所述栅电极至少填充所述栅电极通孔。

9、可选地,所述第一钝化层包括铝元素,所述第二钝化层包括硅元素,所述栅电极通孔位于所述开口所在区域。

10、可选地,所述源电极与所述漏电极均避开所述开口区域,或者所述源电极位于所述开口所在区域,所述漏电极避开所述开口区域。

11、可选地,所述第一钝化层包括硅元素,所述第二钝化层包括铝元素,所述栅电极通孔避开所述开口所在区域。

12、可选地,所述源电极与所述漏电极均位于所述开口区域,或者所述源电极避开所述开口所在区域,所述漏电极位于所述开口区域。

13、可选地,所述复合钝化层还包括第三钝化层,所述第三钝化层覆盖所述第二钝化层。

14、可选地,还包括以下步骤:

15、形成第二介质层于所述第一介质层上,所述第二介质层覆盖所述栅电极;

16、图案化所述第二介质层,以形成通孔结构,所述通孔结构显露所述源电极、所述漏电极及所述栅电极的顶部;

17、形成互连金属层,所述互连金属层覆盖所述第二介质层并填充进所述通孔结构;

18、图案化所述互连金属层以形成引线结构。

19、可选地,所述半导体层还包括位于所述含铝势垒层下方,自下而上依次叠置的衬底、缓冲层及沟道层,所述沟道层朝向所述含铝势垒层的一侧具有二维电子气。

20、可选地,所述第一钝化层与所述第二钝化层其中之一的材质包括氮化铝、氧化铝及氧化铝氮化物中的至少一种,另一个的材质包括氮化硅及二氧化硅中的至少一种。

21、本发明还提供一种半导体器件结构,包括:

22、半导体层,所述半导体层包括含铝势垒层;

23、复合钝化层,位于所述半导体层上方,所述复合钝化层包括先后形成的第一钝化层和第二钝化层,所述第一钝化层经过图案化处理以形成显露所述含铝势垒层的开口,所述第二钝化层覆盖经图案化处理后的所述第一钝化层并填充进所述开口,所述第一钝化层与所述第二钝化层其中之一包括铝元素,另一个包括硅元素;

24、源电极及漏电极,所述源电极与所述漏电极间隔设置,且所述源电极与所述漏电极均垂向贯穿所述复合钝化层;

25、第一介质层,位于所述复合钝化层上方;

26、栅电极,所述栅电极垂向贯穿所述第一介质层及所述复合钝化层,所述栅电极位于包括硅元素的钝化层与所述含铝势垒层直接接触的区域。

27、如上所述,本发明的半导体器件结构及其制备方法,通过在包括含铝势垒层的半导体层上形成复合钝化层,该复合钝化层包括第一钝化层和第二钝化层,第一钝化层经图案化处理后形成有显露含铝势垒层的开口,第二钝化层覆盖第一钝化层并填充该开口。第一钝化层与第二钝化层其中之一包括铝元素,另一个包括硅元素,而栅电极形成于包括硅元素的钝化层与含铝势垒层直接接触的区域。这种复合钝化层的设计,有效减少了含铝势垒层表面的悬挂键和表面态,实现了对半导体器件结构的高效钝化。同时有效避免了后续栅电极通孔及源极接触孔制备过程中对含铝势垒层造成损伤,显著降低漏电风险,提高了半导体器件的电气性能和可靠性。

技术特征:

1.一种半导体器件结构的制备方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的半导体器件结构的制备方法,其特征在于:所述第一钝化层包括铝元素,所述第二钝化层包括硅元素,所述栅电极通孔位于所述开口所在区域。

3.根据权利要求2所述的半导体器件结构的制备方法,其特征在于:所述源电极与所述漏电极均避开所述开口区域,或者所述源电极位于所述开口所在区域,所述漏电极避开所述开口区域。

4.根据权利要求1所述的半导体器件结构的制备方法,其特征在于:所述第一钝化层包括硅元素,所述第二钝化层包括铝元素,所述栅电极通孔避开所述开口所在区域。

5.根据权利要求4所述的半导体器件结构的制备方法,其特征在于:所述源电极与所述漏电极均位于所述开口区域,或者所述源电极避开所述开口所在区域,所述漏电极位于所述开口区域。

6.根据权利要求4所述的半导体器件结构的制备方法,其特征在于:所述复合钝化层还包括第三钝化层,所述第三钝化层覆盖所述第二钝化层。

7.根据权利要求1所述的半导体器件结构的制备方法,其特征在于,还包括以下步骤:

8.根据权利要求1所述的半导体器件结构的制备方法,其特征在于:所述半导体层还包括位于所述含铝势垒层下方,自下而上依次叠置的衬底、缓冲层及沟道层,所述沟道层朝向所述含铝势垒层的一侧具有二维电子气。

9.根据权利要求1所述的半导体器件结构的制备方法,其特征在于:所述第一钝化层与所述第二钝化层其中之一的材质包括氮化铝、氧化铝及氧化铝氮化物中的至少一种,另一个的材质包括氮化硅及二氧化硅中的至少一种。

10.一种半导体器件结构,其特征在于,包括:

技术总结

本发明提供一种半导体器件结构及其制备方法,通过在包括含铝势垒层的半导体层上形成复合钝化层,该复合钝化层包括第一钝化层和第二钝化层,第一钝化层经图案化处理后形成有显露含铝势垒层的开口,第二钝化层覆盖第一钝化层并填充该开口。第一钝化层与第二钝化层其中之一包括铝元素,另一个包括硅元素,而栅电极形成于包括硅元素的钝化层与含铝势垒层直接接触的区域。这种复合钝化层的设计,有效减少了含铝势垒层表面的悬挂键和表面态,实现了对半导体器件结构的高效钝化。同时有效避免了后续栅电极通孔及源极接触孔制备过程中对含铝势垒层造成损伤,显著降低漏电风险,提高了半导体器件的电气性能和可靠性。

技术研发人员:张安邦

受保护的技术使用者:上海新微半导体有限公司

技术研发日:

技术公布日:2024/10/28

- 还没有人留言评论。精彩留言会获得点赞!