半导体结构及其形成方法与流程

本申请涉及半导体,尤其涉及一种半导体结构及其形成方法。

背景技术:

1、碳化硅器件(sic mosfet)是一种区别于传统硅衬底的半导体器件。目前对于碳化硅器件的形成工艺仍然存在缺陷,导致器件性能和可靠性得不到保证。

2、因此,有必要提供更有效、更可靠的技术方案。

技术实现思路

1、本申请提供一种半导体结构及其形成方法,可以自对准形成第一金属硅化物,提高第一金属硅化物的对准精度;刻蚀部分第三掺杂区后形成第一金属硅化物和第二金属硅化物,增加第一金属硅化物和第二金属硅化物的接触面积,提高第一金属硅化物和第二金属硅化物的电连接性;在第一掺杂区之间和第三掺杂区之间形成第二掺杂区过渡,提高电场分布,提高器件性能和可靠性。

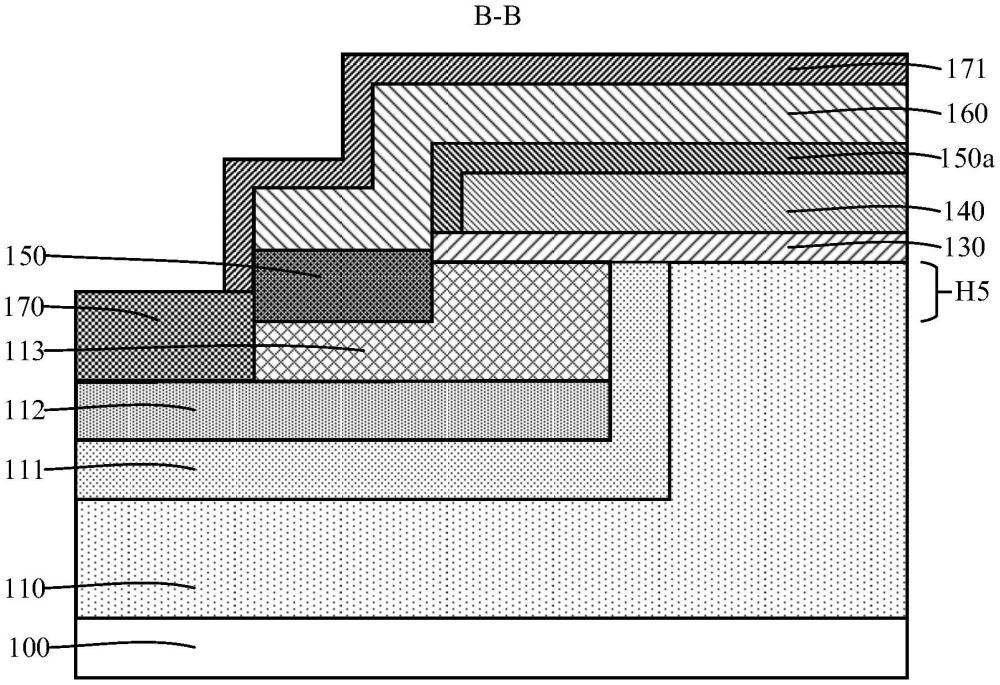

2、本申请的一个方面提供一种半导体结构的形成方法,包括:提供半导体衬底,所述半导体衬底表面形成有外延层,所述外延层中形成有第一掺杂区、位于所述第一掺杂区中的第二掺杂区以及位于所述第二掺杂区中的第三掺杂区;在所述外延层表面形成暴露部分所述第三掺杂区的栅极氧化层和栅极层;刻蚀暴露的所述第三掺杂区形成第一开口;在所述第一开口中形成第一金属硅化物并在所述栅极层表面形成第一金属层;在所述第一金属硅化物和第一金属层表面形成层间介质层。

3、在本申请的一些实施例中,所述半导体衬底的材料包括碳化硅,所述外延层的材料包括掺杂的碳化硅,所述栅极层的材料包括掺杂的多晶硅。

4、在本申请的一些实施例中,所述第一掺杂区的掺杂类型和所述外延层的掺杂类型相反,所述第二掺杂区的掺杂类型和所述第一掺杂区的掺杂类型相同,所述第三掺杂区的掺杂类型和所述第二掺杂区的掺杂类型相反,所述栅极层的掺杂类型与所述外延层的掺杂类型相同。

5、在本申请的一些实施例中,所述外延层的深度为4至40微米,所述第一掺杂区的深度为0.6至2微米,所述第二掺杂区的深度为0.8至2.4微米,所述第三掺杂区的深度为0.2至0.4微米。

6、在本申请的一些实施例中,所述栅极氧化层的长度大于所述栅极层的长度。

7、在本申请的一些实施例中,所述栅极层的表面积大于所述第一开口底部的第三掺杂区的表面积。

8、在本申请的一些实施例中,所述第一开口的深度为0.1至0.2微米。

9、在本申请的一些实施例中,所述第一开口中的第一金属硅化物的深度为0.1至1微米。

10、在本申请的一些实施例中,所述第一开口中的第一金属硅化物的顶面高于所述栅极氧化层的底面低于所述栅极氧化层的顶面。

11、在本申请的一些实施例中,所述半导体衬底包括第一区域和第二区域,形成所述层间介质层后还包括:刻蚀所述第二区域的部分所述层间介质层和第一金属硅化物形成暴露所述第三掺杂区的第二开口;在所述第二开口中形成第二金属硅化物,所述第二金属硅化物连接至所述第三掺杂区下方的第二掺杂区。

12、本申请的另一个方面还提供一种半导体结构,包括:半导体衬底,所述半导体衬底表面形成有外延层,所述外延层中形成有第一掺杂区、位于所述第一掺杂区中的第二掺杂区以及位于所述第二掺杂区中的第三掺杂区,所述外延层表面形成有暴露部分所述第三掺杂区的栅极氧化层和栅极层;第一开口,位于所述暴露的第三掺杂区中;第一金属硅化物,位于所述第一开口中;层间介质层,位于所述第一金属硅化物表面。

13、在本申请的一些实施例中,所述半导体衬底的材料包括碳化硅,所述外延层的材料包括掺杂的碳化硅,所述栅极层的材料包括掺杂的多晶硅。

14、在本申请的一些实施例中,所述第一掺杂区的掺杂类型和所述外延层的掺杂类型相反,所述第二掺杂区的掺杂类型和所述第一掺杂区的掺杂类型相同,所述第三掺杂区的掺杂类型和所述第二掺杂区的掺杂类型相反,所述栅极层的掺杂类型与所述外延层的掺杂类型相同。

15、在本申请的一些实施例中,所述外延层的深度为4至40微米,所述第一掺杂区的深度为0.6至2微米,所述第二掺杂区的深度为0.8至2.4微米,所述第三掺杂区的深度为0.2至0.4微米。

16、在本申请的一些实施例中,所述栅极氧化层的长度大于所述栅极层的长度。

17、在本申请的一些实施例中,所述栅极层的表面积大于所述第一开口底部的第三掺杂区的表面积。

18、在本申请的一些实施例中,所述第一开口的深度为0.1至0.2微米。

19、在本申请的一些实施例中,所述第一开口中的第一金属硅化物的深度为0.1至1微米。

20、在本申请的一些实施例中,所述第一开口中的第一金属硅化物的顶面高于所述栅极氧化层的底面低于所述栅极氧化层的顶面。

21、在本申请的一些实施例中,所述半导体衬底包括第一区域和第二区域,所述第二区域的层间介质层和第一金属硅化物中还形成有暴露所述第三掺杂区的第二开口;所述第二开口中形成有第二金属硅化物,所述第二金属硅化物连接至所述第三掺杂区下方的第二掺杂区。

22、本申请提供一种半导体结构及其形成方法,可以自对准形成第一金属硅化物,提高第一金属硅化物的对准精度;刻蚀部分第三掺杂区后形成第一金属硅化物和第二金属硅化物,增加第一金属硅化物和第二金属硅化物的接触面积,提高第一金属硅化物和第二金属硅化物的电连接性;在第一掺杂区之间和第三掺杂区之间形成第二掺杂区过渡,提高电场分布,提高器件性能和可靠性。

技术特征:

1.一种半导体结构的形成方法,其特征在于,包括:

2.如权利要求1所述的半导体结构的形成方法,其特征在于,所述半导体衬底的材料包括碳化硅,所述外延层的材料包括掺杂的碳化硅,所述栅极层的材料包括掺杂的多晶硅。

3.如权利要求1所述的半导体结构的形成方法,其特征在于,所述第一掺杂区的掺杂类型和所述外延层的掺杂类型相反,所述第二掺杂区的掺杂类型和所述第一掺杂区的掺杂类型相同,所述第三掺杂区的掺杂类型和所述第二掺杂区的掺杂类型相反,所述栅极层的掺杂类型与所述外延层的掺杂类型相同。

4.如权利要求1所述的半导体结构的形成方法,其特征在于,所述外延层的深度为4至40微米,所述第一掺杂区的深度为0.6至2微米,所述第二掺杂区的深度为0.8至2.4微米,所述第三掺杂区的深度为0.2至0.4微米。

5.如权利要求1所述的半导体结构的形成方法,其特征在于,所述栅极氧化层的长度大于所述栅极层的长度。

6.如权利要求1所述的半导体结构的形成方法,其特征在于,所述栅极层的表面积大于所述第一开口底部的第三掺杂区的表面积。

7.如权利要求1所述的半导体结构的形成方法,其特征在于,所述第一开口的深度为0.1至0.2微米。

8.如权利要求1所述的半导体结构的形成方法,其特征在于,所述第一开口中的第一金属硅化物的深度为0.1至1微米。

9.如权利要求1所述的半导体结构的形成方法,其特征在于,所述第一开口中的第一金属硅化物的顶面高于所述栅极氧化层的底面低于所述栅极氧化层的顶面。

10.如权利要求1所述的半导体结构的形成方法,其特征在于,所述半导体衬底包括第一区域和第二区域,形成所述层间介质层后还包括:

11.一种半导体结构,其特征在于,包括:

12.如权利要求11所述的半导体结构,其特征在于,所述半导体衬底的材料包括碳化硅,所述外延层的材料包括掺杂的碳化硅,所述栅极层的材料包括掺杂的多晶硅。

13.如权利要求11所述的半导体结构,其特征在于,所述第一掺杂区的掺杂类型和所述外延层的掺杂类型相反,所述第二掺杂区的掺杂类型和所述第一掺杂区的掺杂类型相同,所述第三掺杂区的掺杂类型和所述第二掺杂区的掺杂类型相反,所述栅极层的掺杂类型与所述外延层的掺杂类型相同。

14.如权利要求11所述的半导体结构,其特征在于,所述外延层的深度为4至40微米,所述第一掺杂区的深度为0.6至2微米,所述第二掺杂区的深度为0.8至2.4微米,所述第三掺杂区的深度为0.2至0.4微米。

15.如权利要求11所述的半导体结构,其特征在于,所述栅极氧化层的长度大于所述栅极层的长度。

16.如权利要求11所述的半导体结构,其特征在于,所述栅极层的表面积大于所述第一开口底部的第三掺杂区的表面积。

17.如权利要求11所述的半导体结构,其特征在于,所述第一开口的深度为0.1至0.2微米。

18.如权利要求11所述的半导体结构,其特征在于,所述第一开口中的第一金属硅化物的深度为0.1至1微米。

19.如权利要求11所述的半导体结构,其特征在于,所述第一开口中的第一金属硅化物的顶面高于所述栅极氧化层的底面低于所述栅极氧化层的顶面。

20.如权利要求11所述的半导体结构,其特征在于,所述半导体衬底包括第一区域和第二区域,所述第二区域的层间介质层和第一金属硅化物中还形成有暴露所述第三掺杂区的第二开口;所述第二开口中形成有第二金属硅化物,所述第二金属硅化物连接至所述第三掺杂区下方的第二掺杂区。

技术总结

本申请提供半导体结构及其形成方法,所述半导体结构包括:半导体衬底,所述半导体衬底表面形成有外延层,所述外延层中形成有第一掺杂区、位于所述第一掺杂区中的第二掺杂区以及位于所述第二掺杂区中的第三掺杂区,所述外延层表面形成有暴露部分所述第三掺杂区的栅极氧化层和栅极层;第一开口,位于所述暴露的第三掺杂区中;第一金属硅化物,位于所述第一开口中;层间介质层,位于所述第一金属硅化物表面。本申请提供一种半导体结构及其形成方法,可以提高第一金属硅化物的对准精度;提高第一金属硅化物和第二金属硅化物的电连接性;提高电场分布,提高器件性能和可靠性。

技术研发人员:李浩南,彭定康,李晓冈,张永杰

受保护的技术使用者:飞锃半导体(上海)有限公司

技术研发日:

技术公布日:2024/11/4

- 还没有人留言评论。精彩留言会获得点赞!