芯片镀金层的等离子清洗方法、芯片封装方法及封装结构与流程

本公开实施例属于半导体封装,具体涉及一种芯片镀金层的等离子清洗方法、芯片封装方法及封装结构。

背景技术:

1、2.5d高功耗的芯片封装产品在工作过程中会产生大量的热能,高功耗的产品在封装过程中需要使用金属铟和芯片表面及散热盖表面完成焊接,来保证高功耗的产品在使用过程中的热能得到及时的散发。金属铟和金的焊接效果最好,需要在芯片背面镀金来完成焊接。芯片背面镀金区域很容易在封装的底部填胶过程中产生树脂的污染,而影响铟片和芯片背面的焊接,铟片和芯片背面焊接不良会影响终端测试的良率。

2、为了解决如上问题,目前行业内没有有效的方法来解决此问题,只能通过底部填充胶水固化前目检来检查芯片背面的树脂脏污情况和传统的用无尘布擦拭的方法来避免问题发生,这种传统方法目前遇到的问题是:

3、1)传统的无尘布擦拭的方法效率低并且效果不好。

4、2)胶水固化前用传统的无尘布擦拭的方法会有二次胶水污染的风险。

5、3)需要大量的人力物力来解决。

6、4)有擦拭不干净,异常逃脱导致的客户投诉的风险。

7、针对上述问题,有必要提出一种设计合理且有效解决上述问题的芯片镀金层的等离子清洗方法、芯片封装方法及封装结构。

技术实现思路

1、本公开实施例旨在至少解决现有技术中存在的技术问题之一,提供一种芯片镀金层的等离子清洗方法、芯片封装方法及封装结构。

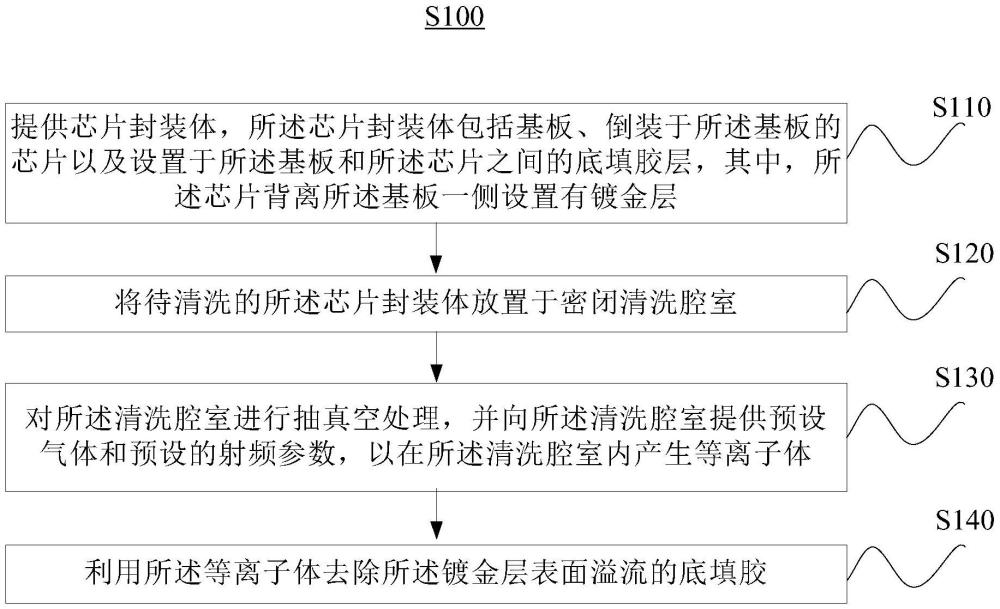

2、本公开实施例的一方面提供一种芯片镀金层的等离子清洗方法,所述等离子清洗方法包括:

3、提供芯片封装体,所述芯片封装体包括基板、倒装于所述基板的芯片以及设置于所述基板和所述芯片之间的底填胶层,其中,所述芯片背离所述基板一侧设置有镀金层;

4、将待清洗的所述芯片封装体放置于密闭清洗腔室;

5、对所述清洗腔室进行抽真空处理,并向所述清洗腔室提供预设气体和预设的射频参数,以在所述清洗腔室内产生等离子体;

6、利用所述等离子体去除所述镀金层表面溢流的底填胶。

7、可选的,所述射频参数包括射频功率和射频持续时间;

8、所述射频功率范围为350w~450w,且所述射频持续时间范围为50s~80s。

9、可选的,所述射频功率为400w,且所述射频持续时间为65s。

10、可选的,所述预设气体包括氩氧混合气体。

11、可选的,所述氩氧混合气体中氦气和氧气的混合比例范围为(8.5~9.5):1。

12、可选的,所述氩氧混合气体中氦气和氧气的混合比例为9:1。

13、可选的,所述清洗腔室在所述抽真空处理后的压力范围为10pa~30pa。

14、可选的,所述利用所述等离子体去除所述镀金层表面溢流的底填胶,包括:

15、利用所述等离子体对所述镀金层的表面进行物理轰击,以使所述镀金层表面溢流的底填胶变为气态物质脱离所述镀金层表面;

16、对所述清洗腔室再次进行抽真空,以将所述气态物质排出至所述清洗腔室外,以去除所述镀金层表面溢流的底填胶。

17、本公开实施例的另一方面提供一种芯片封装方法,所述封装方法包括:

18、将芯片倒装于基板,其中,所述芯片背离所述基板的一侧设置有镀金层;

19、对所述芯片和所述基板进行回流焊接,进行助焊剂清洗;

20、在所述芯片和所述基板之间进行底填胶填充;

21、采用等离子清洗方法对完成底填胶填充的所述基板和所述芯片进行清洗,以去除所述镀金层表面溢流的底填胶;其中,

22、所述等离子清洗方法采用前文所述的等离子清洗方法;

23、在所述镀金层上依次设置金属散热层和散热盖,完成芯片的封装。

24、本公开实施例的另一方面提供一种芯片封装结构,包括:

25、基板;

26、芯片,所述芯片倒装于所述基板,其中,所述芯片背离所述基板的一侧设置有镀金层;

27、底填胶层,夹设于所述基板和所述芯片之间;

28、金属散热层,设置于所述镀金层背离所述芯片的一侧;

29、散热盖,设置于所述金属散热层,且所述散热盖的边缘区域固定于所述基板的边缘区域;其中,

30、所述镀金层采用前文所述的等离子清洗方法进行清洗。

31、本公开实施例的芯片镀金层的等离子清洗方法、芯片封装方法及封装结构,采用等离子清洗方法对芯片背面的镀金层进行清洗,可以有效的去除镀金层表面溢流的底填胶,提升了镀金层清洗的效率和效果,提升芯片镀金层和金属铟的焊接性能,提高芯片封装体的可靠性,提高终端测试良率;采用等离子清洗方法去除镀金层表面的底填胶不会存在二次胶水污染的风险,减少了人力物力,节约了成本。

技术特征:

1.一种芯片镀金层的等离子清洗方法,其特征在于,所述等离子清洗方法包括:

2.根据权利要求1所述的等离子清洗方法,其特征在于,所述射频参数包括射频功率和射频持续时间;

3.根据权利要求2所述的等离子清洗方法,其特征在于,所述射频功率为400w,且所述射频持续时间为65s。

4.根据权利要求1至3任一项所述的等离子清洗方法,其特征在于,所述预设气体包括氩氧混合气体。

5.根据权利要求4所述的等离子清洗方法,其特征在于,所述氩氧混合气体中氦气和氧气的混合比例范围为(8.5~9.5):1。

6.根据权利要求5所述的等离子清洗方法,其特征在于,所述氩氧混合气体中氦气和氧气的混合比例为9:1。

7.根据权利要求1至3任一项所述的等离子清洗方法,其特征在于,所述清洗腔室在所述抽真空处理后的压力范围为10pa~30pa。

8.根据权利要求1至3任一项所述的等离子清洗方法,其特征在于,所述利用所述等离子体去除所述镀金层表面溢流的底填胶,包括:

9.一种芯片封装方法,其特征在于,所述封装方法包括:

10.一种芯片封装结构,其特征在于,包括:

技术总结

本公开实施例提供一种芯片镀金层的等离子清洗方法、芯片封装方法及封装结构,该方法包括:提供芯片封装体,芯片封装体包括基板、倒装于基板的芯片以及设置于基板和芯片之间的底填胶层,其中,芯片背离基板一侧设置有镀金层;将待清洗的芯片封装体放置于密闭清洗腔室;对所述清洗腔室进行抽真空处理,并向清洗腔室提供预设气体和预设的射频参数,以在清洗腔室内产生等离子体;利用等离子体去除镀金层表面溢流的底填胶。该方法可以有效去除镀金层表面的底填胶,提升镀金层清洗的效率和效果,提升芯片镀金层和金属铟的焊接性能,提高芯片封装体的可靠性,提高终端测试良率;减少人力物力,节约成本。

技术研发人员:季洪虎,王冬冬,焦洁

受保护的技术使用者:通富超威(苏州)微电子有限公司

技术研发日:

技术公布日:2024/10/17

- 还没有人留言评论。精彩留言会获得点赞!