一种掩膜层及形成方法与流程

本发明涉及半导体,特别涉及一种掩膜层及形成方法。

背景技术:

1、在集成电路的制作过程中,需要执行多次图形化处理在半导体基片上形成期望的图案,每次图形化处理都需要使用掩膜版。掩膜版的平坦度影响光刻工艺窗口的精度,从而影响转印质量。

2、现有技术中,如图1所示,掩模材料会在刻涂之后的烘烤步骤因为收缩而导致最终所形成的硬掩膜层100表面不平整,尤其形成在沟槽上方的硬掩膜层100会出现较大厚度差,为此,在硬掩膜层100形成之后会在其表面形成一氧化层,而后对其进行机械研磨以实现平坦化,氧化层可以减小机械研磨时应力对硬掩膜层的影响。氧化层的沉积及机械研磨工艺均会导致工艺难度及成本增加。

技术实现思路

1、本发明的目的在于提供一种掩膜层及形成方法,以解决现有技术中的一个或多个问题。

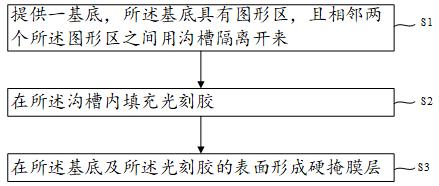

2、为解决上述技术问题,本发明提供一种掩膜层的形成方法,包括:

3、提供一基底,所述基底具有图形区,且相邻两个所述图形区之间用沟槽隔离开来;

4、在所述沟槽内填充光刻胶;以及,

5、在所述基底及所述光刻胶的表面形成硬掩膜层。

6、可选的,在所述的掩膜层的形成方法中,所述硬掩膜层包括soc膜层。

7、可选的,在所述的掩膜层的形成方法中,在所述沟槽内填充光刻胶的方法包括:

8、在所述基底上形成光刻胶层;以及,

9、对所述光刻胶层进行光刻,以去除所述光刻胶层除所述沟槽内的光刻胶以外的部分。

10、可选的,在所述的掩膜层的形成方法中,所述光刻胶为负光刻胶。

11、可选的,在所述的掩膜层的形成方法中,对所述光刻胶层进行光刻时,根据开口宽度是否大于或等于设定值来区分出所述沟槽及所述图形区的位置,并相应设计掩膜版。

12、可选的,在所述的掩膜层的形成方法中,所述根据开口宽度是否大于或等于设置来区分出所述沟槽及所述图形区的位置,并相应设计掩膜版包括:

13、若开口宽度大于或等于所述设定值,则划分为所述沟槽,与所述掩膜版的曝光区域相对应;

14、若开口宽度小于所述设定值,则划分为属于所述图形区,与所述掩膜版的非曝光区域相对应。

15、可选的,在所述的掩膜层的形成方法中,所述设定值为400nm。

16、可选的,在所述的掩膜层的形成方法中,在所述沟槽内填充的光刻胶的上表面不低于所述基底的上表面。

17、可选的,在所述的掩膜层的形成方法中,,还包括:执行光刻工艺,以图形化所述硬掩膜层。

18、本发明还提供一种掩膜层,所述掩膜层利用如前任一项所述的方法形成。

19、综上所述,本发明实提供的掩膜层及其形成方法包括:提供一基底,所述基底具有图形区,且相邻两个所述图形区之间用沟槽隔离开来;在所述沟槽内填充光刻胶;以及,在所述基底及所述光刻胶的表面形成硬掩膜层。本发明提供的方法,在形成硬掩膜层之前,先利用光刻胶填充沟槽,与现有技术相比,具有如下有益效果:

20、(1)可减小在对掩膜材料进行烘烤以形成硬掩膜层时,因掩膜材料收缩而导致沟槽上方的硬掩膜层出现的厚度差,提高掩膜平坦度,从而可以提高图案转移质量;

21、(2)可不必对硬掩膜层表面进行平坦化处理,因此可以省去因机械研磨所带来的成本。

技术特征:

1.一种掩膜层的形成方法,其特征在于,包括:

2.如权利要求1所述的掩膜层的形成方法,其特征在于,所述硬掩膜层包括soc膜层。

3.如权利要求1所述的掩膜层的形成方法,其特征在于,在所述沟槽内填充光刻胶的方法包括:

4.如权利要求3所述的掩膜层的形成方法,其特征在于,所述光刻胶为负光刻胶。

5.如权利要求4所述的掩膜层的形成方法,其特征在于,对所述光刻胶层进行光刻时,根据开口宽度是否大于或等于设定值来区分出所述沟槽及所述图形区的位置,并相应设计掩膜版。

6.如权利要求5所述的掩膜层的形成方法,其特征在于,所述根据开口宽度是否大于或等于设置来区分出所述沟槽及所述图形区的位置,并相应设计掩膜版包括:

7.如权利要求5所述的掩膜层的形成方法,其特征在于,所述设定值为400nm。

8.如权利要求1所述的掩膜层的形成方法,其特征在于,在所述沟槽内填充的光刻胶的上表面不低于所述基底的上表面。

9.如权利要求1所述的掩膜层的形成方法,其特征在于,还包括:执行光刻工艺,以图形化所述硬掩膜层。

10.一种掩膜层,其特征在于,所述掩膜层利用如权利要求1~9任一项所述的方法形成。

技术总结

本发明提供一种掩膜层及其形成方法包括:提供一基底,所述基底具有图形区,且相邻两个所述图形区之间用沟槽隔离开来;在所述沟槽内填充光刻胶;以及,在所述基底及所述光刻胶的表面形成硬掩膜层。即,本发明在形成硬掩膜层之前,先利用光刻胶填充沟槽,如此,可减小在对掩膜材料进行烘烤以形成硬掩膜层时,因掩膜材料收缩而导致沟槽上方的硬掩膜层出现的厚度差,提高掩膜平坦度,从而可以提高图案转移质量,另外,可不必对硬掩膜层表面进行平坦化处理,因此可以省去因机械研磨所带来的成本。

技术研发人员:尤智,张业利

受保护的技术使用者:杭州积海半导体有限公司

技术研发日:

技术公布日:2024/8/27

- 还没有人留言评论。精彩留言会获得点赞!