半导体结构的制备方法及半导体结构与流程

本发明涉及半导体制造,特别是涉及一种半导体结构的制备方法及半导体结构。

背景技术:

1、在半导体后段的钝化层工艺中,通常使用一层铝衬垫作为晶圆器件和外部环境的连线端,连线端作为测试电性和封端的引线点。通常情况下,一般采用在铝衬垫上直接涂布光刻胶进行光刻和刻蚀图案,由于光刻胶和铝衬垫之间的粘附性不匹配,很容易导致图案的剥离以及后期刻蚀的图案不清晰和不完全的问题。在传统的制作工艺中,通常采用在铝衬垫上增加顶层黏附层来连接光刻胶和铝衬垫。

2、然而,生长顶层黏附层后的结构表面易产生大量的鼓包状缺陷。鼓包状缺陷作为铝衬垫表面常见的缺陷类型之一,会对后续的光刻和刻蚀产生不利影响。例如,鼓包状缺陷可能会造成刻蚀图案的不清晰和不完全,继而导致栅极,源漏极以及连线处的短路等,使得半导体产品的生产良率降低。

3、因此,降低鼓包状缺陷的产生是目前半导体制造技术领域亟需解决的问题。

技术实现思路

1、基于此,本申请实施例提供了一种半导体结构的制备方法及半导体结构,至少能够有效避免鼓泡状缺陷。

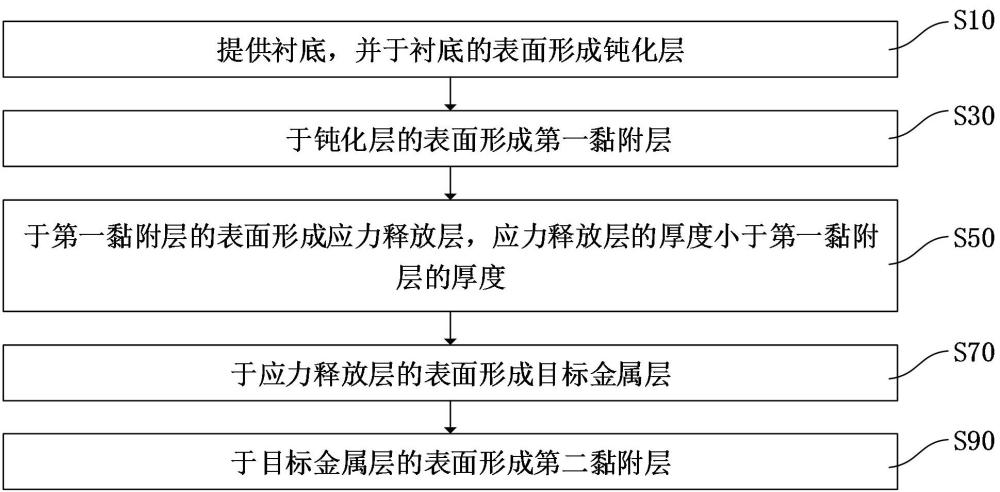

2、根据一些实施例,本申请提供了一种半导体结构的制备方法,半导体结构的制备方法包括:提供衬底,并于衬底的表面形成钝化层;于钝化层的表面形成第一黏附层;于第一黏附层的表面形成应力释放层,应力释放层的厚度小于第一黏附层的厚度;于应力释放层的表面形成目标金属层;于目标金属层的表面形成第二黏附层。

3、上述半导体结构的制备方法中,于钝化层的表面形成的第一黏附层能够增加钝化层与后续结构的粘合度,第一黏附层还具有阻挡作用。于第一黏附层的表面形成应力释放层能够有效降低晶粒大小,便于目标金属层受热后应力在晶界的释放,以抑制目标金属层向上释放应力的趋势,由于应力释放层的厚度小于第一黏附层的厚度,能够在不影响整体结构厚度的前提下,有效地避免鼓泡状缺陷。于目标金属层的表面形成第二黏附层,能够有效提升目标金属层与第二黏附层之间的粘附性,以降低鼓泡状缺陷,从而提升目标金属层的形貌,以提高半导体产品的生产良率。

4、在一些实施例中,应力释放层的厚度范围为60a至80a。

5、在一些实施例中,应力释放层的材料包括金属钛。

6、在一些实施例中,于所述目标金属层的表面形成第二黏附层,以预设沉积速度于目标金属层的表面采用预设沉积工艺形成第二黏附层。

7、在一些实施例中,预设沉积工艺包括单频高频射频化学气相沉积工艺;及/或预设沉积速度的范围为20a/s至40a/s。

8、在一些实施例中,第二黏附层的厚度范围为200a至300a。

9、在一些实施例中,第一黏附层的材料包括氮化钽;及/或第二黏附层的材料包括硅酸乙酯。

10、在一些实施例中,于应力释放层的表面形成目标金属层,包括:采用一次性沉积工艺于应力释放层的表面形成目标金属层。

11、根据一些实施例,本申请还提供了一种半导体结构,半导体结构包括衬底及位于衬底表面的钝化层,第一黏附层,应力释放层,目标金属层以及第二黏附层;第一黏附层位于钝化层的表面;应力释放层位于第一黏附层的表面,应力释放层的厚度小于第一黏附层的厚度;目标金属层位于应力释放层的表面;第二黏附层位于所述目标金属层表面。

12、上述半导体结构中,位于钝化层的表面的第一黏附层能够增加钝化层与后续结构的粘合度,第一黏附层还具有阻挡作用。位于第一黏附层的表面的应力释放层能够有效降低晶粒大小,便于目标金属层受热后应力在晶界的释放,以抑制目标金属层向上释放应力的趋势,由于应力释放层的厚度小于第一黏附层的厚度,能够在不影响整体结构厚度的前提下,有效地避免鼓泡状缺陷位于目标金属层表面的第二黏附层,能够有效提升其与目标金属层之间的粘附性,以降低鼓泡状缺陷,从而提升目标金属层的形貌,以提高半导体产品的生产良率。

13、在一些实施例中,第二黏附层以预设沉积速度采用预设沉积工艺形成。

技术特征:

1.一种半导体结构的制备方法,其特征在于,包括:

2.根据权利要求1所述的半导体结构的制备方法,其特征在于,所述应力释放层的厚度范围为60a至80a。

3.根据权利要求1所述的半导体结构的制备方法,其特征在于,所述应力释放层的材料包括金属钛。

4.根据权利要求1所述的半导体结构的制备方法,其特征在于,于所述目标金属层的表面形成第二黏附层,包括:

5.根据权利要求4所述的半导体结构的制备方法,其特征在于,所述预设沉积工艺包括单频高频射频化学气相沉积工艺;及/或

6.根据权利要求4所述的半导体结构的制备方法,其特征在于,所述第二黏附层的厚度范围为200a至300a。

7.根据权利要求4所述的半导体结构的制备方法,其特征在于,所述第一黏附层的材料包括氮化钽;及/或

8.根据权利要求1所述的半导体结构的制备方法,其特征在于,所述于所述应力释放层的表面形成目标金属层,包括:

9.一种半导体结构,其特征在于,包括:

10.根据权利要求9所述的半导体结构,其特征在于,所述第二黏附层以预设沉积速度采用预设沉积工艺形成。

技术总结

本发明涉及一种半导体结构的制备方法及半导体结构。半导体结构的制备方法包括:提供衬底,并于衬底的表面形成钝化层;于钝化层的表面形成第一黏附层;于第一黏附层的表面形成应力释放层,应力释放层的厚度小于第一黏附层的厚度;于应力释放层的表面形成目标金属层;于目标金属层的表面形成第二黏附层。上述半导体结构的制备方法中,应力释放层能够有效降低目标金属层的晶粒大小,以抑制目标金属层向上释放应力的趋势,并且在不影响整体结构厚度的前提下,有效避免鼓泡状缺陷,于目标金属层的表面形成第二黏附层,能够有效提升目标金属层与第二黏附层之间的粘附性,以降低鼓泡状缺陷,从而提升目标金属层的形貌,以提高半导体产品的生产良率。

技术研发人员:王甄,储郁冬,刘聪

受保护的技术使用者:上海积塔半导体有限公司

技术研发日:

技术公布日:2024/10/21

- 还没有人留言评论。精彩留言会获得点赞!