瞬态电压抑制器及其制备方法与流程

本发明属于半导体集成电路制造领域,涉及一种瞬态电压抑制器及其制备方法。

背景技术:

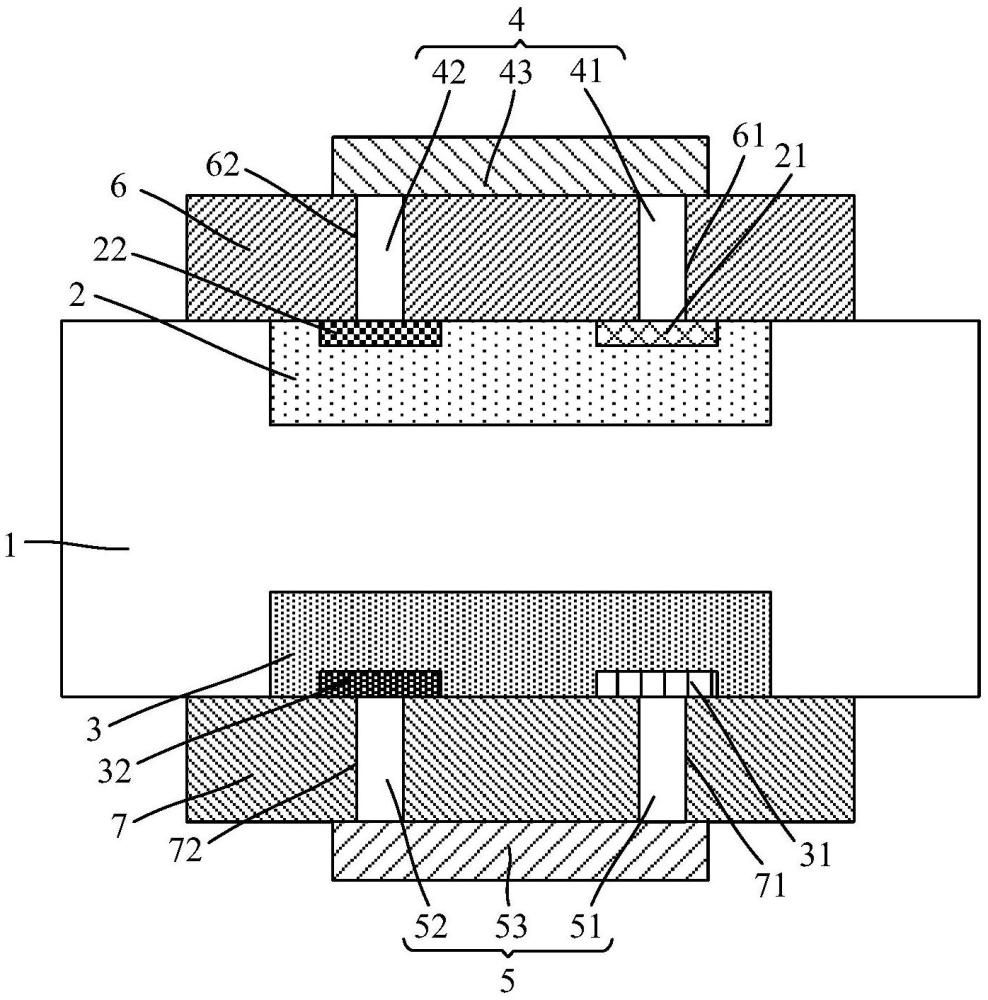

1、瞬态电压抑制器(transient voltage suppressor,tvs)由于独特的电性能(即在受到高能量冲击时,两极之间的高阻抗转变为低阻抗,吸收浪涌功率,使器件的两端电压钳位在一个固定的电压值)而被广泛的应用到器件的保护电路中。如图1所示,为瞬态电压抑制器的剖面结构示意图,包括n型衬底01、沟槽011、氧化硅填充层012、n型阱区02、第一n型掺杂区021、第一p型掺杂区022、p型阱区03、第二n型掺杂区031、第二p型掺杂区032、层间介质层04、第一电极05及第二电极06,其通过沟槽与氧化硅填充层构成的深沟槽隔离结构使横向排列的n型阱区与p型阱区实现电性隔离,增大n型阱区与p型阱区之间的阻值。但是由于其需要制作深沟槽隔离结构,增大了器件的制作难度,且器件的响应速度较慢,导致器件的抗静电及抗浪涌能力较差。

2、因此,急需寻找一种降低器件制作难度同时提升器件抗静电和抗浪涌能力的瞬态电压抑制器。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种瞬态电压抑制器及其制备方法,用于解决现有技术中瞬态电压抑制器的制作难度较大且抗静电和抗浪涌能力较差的问题。

2、为实现上述目的及其他相关目的,本发明提供了一种瞬态电压抑制器,包括以下步骤:

3、第一导电类型衬底;

4、第一导电类型第一阱区,位于所述衬底的上表层;

5、第二导电类型第二阱区,位于所述衬底的下表层且与所述第一阱区间隔预设距离;

6、第一导电类型第一掺杂区,位于所述第一阱区的上表层;

7、第二导电类型第二掺杂区,位于所述第一阱区的上表层且与所述第一掺杂区间隔预设距离;

8、第一导电类型第三掺杂区,位于所述第二阱区的下表层;

9、第二导电类型第四掺杂区,位于所述第二阱区的下表层且与所述第三掺杂区间隔预设距离;

10、第一电极,与所述第一掺杂区及所述第二掺杂区电连接;

11、第二电极,与所述第三掺杂区及所述第四掺杂区电连接。

12、可选地,所述衬底的掺杂浓度小于所述第一阱区的掺杂浓度。

13、可选地,所述第一阱区与所述第二阱区之间的所述衬底中还设有至少一第二导电类型第五掺杂区,所述第五掺杂区与所述第一阱区及所述第二阱区均间隔设置。

14、可选地,所述第二阱区位于所述第一阱区的正下方。

15、可选地,所述第一掺杂区位于所述第三掺杂区的正上方;所述第二掺杂区位于所述第四掺杂区的正上方。

16、可选地,所述衬底的上表面还设有覆盖所述衬底上表面的第一层间介质层,所述第一层间介质层中设有贯穿所述第一层间介质层的第一接触孔及第二接触孔,所述第一接触孔和所述第二接触孔的底面分别显露出所述第一掺杂区及所述第二掺杂区,所述第一电极通过所述第一接触孔和所述第二接触孔分别与所述第一掺杂区及所述第二掺杂区电连接。

17、可选地,所述衬底的下表面还设有覆盖所述衬底下表面的第二层间介质层,所述第二层间介质层中设有贯穿所述第二层间介质层的第三接触孔及第四接触孔,所述第三接触孔和所述第四接触孔的底面分别显露出所述第三掺杂区及所述第四掺杂区,所述第二电极通过所述第三接触孔及所述第四接触孔分别与所述第三掺杂区及所述第四掺杂区电连接。

18、可选地,所述第一电极与所述第一掺杂区及所述第二掺杂区的接触类型为欧姆接触,所述第二电极与所述第三掺杂区及所述第四掺杂区的接触类型为欧姆接触。

19、本发明还提供了一种瞬态电压抑制器的制备方法,包括以下步骤:

20、提供一第一导电类型衬底,并于所述衬底的上表层形成第一导电类型第一阱区;

21、于所述第一阱区的上表层分别形成间隔设置的第一导电类型第一掺杂区及第二导电类型第二掺杂区;

22、形成与所述第一掺杂区及所述第二掺杂区电连接的第一电极;

23、于所述衬底的下表层形成第二导电类型第二阱区,并于所述第二阱区的下表层分别形成间隔设置的第一导电类型第三掺杂区及第二导电类型第四掺杂区;

24、形成与所述第三掺杂区及所述第四掺杂区电连接的第二电极。

25、可选地,形成所述第一电极之后,形成所述第二阱区之前,还包括自所述衬底的下表面对所述衬底进行减薄的步骤。

26、如上所述,本发明的瞬态电压抑制器及其制备方法通过将所述第一阱区设置于所述衬底的上表层,所述第一掺杂区和所述第二掺杂区间隔设置于所述第一阱区的上表层,所述第二阱区设置于所述衬底的下表层,所述第三掺杂区和所述第四掺杂区间隔设置于所述第二阱区的下表层,继而形成纵向器件结构,利用所述第一阱区与所述第二阱区之间的高阻区域实现所述第一阱区与所述第二阱区之间的电性隔离,避免了制作沟槽隔离结构的步骤,降低了器件的制作难度,同时提升了器件与其他器件合封的兼容性,提高了器件的抗静电及抗浪涌能力,具有高度产业利用价值。

技术特征:

1.一种瞬态电压抑制器,其特征在于,包括:

2.根据权利要求1所述的瞬态电压抑制器,其特征在于:所述衬底的掺杂浓度小于所述第一阱区的掺杂浓度。

3.根据权利要求1所述的瞬态电压抑制器,其特征在于:所述第一阱区与所述第二阱区之间的所述衬底中还设有至少一第二导电类型第五掺杂区,所述第五掺杂区与所述第一阱区及所述第二阱区均间隔设置。

4.根据权利要求1所述的瞬态电压抑制器,其特征在于:所述第二阱区位于所述第一阱区的正下方。

5.根据权利要求1所述的瞬态电压抑制器,其特征在于:所述第一掺杂区位于所述第三掺杂区的正上方;所述第二掺杂区位于所述第四掺杂区的正上方。

6.根据权利要求1所述的瞬态电压抑制器,其特征在于:所述衬底的上表面还设有覆盖所述衬底上表面的第一层间介质层,所述第一层间介质层中设有贯穿所述第一层间介质层的第一接触孔及第二接触孔,所述第一接触孔和所述第二接触孔的底面分别显露出所述第一掺杂区及所述第二掺杂区,所述第一电极通过所述第一接触孔和所述第二接触孔分别与所述第一掺杂区及所述第二掺杂区电连接。

7.根据权利要求1所述的瞬态电压抑制器,其特征在于:所述衬底的下表面还设有覆盖所述衬底下表面的第二层间介质层,所述第二层间介质层中设有贯穿所述第二层间介质层的第三接触孔及第四接触孔,所述第三接触孔和所述第四接触孔的底面分别显露出所述第三掺杂区及所述第四掺杂区,所述第二电极通过所述第三接触孔及所述第四接触孔分别与所述第三掺杂区及所述第四掺杂区电连接。

8.根据权利要求1所述的瞬态电压抑制器,其特征在于:所述第一电极与所述第一掺杂区及所述第二掺杂区的接触类型为欧姆接触,所述第二电极与所述第三掺杂区及所述第四掺杂区的接触类型为欧姆接触。

9.一种瞬态电压抑制器的制备方法,其特征在于,包括以下步骤:

10.根据权利要求9所述的瞬态电压抑制器的制备方法,其特征在于:形成所述第一电极之后,形成所述第二阱区之前,还包括自所述衬底的下表面对所述衬底进行减薄的步骤。

技术总结

本发明提供一种瞬态电压抑制器及其制备方法,该瞬态电压抑制器包括衬底、第一和二阱区、第一和二掺杂区、第三和四掺杂区及第一和二电极,其中,第一阱区位于衬底上表层;第二阱区位于衬底下表层且与第一阱区间隔预设距离;第一和二掺杂区间隔设置于第一阱区上表层;第二掺杂区位于第一阱区上表层且与第一掺杂区间隔预设距离;第三掺杂区位于第二阱区下表层;第四掺杂区位于第二阱区下表层且与第三掺杂区间隔预设距离;第一电极与第一和二掺杂区电连接;第二电极与第三和四掺杂区电连接。本发明通过将第一阱区与第二阱区分别设置与衬底的上表层和下表层,形成纵向结构,提升了器件的抗静电及抗浪涌能力,降低了器件的制作难度。

技术研发人员:龚罗炜,姜剑光,刘峰松,祁玉发

受保护的技术使用者:上海积塔半导体有限公司

技术研发日:

技术公布日:2024/11/18

- 还没有人留言评论。精彩留言会获得点赞!