一种半导体结构及其制备方法与流程

本发明涉及半导体领域,特别是涉及一种半导体结构及其制备方法。

背景技术:

1、互补式金属氧化物半导体(complementary metal oxide semiconductor,cmos)具有功耗低、逻辑摆幅大和抗干扰能力强等优点,被广泛应用于计算机、通信和消费电子等众多领域。在cmos中,沟道晶向为<110>时,对控制沟道应力和提高载流子迁移率方面具有显著优势,从而得到越来越多的应用。然而,不同的载流子对拉伸应力和压缩应力的需求不同,因此很难在cmos器件中形成满足空穴压缩应力需求和电子拉伸应力需求的沟道,同时保持较少的缺陷。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种半导体结构及其制备方法,能够在半导体结构上同时构成拉伸应力沟道和压缩应力沟道,且不会对半导体结构产生损伤及应力损失,提高半导体结构的质量。

2、为解决上述技术问题,本发明是通过以下技术方案实现的。

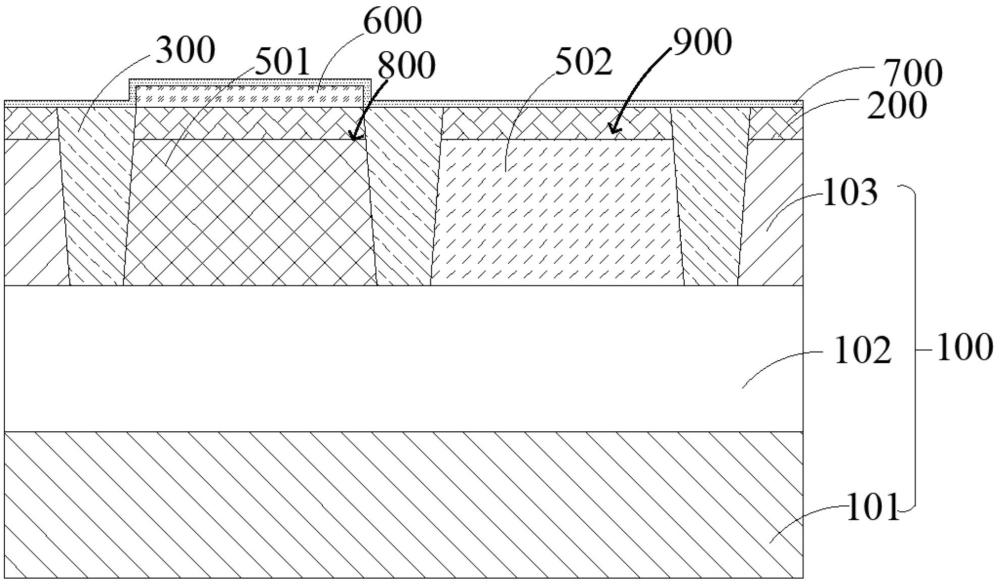

3、本发明提供一种半导体结构,至少包括:

4、衬底,所述衬底内包括间隔设置的第一阱区和第二阱区;

5、第一应力层,设置在所述衬底上;

6、浅沟槽隔离结构,设置在所述第一阱区和所述第二阱区之间,且所述浅沟槽隔离结构由所述第一应力层的表面延伸至所述衬底内;以及

7、第二应力层,设置在所述第一阱区上的所述第一应力层上。

8、在本发明一实施例中,所述第一阱区为p型阱区,所述第二阱区为n型阱区。

9、在本发明一实施例中,所述半导体结构还包括第一应力沟道,所述第一应力沟道至少包括所述第一阱区上的所述第一应力层和所述第二应力层。

10、在本发明一实施例中,所述半导体结构还包括第二应力沟道,所述第二应力沟道至少包括所述第二阱区上的所述第一应力层。

11、在本发明一实施例中,所述第一应力层的材料包括碳化硅,所述第二应力层的材料包括锗化硅。

12、在本发明一实施例中,在所述第二应力层中,由所述第一应力层指向所述第二应力层的方向上,所述第二应力层中的锗含量由0%递增至预设值。

13、在本发明一实施例中,所述预设值为5%-60%。

14、在本发明一实施例中,所述第一应力层的厚度大于所述第二应力层的厚度。

15、在本发明一实施例中,所述第一应力层的厚度为5nm-100nm。

16、本发明还提出一种半导体结构的制备方法,至少包括以下步骤:

17、提供一衬底,在所述衬底内形成间隔设置的第一阱区和第二阱区;

18、在所述衬底上形成第一应力层;

19、在所述第一阱区和所述第二阱区之间设置浅沟槽隔离结构,且所述浅沟槽隔离结构由所述第一应力层的表面延伸至所述衬底内;以及

20、在所述第一阱区上的所述第一应力层上形成第二应力层。

21、综上所述,本发明提供了一种半导体结构及其制备方法,无需额外的刻蚀步骤,能够在半导体结构上同时形成拉伸应力沟道和压缩应力沟道,有效提高空穴和电子载流子的迁移率,提高半导体结构的整体性能。此外,第二应力层采用渐变式锗浓度,能够有效减轻第一应力层和第二层应力层界面缺陷的问题。本发明提供的半导体结构及其制备方法,具有工艺流程简洁便捷的优点,能够减少半导体结构的制备周期和制备成本,且不会对半导体结构产生损伤及应力损失,能够提高半导体结构的质量。

22、当然,实施本发明的任一方式并不一定需要同时达到以上所述的所有优点。

技术特征:

1.一种半导体结构,其特征在于,至少包括:

2.根据权利要求1所述的半导体结构,其特征在于,所述第一阱区为p型阱区,第二阱区为n型阱区。

3.根据权利要求1所述的半导体结构,其特征在于,所述半导体结构还包括第一应力沟道,所述第一应力沟道至少包括所述第一阱区上的所述第一应力层和所述第二应力层。

4.根据权利要求1所述的半导体结构,其特征在于,所述半导体结构还包括第二应力沟道,所述第二应力沟道至少包括所述第二阱区上的所述第一应力层。

5.根据权利要求1所述的半导体结构,其特征在于,所述第一应力层的材料包括碳化硅,所述第二应力层的材料包括锗化硅。

6.根据权利要求5所述的半导体结构,其特征在于,在所述第二应力层中,由所述第一应力层指向所述第二应力层的方向上,所述第二应力层中的锗含量由0%递增至预设值。

7.根据权利要求6所述的半导体结构,其特征在于,所述预设值为5%-60%。

8.根据权利要求1所述的半导体结构,其特征在于,所述第一应力层的厚度大于所述第二应力层的厚度。

9.根据权利要求1所述的半导体结构,其特征在于,所述第一应力层的厚度为5nm-100nm。

10.一种半导体结构的制备方法,其特征在于,至少包括以下步骤:

技术总结

本发明公开了一种半导体结构及其制备方法,属于半导体技术领域。所述半导体结构至少包括:衬底,所述衬底内包括间隔设置的第一阱区和第二阱区;第一应力层,设置在所述衬底上;浅沟槽隔离结构,设置在所述第一阱区和所述第二阱区之间,且所述浅沟槽隔离结构由所述第一应力层的表面延伸至所述衬底内;以及第二应力层,设置在所述第一阱区上的所述第一应力层上。通过本发明提供的半导体结构及其制备方法,能够在半导体结构上同时构成拉伸应力沟道和压缩应力沟道,且不对半导体结构产生损伤及应力损失,提高半导体结构的质量。

技术研发人员:祝强韬,余宗祐,高天,汪涛,孔凡友,张宏光

受保护的技术使用者:杭州积海半导体有限公司

技术研发日:

技术公布日:2024/9/9

- 还没有人留言评论。精彩留言会获得点赞!