一种SGT器件制备方法及SGT器件与流程

本申请涉及半导体制造领域,特别涉及一种sgt器件制备方法及sgt器件。

背景技术:

1、在功率mosfet(metal-oxide-semiconductor field-effect transistor,金属-氧化物半导体场效应晶体管)器件中,由于屏蔽栅沟槽mosfet作为比较先进的功率器件,相较于传统的沟槽mosfet具有更低的导通电阻、更快的开关速度等优点,在很多领域得到了广泛应用。在sgt(shield gate trench,屏蔽栅沟槽) mosfet中,左右结构sgt mosfet由于起工艺简单而得到不少关注。传统的左右结构sgt工艺中由于栅极沟槽是在形成屏蔽栅极之后,回刻屏蔽栅介质层而形成,会使得栅极沟槽底部与屏蔽栅极相临近的底角呈尖角(如图1所示圆圈区域),在形成栅极介质层时,会使得尖角处的栅极介质层的厚度较薄,导致该处位置耐压不足,从而导致栅极漏电。

技术实现思路

1、本申请的目的是提供一种sgt器件制备方法及sgt器件,从而解决传统sgt mosfet制备工艺中由于栅极沟槽底部与屏蔽栅极相临近的底角呈尖角,而导致的栅极漏电问题。

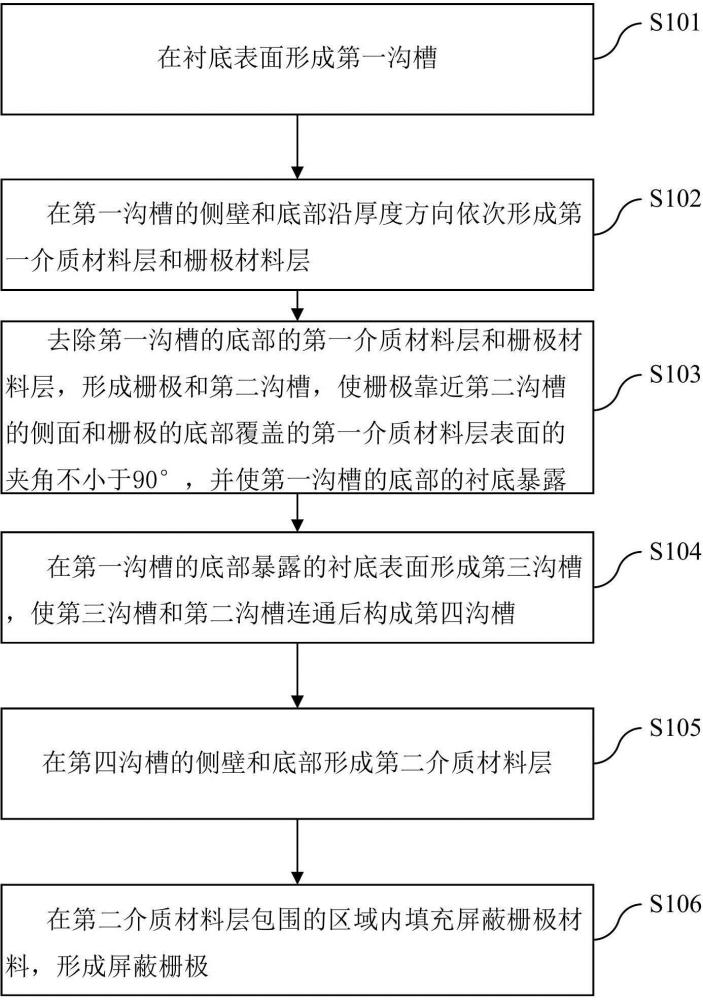

2、为实现上述目的,本申请提供了一种sgt器件制备方法,包括:

3、在衬底表面形成第一沟槽;

4、在所述第一沟槽的侧壁和底部沿厚度方向依次形成第一介质材料层和栅极材料层;

5、去除所述第一沟槽的底部的所述第一介质材料层和所述栅极材料层,形成栅极和第二沟槽,使所述栅极靠近所述第二沟槽的侧面和所述栅极的底部覆盖的所述第一介质材料层表面的夹角不小于90°,并使所述第一沟槽的底部的所述衬底暴露;

6、在所述第一沟槽的底部暴露的所述衬底表面形成第三沟槽,使所述第三沟槽和所述第二沟槽连通后构成第四沟槽;

7、在所述第四沟槽的侧壁和底部形成第二介质材料层;

8、在所述第二介质材料层包围的区域内填充屏蔽栅极材料,形成屏蔽栅极。

9、可选的,所述在所述第一沟槽的侧壁和底部沿厚度方向依次形成第一介质材料层和栅极材料层,包括:

10、通过炉管在所述第一沟槽的侧壁和底部沿厚度方向依次沉积所述第一介质材料层和所述栅极材料层。

11、可选的,所述去除所述第一沟槽的底部的所述第一介质材料层和所述栅极材料层,形成栅极和第二沟槽,使所述栅极靠近所述第二沟槽的侧面和所述栅极的底部覆盖的所述第一介质材料层表面的夹角不小于90°,并使所述第一沟槽的底部的所述衬底暴露,包括:

12、通过干法刻蚀去除所述第一沟槽的底部的所述第一介质材料层和所述栅极材料层,以及沉积在所述衬底表面的所述栅极材料层,形成栅极和第二沟槽,使所述栅极靠近所述第二沟槽的侧面和所述栅极的底部覆盖的所述第一介质材料层表面的夹角不小于90°,并使所述第一沟槽的底部的所述衬底暴露。

13、可选的,所述在所述第一沟槽的底部暴露的所述衬底表面形成第三沟槽,使所述第三沟槽和所述第二沟槽连通后构成第四沟槽,包括:

14、通过干法刻蚀所述第一沟槽的底部暴露的所述衬底,在所述衬底表面形成所述第三沟槽,使所述第三沟槽和所述第二沟槽连通后构成第四沟槽。

15、可选的,所述在所述第四沟槽的侧壁和底部形成第二介质材料层,包括:

16、通过sacvd在所述第四沟槽的侧壁和底部沉积所述第二介质材料层。

17、可选的,所述在衬底表面形成第一沟槽,包括:

18、在所述衬底表面沉积掩膜层;

19、在所述掩膜层表面旋涂光刻胶;

20、通过黄光曝光定义第一沟槽图形;

21、基于所述第一沟槽图形,通过干法刻蚀所述掩膜层和所述衬底,在所述衬底表面形成所述第一沟槽;

22、刻蚀完成后,去除所述光刻胶。

23、可选的,所述在所述衬底表面沉积掩膜层,包括:

24、在所述衬底表面依次沉积第一氧化层、氮化层和第二氧化层。

25、可选的,所述在所述第二介质材料层包围的区域内填充屏蔽栅极材料,形成屏蔽栅极,包括:

26、通过炉管在所述第二介质材料层包围的区域内沉积所述屏蔽栅极材料,以填充整个所述第二介质材料层包围的区域;

27、通过cmp工艺去除沉积在所述衬底表面的所述屏蔽栅极材料,并停止在所述氮化层表面,形成所述屏蔽栅极。

28、可选的,所述在形成有所述第二介质材料层的整个所述第四沟槽内填充屏蔽栅极材料,形成屏蔽栅极后,还包括:

29、去除所述掩膜层;

30、去除所述掩膜层后,通过干法刻蚀回刻所述屏蔽栅极,在所述屏蔽栅极中形成第五沟槽;

31、通过cvd在所述第五沟槽内和所述衬底表面沉积层间介质氧化层;

32、沉积完成后,通过光刻与刻蚀工艺在所述衬底表面形成接触孔。

33、为实现上述目的,本申请还提供了一种sgt器件,包括:衬底;

34、所述衬底表面形成有第一沟槽;所述第一沟槽的侧壁形成有沿厚度方向依次排布的第一介质材料层和栅极;两个所述栅极之间形成有第二沟槽;所述栅极靠近所述第二沟槽的侧面和所述栅极的底部覆盖的所述第一介质材料层表面的夹角不小于90°;

35、所述第一沟槽的底部的所述衬底表面形成有第三沟槽,所述第三沟槽和所述第二沟槽连通构成第四沟槽;

36、所述第四沟槽的侧壁和底部形成有第二介质材料层;所述第二介质材料层包围的区域内填充有屏蔽栅极。

37、显然,本申请提供的一种sgt器件制备方法,先在衬底表面形成第一沟槽,在第一沟槽的侧壁和底部沿厚度方向依次形成第一介质材料层和栅极材料层后,去除第一沟槽的底部的第一介质材料层和栅极材料层,形成栅极和第二沟槽,使栅极靠近第二沟槽的侧面和栅极的底部覆盖的第一介质材料层表面的夹角不小于90°,并使底部的衬底暴露;然后在第一沟槽的底部暴露的衬底表面形成第三沟槽,使第三沟槽和第二沟槽连通后构成第四沟槽,并在第四沟槽的侧壁和底部形成第二介质材料层;最后在第二介质材料层包围的区域内填充屏蔽栅极材料,形成屏蔽栅极。由于是先形成栅极,使栅极靠近屏蔽栅极的侧面和栅极的底部覆盖的介质材料层表面的夹角不小于90°,然后再形成屏蔽栅极,所以栅极底部与屏蔽栅极相临近的底角不会呈尖角,保证了介质层的厚度均匀性,提高了该处位置的耐压,从而降低了栅极漏电。本申请还提供一种sgt器件,具有上述有益效果。

技术特征:

1.一种sgt器件制备方法,其特征在于,包括:

2.根据权利要求1所述的sgt器件制备方法,其特征在于,所述在所述第一沟槽的侧壁和底部沿厚度方向依次形成第一介质材料层和栅极材料层,包括:

3.根据权利要求2所述的sgt器件制备方法,其特征在于,所述去除所述第一沟槽的底部的所述第一介质材料层和所述栅极材料层,形成栅极和第二沟槽,使所述栅极靠近所述第二沟槽的侧面和所述栅极的底部覆盖的所述第一介质材料层表面的夹角不小于90°,并使所述第一沟槽的底部的所述衬底暴露,包括:

4.根据权利要求1所述的sgt器件制备方法,其特征在于,所述在所述第一沟槽的底部暴露的所述衬底表面形成第三沟槽,使所述第三沟槽和所述第二沟槽连通后构成第四沟槽,包括:

5.根据权利要求1所述的sgt器件制备方法,其特征在于,所述在所述第四沟槽的侧壁和底部形成第二介质材料层,包括:

6.根据权利要求1至5任一项所述的sgt器件制备方法,其特征在于,所述在衬底表面形成第一沟槽,包括:

7.根据权利要求6所述的sgt器件制备方法,其特征在于,所述在所述衬底表面沉积掩膜层,包括:

8.根据权利要求7所述的sgt器件制备方法,其特征在于,所述在所述第二介质材料层包围的区域内填充屏蔽栅极材料,形成屏蔽栅极,包括:

9.根据权利要求6所述的sgt器件制备方法,其特征在于,所述在形成有所述第二介质材料层的整个所述第四沟槽内填充屏蔽栅极材料,形成屏蔽栅极后,还包括:

10.一种sgt器件,其特征在于,包括:衬底;

技术总结

本申请公开了一种SGT器件制备方法及SGT器件,属于半导体制造领域,该方法包括:在衬底表面形成第一沟槽;在第一沟槽的侧壁和底部沿厚度方向依次形成第一介质材料层和栅极材料层;去除第一沟槽的底部的第一介质材料层和栅极材料层,形成栅极和第二沟槽,使栅极靠近第二沟槽的侧面和栅极的底部覆盖的第一介质材料层表面的夹角不小于90°,并使第一沟槽的底部的衬底暴露;在第一沟槽的底部暴露的衬底表面形成第三沟槽,使第三沟槽和第二沟槽连通后构成第四沟槽;在第四沟槽的侧壁和底部形成第二介质材料层;在第二介质材料层包围的区域内填充屏蔽栅极材料,形成屏蔽栅极。本申请通过上述方法解决了栅极漏电问题。

技术研发人员:赵君红,陈正嵘

受保护的技术使用者:上海鼎泰匠芯科技有限公司

技术研发日:

技术公布日:2024/11/18

- 还没有人留言评论。精彩留言会获得点赞!