半导体结构及其形成方法与流程

本发明涉及集成电路制造,尤其涉及一种半导体结构及其形成方法。

背景技术:

1、具有电力电子器件的半导体结构正沿着大功率化、高频化、集成化的方向发展。80年代晶闸管的电流容量已达6000安,阻断电压高达6500伏。但这类器件工作频率较低。提高其工作频率,取决于器件关断期间如何加快基区少数载流子(以下简称少子)的复合速度和经门极抽取更多的载流子。降低少子寿命虽能有效地缩短关断电流的过程,却导致器件导通期正向压降的增加。因此必须兼顾转换速度和器件通态功率损耗的要求。为了提高功率器件的工作频率,降低寄生电容是一个有效的手段。但是,当前将对晶体管中栅极与漏极之间寄生电容的方法流程较为复杂,成本较高,而且降低寄生电容的效果不显著。

2、因此,如何在有效降低半导体结构内的寄生电容效应的同时,简化半导体结构的制造工艺,降低半导体结构的制造成本,是当前亟待解决的技术问题。

技术实现思路

1、本发明提供一种半导体结构及其形成方法,用于在有效降低半导体结构内的寄生电容效应的同时,简化半导体结构的制造工艺,降低半导体结构的制造成本。

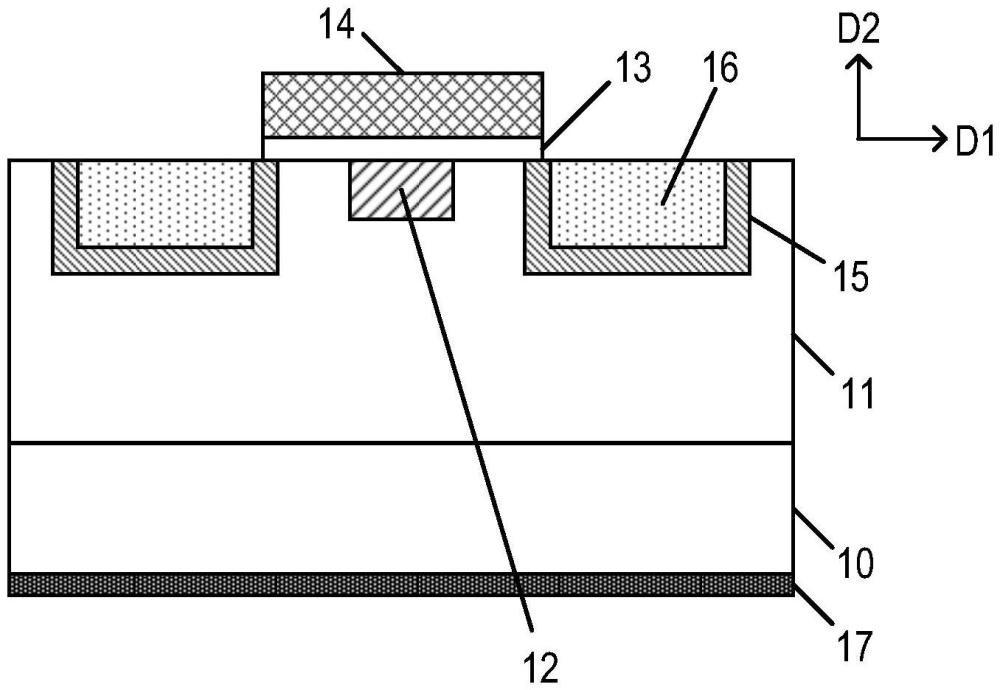

2、根据一些实施例,本发明提供了一种半导体结构,包括:

3、衬底,所述衬底内包括第一掺杂离子,所述衬底包括相对分布的正面和背面;

4、外延层,位于所述衬底的正面上,所述外延层中包括所述第一掺杂离子;

5、栅极结构,位于所述外延层背离所述衬底的表面上;

6、漏电极,位于所述衬底的背面上;

7、隔离结构,位于所述外延层内,所述隔离结构背离所述衬底的表面与所述外延层背离所述衬底的表面平齐,且所述栅极结构在所述外延层上的正投影覆盖所述隔离结构。

8、在一些实施例中,还包括:

9、阱区,位于所述外延层内,所述阱区中包括第二掺杂离子,所述第二掺杂离子的导电类型与所述第一掺杂离子的导电类型相反,且两个所述阱区沿第一方向分布于所述栅极结构在所述外延层上的正投影的相对两侧,所述第一方向与所述衬底的正面平行;

10、源极区,位于所述阱区内,所述隔离结构与所述阱区之间具有一间隙。

11、在一些实施例中,所述隔离结构沿第二方向的深度小于所述阱区沿所述第二方向的深度,所述第二方向与所述衬底的正面垂直。

12、在一些实施例中,所述隔离结构包括:

13、隔离槽,自所述外延层背离所述衬底的表面向所述衬底的内部延伸;

14、绝缘层,填充满所述隔离槽。

15、在一些实施例中,所述绝缘层的材料为氧化硅、氮化硅中的任意一种或者二者的组合。

16、在一些实施例中,所述隔离结构关于所述栅极结构在所述外延层上的正投影的中心对称分布。

17、在一些实施例中,所述隔离结构的宽度小于所述栅极结构的宽度。

18、在一些实施例中,所述隔离结构的宽度大于20nm,且所述隔离结构的宽度小于所述栅极结构的宽度的2/3。

19、根据另一些实施例,本发明还提供了一种半导体结构的形成方法,包括如下步骤:

20、提供衬底,所述衬底内包括第一掺杂离子,所述衬底包括相对分布的正面和背面;

21、于所述衬底的正面形成外延层,所述外延层中包括所述第一掺杂离子;

22、于所述外延层中形成隔离结构,所述隔离结构背离所述衬底的表面与所述外延层背离所述衬底的表面平齐;

23、于所述外延层背离所述衬底的表面上形成栅极结构,所述栅极结构在所述外延层上的正投影覆盖所述隔离结构;

24、形成覆盖所述衬底的背面的漏电极。

25、在一些实施例中,于所述外延层中形成隔离结构之前,还包括如下步骤:

26、于所述外延层中形成沿第一方向间隔排布的两个阱区以及位于每个所述阱区内的源极区,所述阱区中包括第二掺杂离子,所述第二掺杂离子的导电类型与所述第一掺杂离子的导电类型相反,所述第一方向与所述衬底的正面平行。

27、在一些实施例中,于所述外延层中形成隔离结构的具体步骤包括:

28、刻蚀两个所述阱区之间的所述外延层,形成隔离槽,所述隔离槽与所述阱区之间具有一间隙;

29、形成填充满所述隔离槽的绝缘层,所述隔离槽和所述绝缘层共同作为所述隔离结构。

30、在一些实施例中,所述绝缘层的材料为氧化硅、氮化硅中的任意一种或者二者的组合。

31、在一些实施例中,刻蚀两个所述阱区之间的所述外延层,形成隔离槽的具体步骤包括:

32、于所述外延层上定义栅极区域;

33、采用干法刻蚀工艺刻蚀两个所述阱区之间的所述外延层,形成关于所述栅极区域的中心对称分布的所述隔离槽。

34、在一些实施例中,所述隔离槽的宽度大于20nm,且所述隔离槽的宽度小于所述栅极区域的宽度的2/3。

35、本发明提供的半导体结构及其形成方法,通过在衬底上方的外延层中设置隔离结构,所述隔离结构背离所述衬底的表面与所述外延层背离所述衬底的表面平齐,且位于外延层上方的栅极结构在所述外延层上的正投影覆盖所述隔离结构,从而缩小了所述栅极结构与所述外延层之间的正对面积,减小了半导体结构内栅电极(即栅极导电层)与漏电极之间的寄生电容效应,增大了所述半导体结构的开关比及响应速度。而且,本发明仅需在外延层中设置隔离结构,操作简单,成本较低,有助于提高所述半导体结构的制造效率。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.根据权利要求1所述的半导体结构,其特征在于,还包括:

3.根据权利要求2所述的半导体结构,其特征在于,所述隔离结构沿第二方向的深度小于所述阱区沿所述第二方向的深度,所述第二方向与所述衬底的正面垂直。

4.根据权利要求2所述的半导体结构,其特征在于,所述隔离结构包括:

5.根据权利要求4所述的半导体结构,其特征在于,所述绝缘层的材料为氧化硅、氮化硅中的任意一种或者二者的组合。

6.根据权利要求1所述的半导体结构,其特征在于,所述隔离结构关于所述栅极结构在所述外延层上的正投影的中心对称分布。

7.根据权利要求1所述的半导体结构,其特征在于,所述隔离结构的宽度小于所述栅极结构的宽度。

8.根据权利要求7所述的半导体结构,其特征在于,所述隔离结构的宽度大于20nm,且所述隔离结构的宽度小于所述栅极结构的宽度的2/3。

9.一种半导体结构的形成方法,其特征在于,包括如下步骤:

10.根据权利要求9所述的半导体结构的形成方法,其特征在于,于所述外延层中形成隔离结构之前,还包括如下步骤:

11.根据权利要求9所述的半导体结构的形成方法,其特征在于,于所述外延层中形成隔离结构的具体步骤包括:

12.根据权利要求11所述的半导体结构的形成方法,其特征在于,所述绝缘层的材料为氧化硅、氮化硅中的任意一种或者二者的组合。

13.根据权利要求11所述的半导体结构的形成方法,其特征在于,刻蚀两个所述阱区之间的所述外延层,形成隔离槽的具体步骤包括:

14.根据权利要求13所述的半导体结构的形成方法,其特征在于,所述隔离槽的宽度大于20nm,且所述隔离槽的宽度小于所述栅极区域的宽度的2/3。

技术总结

本发明涉及一种半导体结构及其形成方法。所述半导体结构包括:衬底,所述衬底内包括第一掺杂离子,所述衬底包括相对分布的正面和背面;外延层,位于所述衬底的正面上,所述外延层中包括所述第一掺杂离子;栅极结构,位于所述外延层背离所述衬底的表面上;漏电极,位于所述衬底的背面上;隔离结构,位于所述外延层内,所述隔离结构背离所述衬底的表面与所述外延层背离所述衬底的表面平齐,且所述栅极结构在所述外延层上的正投影覆盖所述隔离结构。本发明减小了半导体结构内栅电极与漏电极之间的寄生电容效应。

技术研发人员:于海龙,董信国,孟昭生,贾超超,赵朵朵,常靖华

受保护的技术使用者:上海积塔半导体有限公司

技术研发日:

技术公布日:2024/12/2

- 还没有人留言评论。精彩留言会获得点赞!