一种单层芯片瓷介电容器及其制备方法和应用与流程

本发明涉及电容器,尤其涉及一种单层芯片瓷介电容器及其制备方法和应用。

背景技术:

1、单层芯片瓷介电容器广泛应用于gan或gaas芯片的外围电路、无线通信、光纤通信等微组装电路中,为半导体集成电路、5g通信、航空航天等领域提供薄膜集成封装产品。为保证器件封装过程中可满足金丝键合、共晶焊等焊接方式,同时需要具有优异的电性能、可靠性等,目前市场上大多单层芯片瓷介电容器的双面电极均采用金(au)电极,正面和背面通常均采用tiw+ni+au膜层结构,且其中au层厚度普遍要求>3μm,材料成本较高。

技术实现思路

1、本发明的目的在于提供一种单层芯片瓷介电容器及其制备方法和应用,本发明中单层芯片瓷介电容器的正面和背面采用不同膜层结构,仅正面设置au层,且其厚度≤2000nm,背面pt层的厚度≤600nm,有效降低了材料成本。

2、为了实现上述发明目的,本发明提供以下技术方案:

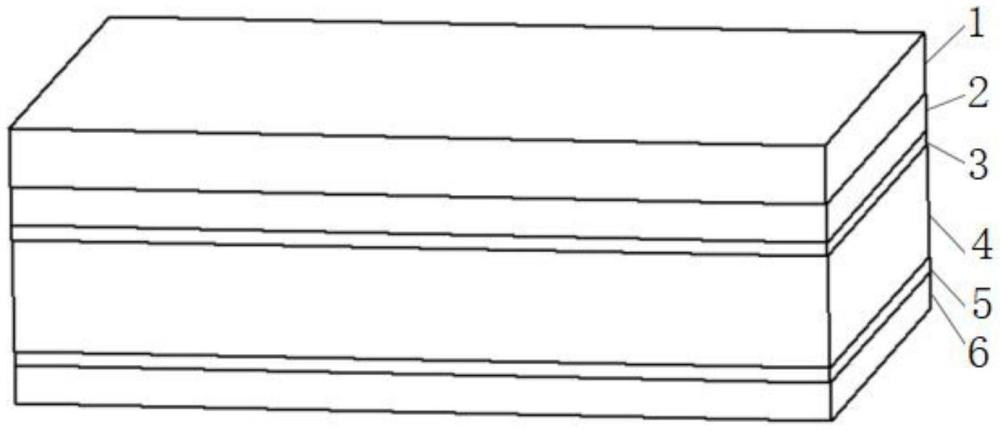

3、本发明提供了一种单层芯片瓷介电容器,包括依次叠层设置的au层、阻挡层、第一tiw层、陶瓷基板、第二tiw层与pt层,所述阻挡层包括niv层,所述au层的厚度≤2000nm,所述pt层的厚度≤600nm。

4、优选地,所述阻挡层还包括与niv层叠层设置的al层或cu层,当所述阻挡层中包括al层或cu层时,所述niv层与au层接触。

5、优选地,所述阻挡层的厚度为500~1500nm;所述al层和cu层的厚度独立为200~600nm。

6、优选地,所述niv层由niv合金形成,所述niv合金中ni的质量分数为90~95%。

7、优选地,所述第一tiw层与第二tiw层由tiw合金形成,形成第一tiw层与第二tiw层的tiw合金中ti的质量分数独立为80~95%。

8、优选地,所述第一tiw层与第二tiw层的厚度独立为50~200nm。

9、优选地,所述au层的厚度为1300~2000nm,所述pt层的厚度为300~600nm。

10、本发明提供了上述技术方案所述单层芯片瓷介电容器的制备方法,包括以下步骤:

11、在陶瓷基板的一表面依次溅射第一tiw层、阻挡层与au层,在所述陶瓷基板的另一表面依次溅射第二tiw层与pt层,得到金属化陶瓷基板;

12、将所述金属化陶瓷基板进行划切处理,得到所述单层芯片瓷介电容器。

13、优选地,所述第一tiw层、阻挡层、au层、第二tiw层与pt层的溅射方式为扫描溅射方式;

14、所述第一tiw层的溅射功率为800~1200w,扫描次数为20~30次;

15、所述au层的溅射功率为300~600w,扫描次数为180~220次;

16、所述第二tiw层的溅射功率为800~1200w,扫描次数为20~30次;

17、所述pt层的溅射功率为600~1000w,扫描次数为80~100次;

18、当所述阻挡层为niv层时,所述阻挡层的溅射功率为800~1200w,扫描次数为45~55次;

19、当所述阻挡层为叠层设置的niv层与al层,或者为叠层设置的niv层与cu层时,所述niv层的溅射功率为800~1200w,扫描次数为25~35次;所述al层的溅射功率为1500~2000w,扫描次数为30~40次;所述cu层的溅射功率为1000~1600w,扫描次数为30~40次。

20、本发明提供了上述技术方案所述单层芯片瓷介电容器或上述技术方案所述制备方法制备得到的单层芯片瓷介电容器在半导体集成电路、5g通信或航空航天领域中的应用。

21、本发明提供了一种单层芯片瓷介电容器,包括依次叠层设置的au层、阻挡层、第一tiw层、陶瓷基板、第二tiw层与pt层,所述阻挡层包括niv层,所述au层的厚度≤2000nm,所述pt层的厚度≤600nm。本发明中单层芯片瓷介电容器的正面和背面采用不同膜层结构,仅正面设置au层,且其厚度≤2000nm,背面pt层的厚度≤600nm,有效降低了材料成本;而且本发明提供的单层芯片瓷介电容器的电性能指标、可焊性、可靠性验证均与传统正反面tiw+ni+au膜层结构产品一致,便于大规模推广使用。

技术特征:

1.一种单层芯片瓷介电容器,其特征在于,包括依次叠层设置的au层、阻挡层、第一tiw层、陶瓷基板、第二tiw层与pt层,所述阻挡层包括niv层,所述au层的厚度≤2000nm,所述pt层的厚度≤600nm。

2.根据权利要求1所述的单层芯片瓷介电容器,其特征在于,所述阻挡层还包括与niv层叠层设置的al层或cu层,当所述阻挡层中包括al层或cu层时,所述niv层与au层接触。

3.根据权利要求2所述的单层芯片瓷介电容器,其特征在于,所述阻挡层的厚度为500~1500nm;所述al层和cu层的厚度独立为200~600nm。

4.根据权利要求1~3任一项所述单层芯片瓷介电容器,其特征在于,所述niv层由niv合金形成,所述niv合金中ni的质量分数为90~95%。

5.根据权利要求1或2所述的单层芯片瓷介电容器,其特征在于,所述第一tiw层与第二tiw层由tiw合金形成,形成第一tiw层与第二tiw层的tiw合金中ti的质量分数独立为80~95%。

6.根据权利要求5所述的单层芯片瓷介电容器,其特征在于,所述第一tiw层与第二tiw层的厚度独立为50~200nm。

7.根据权利要求1、2、3或6所述的单层芯片瓷介电容器,其特征在于,所述au层的厚度为1300~2000nm,所述pt层的厚度为300~600nm。

8.权利要求1~7任一项所述单层芯片瓷介电容器的制备方法,其特征在于,包括以下步骤:

9.根据权利要求8所述的制备方法,其特征在于,所述第一tiw层、阻挡层、au层、第二tiw层与pt层的溅射方式为扫描溅射方式;

10.权利要求1~7任一项所述单层芯片瓷介电容器或权利要求8或9所述制备方法制备得到的单层芯片瓷介电容器在半导体集成电路、5g通信或航空航天领域中的应用。

技术总结

本发明提供了一种单层芯片瓷介电容器及其制备方法和应用,属于电容器技术领域。本发明提供的单层芯片瓷介电容器包括依次叠层设置的Au层、阻挡层、第一TiW层、陶瓷基板、第二TiW层与Pt层,所述阻挡层包括NiV层,所述Au层的厚度≤2000nm,所述Pt层的厚度≤600nm。本发明中单层芯片瓷介电容器的正面和背面采用不同膜层结构,仅正面设置Au层,且其厚度≤2000nm,背面Pt层的厚度≤600nm,有效降低了材料成本;而且本发明提供的单层芯片瓷介电容器的电性能指标、可焊性、可靠性验证均与传统正反面TiW+Ni+Au膜层结构产品一致,便于大规模推广使用。

技术研发人员:王帅,赵伟利,张超越,王新,段成辉

受保护的技术使用者:北京元六鸿远电子科技股份有限公司

技术研发日:

技术公布日:2024/11/7

- 还没有人留言评论。精彩留言会获得点赞!