MOS器件及其制备方法与流程

本申请涉及半导体领域,具体而言,涉及一种mos器件及其制备方法。

背景技术:

1、硅基igbt统治了高压高电流场景,但硅基igbt无法承受高频工况、且功耗较大等,而sic耐高压耐高温的特性,使得其仅用结构更简单的mosfet器件就能覆盖硅基igbt耐压水平,同时规避其高能耗的缺点。碳化硅基mosfet在相同环境下,对比同规格硅基igbt能量损失减少66%,主要来自于开关损耗的大幅减少。在新能源汽车行业,sic可用于驱动和控制电机的逆变器、车载充电器和快速充电桩等。在光伏发电上,目前光伏逆变器龙头企业已采用sic功率器件替代硅器件。

2、沟道迁移率是sic mosfet的重要参数之一,沟道迁移率是指沟道中电子或空穴在电场作用下的迁移速度。在mosfet中,沟道迁移率决定了电流的传输效率和速度。沟道迁移率越高,电子或空穴在沟道中的迁移速度越快,器件的导电性能也越好。

3、sic由于材料本身的影响,另外sic/sio2界面态等因素等大大限制了sic的沟道迁移率,降低了器件的导电性能。

技术实现思路

1、本申请提供一种mos器件及其制备方法,以解决相关技术中mos器件的沟道迁移率低的问题。

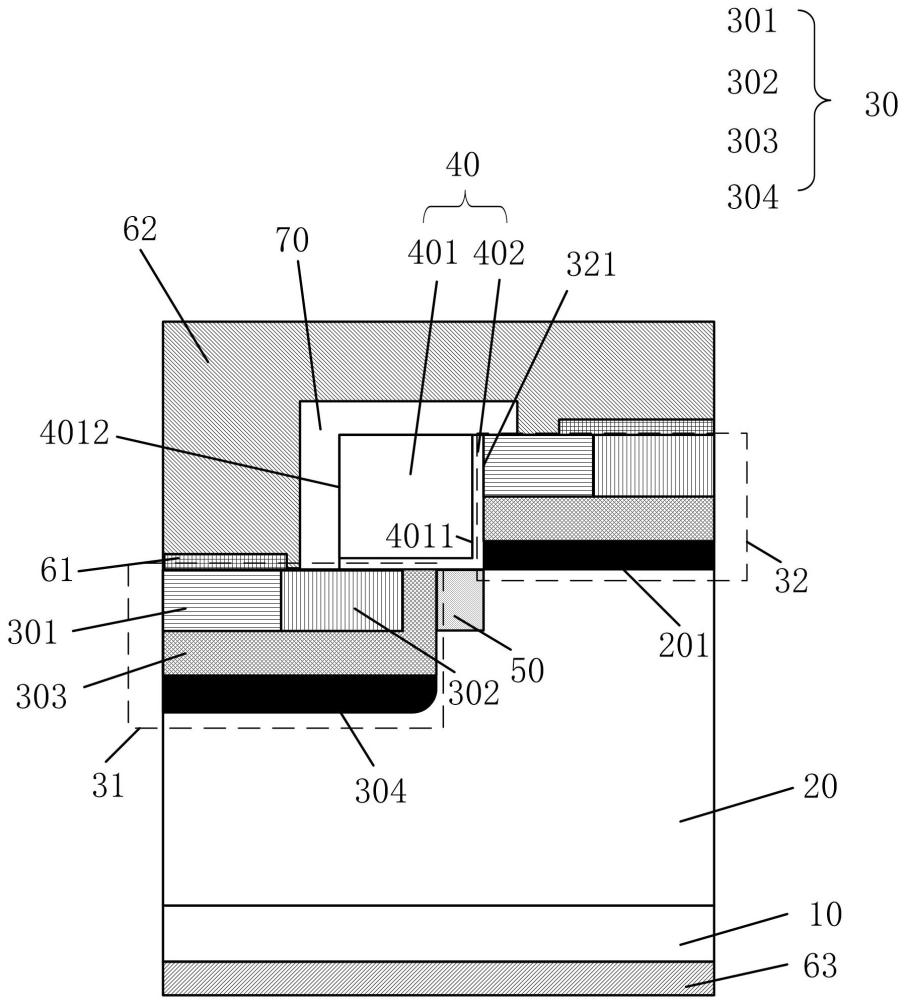

2、根据本申请的一个方面,提供了一种mos器件,包括:衬底以及在所述衬底的一侧具有漂移层,所述漂移层具有背离所述衬底的第一表面,所述mos器件还包括:至少一个源区结构,所述源区结构包括第一重掺杂区、第二重掺杂区和第一体区,所述第一重掺杂区和所述第一体区具有第一掺杂类型,所述第二重掺杂区具有第二掺杂类型,所述第一体区至少位于所述第一重掺杂区和第二重掺杂区靠近所述衬底的一侧,所述第一体区与所述漂移层具有不同的半导体材料;栅极结构,所述栅极结构包括栅极和第一栅介质,所述第一栅介质至少位于所述栅极与所述源区结构之间,其中,所述第一栅介质至少与所述第一体区和所述第二重掺杂区接触。

3、可选地,所述源区结构还包括:第二体区,所述第二体区位于所述第一体区靠近所述衬底一侧且与所述第一体区接触,所述第二体区具有所述第一掺杂类型,且所述第二体区与所述漂移层具有相同的半导体材料。

4、可选地,所述第一体区的材料包括硅材料,所述第二体区的材料包括碳化硅材料。

5、可选地,所述源区结构包括第一源区结构和第二源区结构,所述第一源区结构具有背离所述衬底的第二表面,所述第一源区结构位于所述漂移层中且所述第二表面位于所述第一表面中,所述第二源区结构位于所述漂移层背离所述衬底的一侧,所述第一源区结构与所述第二源区结构不接触;所述栅极结构位于所述漂移层背离所述衬底的一侧,所述栅极结构分别与所述第二源区结构的第一侧面和所述第一源区结构的部分所述第二表面接触,其中,所述第一侧面为所述第二源区结构靠近所述第一源区结构的侧面。

6、可选地,所述的mos器件还包括:电流扩展区,所述电流扩展区位于所述漂移层中且与所述第一源区结构接触,所述电流扩展区背离所述第一源区结构的侧面与所述第一侧面接触,所述电流扩展区具有第二掺杂类型。

7、可选地,所述电流扩展区的掺杂浓度为所述漂移层的掺杂浓度的100倍~1000倍。

8、可选地,mos器件还包括:第一导电层,所述第一导电层位于所述第一重掺杂区和部分所述第二重掺杂区背离衬底的一侧,所述第一导电层与所述源区结构形成欧姆接触。

9、根据本申请的一个方面,提供了一种mos器件的制备方法,用于制备任意一种所述mos器件,所述制备方法包括:提供衬底;在所述衬底上形成漂移层,所述漂移层具有背离所述衬底的第一表面;形成源区结构,所述源区结构包括第一重掺杂区、第二重掺杂区和第一体区,所述第一重掺杂区和所述第一体区具有第一掺杂类型,所述第二重掺杂区具有第二掺杂类型,所述第一体区至少位于所述第一重掺杂区和第二重掺杂区靠近所述衬底的一侧,所述第一体区与所述漂移层具有不同的半导体材料;形成栅极结构,所述栅极结构包括栅极和第一栅介质,所述第一栅介质至少位于所述栅极与所述源区结构之间,其中,所述第一栅介质至少与所述第一体区和所述第二重掺杂区接触。

10、可选地,形成所述源区结构的步骤包括:采用沉积工艺分别在所述漂移层上形成第一材料层;采用离子注入工艺分别在所述第一材料层中进行注入离子,形成所述第一体区;采用离子注入工艺在所述第一体区中分别进行不同掺杂类型的离子注入,形成所述第一重掺杂区和所述第二重掺杂区。

11、可选地,所述制备方法还包括形成第二体区,所述第二体区位于所述第一体区靠近所述衬底一侧且与所述第一体区接触,制备步骤包括:在所述第一材料层中和第二材料层中进行注入离子,所述第一材料层形成所述第一体区,所述第二材料层形成所述第二体区,其中,所述第二材料层为位于所述漂移层中与所述第一材料层接触的部分所述漂移层,所述第一材料层和所述第二材料层在第二方向上进行离子注入的深度的比例为1:2~1:6,所述第二方向垂直于所述第一表面。

12、通过本申请的技术方案,提供一种mos器件,该器件中的第一体区采用与漂移层不同材料,不同的半导体材料与第一栅介质接触后体现不同的载流子迁移率,通过对第一体区设置不同载流子迁移率半导体材料,避免了现有技术中的体区材料与栅氧材料界面态等因素等大大限制了体区的沟道迁移率,提升沟道迁移率以提升电流的传输效率和速度,提升了器件的导电性。

技术特征:

1.一种mos器件,其特征在于,包括:衬底以及在所述衬底的一侧具有漂移层,所述漂移层具有背离所述衬底的第一表面,所述mos器件还包括:

2.根据权利要求1所述的mos器件,其特征在于,所述源区结构还包括:

3.根据权利要求2所述的mos器件,其特征在于,所述第一体区的材料包括硅材料,所述第二体区的材料包括碳化硅材料。

4.根据权利要求1至3中任意一项所述的mos器件,其特征在于,所述源区结构包括第一源区结构和第二源区结构,所述第一源区结构具有背离所述衬底的第二表面,所述第一源区结构位于所述漂移层中且所述第二表面位于所述第一表面中,所述第二源区结构位于所述漂移层背离所述衬底的一侧,所述第一源区结构与所述第二源区结构不接触;

5.根据权利要求4所述的mos器件,其特征在于,还包括:

6.根据权利要求5所述的mos器件,其特征在于,所述电流扩展区的掺杂浓度为所述漂移层的掺杂浓度的100倍~1000倍。

7.根据权利要求1所述的mos器件,其特征在于,还包括:

8.一种mos器件的制备方法,其特征在于,用于制备权利要求1至7中任意一项所述mos器件,所述制备方法包括:

9.根据权利要求8所述的制备方法,其特征在于,形成所述源区结构的步骤包括:

10.根据权利要求9所述的制备方法,其特征在于,还包括形成第二体区,所述第二体区位于所述第一体区靠近所述衬底一侧且与所述第一体区接触,制备步骤包括:

技术总结

本申请公开了一种MOS器件及其制备方法,该MOS器件包括:衬底以及在衬底的一侧具有漂移层,漂移层具有背离衬底的第一表面,MOS器件还包括:至少一个源区结构,源区结构包括第一重掺杂区、第二重掺杂区和第一体区,第一重掺杂区和第一体区具有第一掺杂类型,第二重掺杂区具有第二掺杂类型,第一体区至少位于第一重掺杂区和第二重掺杂区靠近衬底的一侧,第一体区与漂移层具有不同的半导体材料;栅极结构,栅极结构包括栅极和第一栅介质,第一栅介质至少位于栅极与源区结构之间,其中,第一栅介质至少与第一体区和第二重掺杂区接触。以解决相关技术中MOS器件的沟道迁移率低的问题。

技术研发人员:李辉斌,李理,周璇,宋旋坤,陈铭杰

受保护的技术使用者:珠海格力电子元器件有限公司

技术研发日:

技术公布日:2024/12/5

- 还没有人留言评论。精彩留言会获得点赞!