半导体器件及其制备方法与流程

本申请属于功率半导体,尤其涉及一种半导体器件及其制备方法。

背景技术:

1、在功率半导体领域,碳化硅mosfet由于击穿电压高、功率大、导通电阻低及耐高温等众多优势,被广泛应用于高压场景。

2、对于碳化硅mosfet器件来说,容易在过渡区区域出现电场集中,进而导致该区域发生氧化层击穿造成器件失效,对器件的可靠性造成不良影响。

技术实现思路

1、本申请实施例提供一种半导体器件及其制备方法,半导体器件在主结层引入相反导电类型的调节区,调节区能够降低过渡区内栅氧化层部位的电场强度,从而实现半导体器件可靠性的提升。

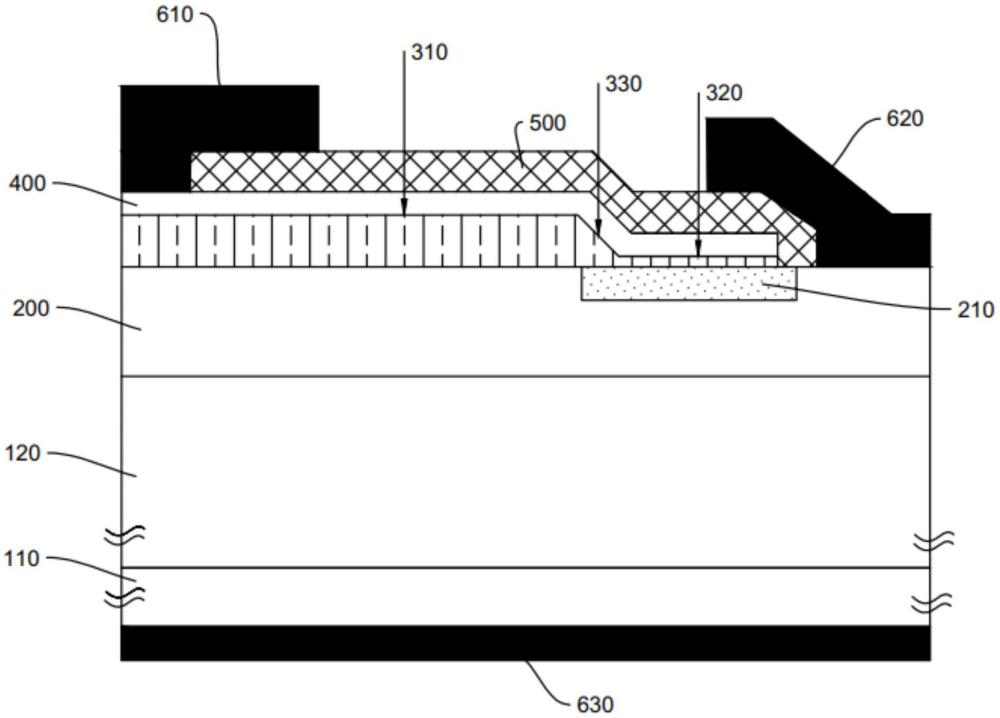

2、第一方面,本申请实施例提供一种半导体器件,包括元胞区、栅总线及过渡区,过渡区位于元胞区与栅总线之间,过渡区包括依次设置的衬底、外延层、主结层、栅氧化层、栅介质层,外延层设置于衬底一侧;主结层设置于外延层背离衬底的一侧,主结层包括调节区,调节区位于主结层背离衬底的一侧,调节区与主结层的导电类型相反;栅氧化层设置于主结层背离衬底的一侧,包括靠近元胞区的第一栅氧结构与靠近栅总线的第二栅氧结构,第一栅氧结构的厚度大于第二栅氧结构的厚度;栅介质层设置于栅氧化层背离衬底的一侧;

3、其中,第二栅氧结构与调节区接触,第二栅氧结构在衬底上的正投影落入调节区在衬底上的正投影范围内。

4、在其中的一些实施例中,栅氧化层还包括第三栅氧结构,第三栅氧结构位于第一栅氧结构与第二栅氧结构之间,沿元胞区向栅总线的方向,第三栅氧结构的厚度逐渐减小。

5、在其中的一些实施例中,第三栅氧结构在衬底上的正投影至少部分地落入调节区在衬底上的正投影范围内。

6、在其中的一些实施例中,调节区的导电离子浓度大于外延层的导电离子浓度。

7、在其中的一些实施例中,过渡区还包括:

8、隔离介质层,位于栅介质层背离衬底的一侧;

9、栅极金属,位于隔离介质层背离衬底的一侧且与栅介质层接触;

10、源极金属,位于隔离介质层背离衬底的一侧且与主结层接触;

11、其中,源极金属与栅极金属通过隔离介质层间隔开来,源极金属与栅介质层沟通过隔离介质层间隔开来。

12、在其中的一些实施例中,沿元胞区向栅总线的方向,源极金属在衬底上的正投影与第一栅氧结构在衬底上的正投影间隔分布。

13、在其中的一些实施例中,源极金属在衬底上的正投影与第二栅氧结构在衬底上的正投影部分重叠。

14、第二方面,本申请实施例提供了一种半导体器件制备方法,制备方法包括:

15、提供衬底,在衬底一侧生长漂移区;

16、对漂移区背离衬底的一侧注入第一导电类型的离子,得到位于漂移区内的外延层及主结层;

17、设置第一掩膜版,对主结层背离衬底的一侧注入第二导电类型的离子,得到调节区;

18、在主结层背离衬底的一侧形成栅氧化层;

19、在栅氧化层背离衬底的一侧形成栅介质层。

20、在其中的一些实施例中,在主结层背离衬底的一侧形成栅氧化层的步骤包括:

21、在主结层背离衬底的一侧淀积厚氧化层,设置第二掩膜版,对厚氧化层刻蚀得到第一栅氧结构;

22、在主结层背离衬底的一侧生长薄氧化层,设置第三掩膜版,对薄氧化层刻蚀得到第二栅氧结构。

23、在其中的一些实施例中,制备方法还包括:

24、在栅介质层背离衬底的一侧淀积隔离介质层,设置第四掩膜版,对隔离介质层刻蚀得到栅极接触孔和源极接触孔;

25、在栅极接触孔内通过金属淀积得到栅极金属,在源极接触孔内通过金属淀积得到源极金属。

26、本申请实施例在半导体器件过渡区的主结层引入导电类型相反的调节区,可以提升调节区上方第二栅氧结构的生长速率,使其在同等时间下生长出更厚的栅氧化层,进而实现器件耐压性能的提升。此外,覆盖第二栅氧结构设置的调节区还能够削弱第二栅氧结构上方的电场强度,降低第二栅氧结构发生击穿导致器件失效的概率,实现器件可靠性的改善。

技术特征:

1.一种半导体器件,其特征在于,包括元胞区、栅总线及过渡区,所述过渡区位于所述元胞区与所述栅总线之间,所述过渡区包括:

2.根据权利要求1所述的半导体器件,其特征在于,所述栅氧化层还包括第三栅氧结构,所述第三栅氧结构位于所述第一栅氧结构与所述第二栅氧结构之间,沿所述元胞区向所述栅总线的方向,所述第三栅氧结构的厚度逐渐减小。

3.根据权利要求2所述的半导体器件,其特征在于,所述第三栅氧结构在所述衬底上的正投影至少部分地落入所述调节区在所述衬底上的正投影范围内。

4.根据权利要求1所述的半导体器件,其特征在于,所述调节区的导电离子浓度大于所述外延层的导电离子浓度。

5.根据权利要求1所述的半导体器件,其特征在于,所述过渡区还包括:

6.根据权利要求5所述的半导体器件,其特征在于,沿所述元胞区向所述栅总线的方向,所述源极金属在所述衬底上的正投影与所述第一栅氧结构在所述衬底上的正投影间隔分布。

7.根据权利要求5所述的半导体器件,其特征在于,所述源极金属在所述衬底上的正投影与所述第二栅氧结构在所述衬底上的正投影部分重叠。

8.一种半导体器件制备方法,其特征在于,制备方法包括:

9.根据权利要求8所述的半导体器件制备方法,其特征在于,所述在主结层背离衬底的一侧形成栅氧化层的步骤包括:

10.根据权利要求8所述的半导体器件制备方法,其特征在于,制备方法还包括:

技术总结

本申请公开了一种半导体器件及其制备方法,半导体器件包括元胞区、栅总线及过渡区,过渡区位于元胞区与栅总线之间,过渡区包括衬底、外延层、主结层、栅氧化层、栅介质层,外延层设置于衬底一侧,主结层设置于外延层背离衬底的一侧,主结层包括调节区,调节区位于主结层背离衬底的一侧,调节区与主结层的导电类型相反;栅氧化层设置于主结层背离衬底的一侧,包括靠近元胞区的第一栅氧结构与靠近栅总线的第二栅氧结构,第一栅氧结构的厚度大于第二栅氧结构的厚度;栅介质层设置于栅氧化层背离衬底的一侧。其中,第二栅氧结构与调节区接触,第二栅氧结构在衬底上的正投影落入调节区在衬底上的正投影范围内。

技术研发人员:李寿全,刘志国,张彦飞,赵哿,温霄霞,刘梦新

受保护的技术使用者:北京中科新微特科技开发股份有限公司

技术研发日:

技术公布日:2025/1/2

- 还没有人留言评论。精彩留言会获得点赞!