Ⅲ-Ⅴ族半导体材料与硅晶圆的晶圆级键合方法及键合结构与流程

本发明属于半导体封装,具体涉及一种ⅲ-ⅴ族半导体材料与硅晶圆的晶圆级键合方法及键合结构。

背景技术:

1、ⅲ-ⅴ族半导体材料通常具有优异的光电特性和高频性能,而硅材料具有良好的集成电路兼容性,因此,两者结合有助于实现高效能的异质集成电路(heterogeneousintegration)。

2、ⅲ-ⅴ族半导体材料晶圆与硅晶圆进行wafer-to-wafer(w2w)的封装方式结合了ⅲ-ⅴ族半导体材料,如砷化镓(gaas)、磷化铟(inp)等,与硅材料的各自优点,可以实现高性能的光电子器件、射频器件或其他异质集成应用。但ⅲ-ⅴ族半导体材料晶圆与硅晶圆的直接键合也存在一定的技术挑战,主要表现为材料不匹配,晶格常数差异较大,应力、位错和晶体缺陷,影响器件性能。同时,两者热膨胀系数的差异,可能导致高温工艺中引发热应力,影响封装的可靠性。

3、目前主流的ⅲ-ⅴ半导体材料器件与硅晶圆的封装方式为chip to chip(芯片对芯片)或者chip to wafer(芯片对晶圆)的方式。将ⅲ-ⅴ族半导体材料晶圆先切割成一个个半导体材料器件芯片-chip,再通过倒装焊的方式,封装在硅晶圆或者硅芯片-chip上。

4、上述的封装方式效率效率低且工艺复杂。

5、公开于该背景技术部分的信息仅仅旨在增加对本发明的总体背景的理解,而不应当被视为承认或以任何形式暗示该信息构成已为本领域一般技术人员所公知的现有技术。

技术实现思路

1、本发明的目的在于提供一种ⅲ-ⅴ族半导体材料与硅晶圆的晶圆级键合方法及键合结构,其能够实现ⅲ-ⅴ族半导体材料与硅晶圆的晶圆级键合,提高封装效率。

2、为了实现上述目的,本发明一具体实施例提供的技术方案如下:

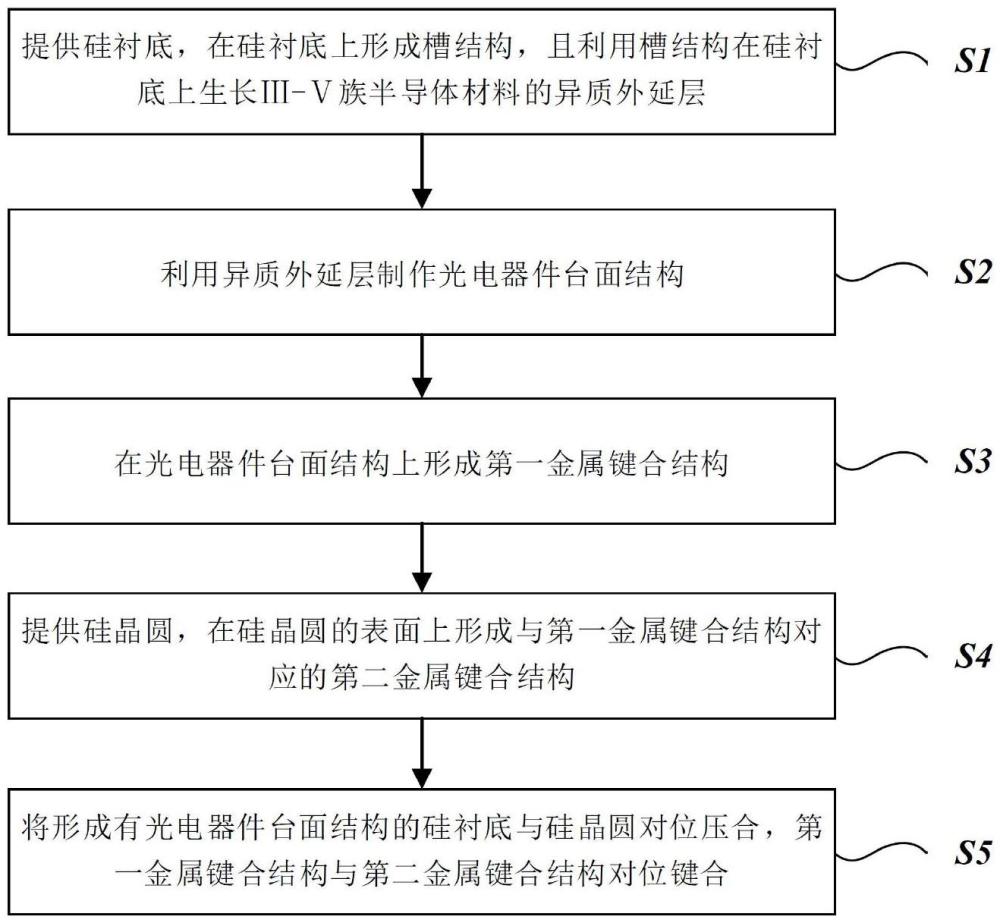

3、一种ⅲ-ⅴ族半导体材料与硅晶圆的晶圆级键合方法,包括:

4、提供硅衬底,在所述硅衬底上形成槽结构,且利用所述槽结构在所述硅衬底上生长ⅲ-ⅴ族半导体材料的异质外延层;

5、利用所述异质外延层制作光电器件台面结构;

6、在所述光电器件台面结构上形成第一金属键合结构;

7、提供硅晶圆,在所述硅晶圆的表面上形成与所述第一金属键合结构对应的第二金属键合结构;

8、将形成有光电器件台面结构的硅衬底与硅晶圆对位压合,所述第一金属键合结构与所述第二金属键合结构对位键合。

9、在本发明的一个或多个实施例中,提供硅衬底,在所述硅衬底上形成槽结构,包括:

10、提供硅衬底,所述硅衬底具有第一表面,所述第一表面为非{111}晶面;

11、在所述硅衬底的第一表面上形成光刻胶层,在所述光刻胶层上形成凹槽,所述凹槽具有至少一所需倾斜角度的斜面;

12、以所述光刻胶层为掩膜层,沿所述凹槽的斜面对所述硅衬底进行倾斜刻蚀,在所述硅衬底上形成具有至少一个{111}晶面的槽结构。

13、在本发明的一个或多个实施例中,所述第一表面为{100}晶面,所述凹槽的斜面相对于所述第一表面的倾斜角度为54.7°;和/或,

14、利用曝光显影技术在所述光刻胶层上形成径向截面为倒梯形的凹槽,所述凹槽的两个侧面相对于所述第一表面的倾斜角度均为54.7°;和/或,

15、采用离子束刻蚀的倾斜刻蚀技术,沿平行于所述凹槽的斜面方向,在所述硅衬底上刻蚀出具有{111}晶面的槽结构,所述槽结构的径向截面为平行四边形,所述槽结构具有相对设置的两个{111}晶面。

16、在本发明的一个或多个实施例中,利用所述槽结构在所述硅衬底上生长ⅲ-ⅴ族半导体材料的异质外延层,包括:

17、在所述硅衬底上沉积氧化层,所述氧化层暴露出所述槽结构的至少一个{111}晶面;

18、在所述槽结构被暴露的{111}晶面上外延生长平坦层,所述平坦层至少覆盖所述槽结构且所述平坦层的顶面与所述硅衬底的第一表面平行;

19、在所述平坦层上外延生长ⅲ-ⅴ族半导体材料的功能层。

20、在本发明的一个或多个实施例中,利用所述异质外延层制作光电器件台面结构,包括:

21、图形化刻蚀所述异质外延层,形成光电器件台面结构。

22、在本发明的一个或多个实施例中,在所述光电器件台面结构上形成第一金属键合结构,包括:

23、在所述异质外延层上形成第一阻挡层,所述第一阻挡层覆盖所述光电器件台面结构;

24、在所述第一阻挡层上形成暴露出所述光电器件台面结构的第一窗口;

25、在所述第一窗口内形成第一金属键合结构。

26、在本发明的一个或多个实施例中,在所述第一窗口内形成第一金属键合结构,包括:

27、在所述第一窗口的内壁上以及所述第一阻挡层表面上形成第一种子层;

28、在所述第一种子层上形成第一金属键合层;

29、对所述第一金属键合层进行减薄抛光处理,形成位于所述第一窗口内的第一金属键合结构,所述第一金属键合结构的表面粗糙度小于1nm。

30、在本发明的一个或多个实施例中,在所述硅晶圆的表面上形成与所述第一金属键合结构对应的第二金属键合结构,包括:

31、在所述硅晶圆的表面上形成第二阻挡层;

32、在所述第二阻挡层上形成与所述第一窗口对应的第二窗口,在所述第二窗口内形成第二金属键合结构。

33、在本发明的一个或多个实施例中,在所述第二窗口内形成第二金属键合结构,包括:

34、在所述第二窗口的内壁上以及所述第二阻挡层表面上形成第二种子层;

35、在所述第二种子层上形成第二金属键合层;

36、对所述第二金属键合层进行减薄抛光处理,形成位于所述第二窗口内的第二金属键合结构,所述第二金属键合结构的表面粗糙度小于1nm。

37、一种ⅲ-ⅴ族半导体材料与硅晶圆的键合结构,采用上述的ⅲ-ⅴ族半导体材料与硅晶圆的晶圆级键合方法键合而成。

38、与现有技术相比,本发明的ⅲ-ⅴ族半导体材料与硅晶圆的晶圆级键合方法及键合结构,通过在图形化的硅衬底上异质外延ⅲ-ⅴ族半导体材料,利用图形化衬底异质外延的优势,实现ⅲ-ⅴ族半导体材料光电器件与硅晶圆的wafer to wafer键合。

39、本发明的ⅲ-ⅴ族半导体材料与硅晶圆的晶圆级键合方法及键合结构,wafer-to-wafer封装技术使得ⅲ-ⅴ族半导体材料与硅材料可以在同一系统中结合,从而优化整体性能,并实现更高的集成度和功能密度。

技术特征:

1.一种ⅲ-ⅴ族半导体材料与硅晶圆的晶圆级键合方法,其特征在于,包括:

2.根据权利要求1所述的ⅲ-ⅴ族半导体材料与硅晶圆的晶圆级键合方法,其特征在于,提供硅衬底,在所述硅衬底上形成槽结构,包括:

3.根据权利要求2所述的ⅲ-ⅴ族半导体材料与硅晶圆的晶圆级键合方法,其特征在于,所述第一表面为{100}晶面,所述凹槽的斜面相对于所述第一表面的倾斜角度为54.7°;和/或,

4.根据权利要求2所述的ⅲ-ⅴ族半导体材料与硅晶圆的晶圆级键合方法,其特征在于,利用所述槽结构在所述硅衬底上生长ⅲ-ⅴ族半导体材料的异质外延层,包括:

5.根据权利要求1所述的ⅲ-ⅴ族半导体材料与硅晶圆的晶圆级键合方法,其特征在于,利用所述异质外延层制作光电器件台面结构,包括:

6.根据权利要求1所述的ⅲ-ⅴ族半导体材料与硅晶圆的晶圆级键合方法,其特征在于,在所述光电器件台面结构上形成第一金属键合结构,包括:

7.根据权利要求6所述的ⅲ-ⅴ族半导体材料与硅晶圆的晶圆级键合方法,其特征在于,在所述第一窗口内形成第一金属键合结构,包括:

8.根据权利要求6所述的ⅲ-ⅴ族半导体材料与硅晶圆的晶圆级键合方法,其特征在于,在所述硅晶圆的表面上形成与所述第一金属键合结构对应的第二金属键合结构,包括:

9.根据权利要求8所述的ⅲ-ⅴ族半导体材料与硅晶圆的晶圆级键合方法,其特征在于,在所述第二窗口内形成第二金属键合结构,包括:

10.一种ⅲ-ⅴ族半导体材料与硅晶圆的键合结构,采用如权利要求1-9任一项所述的ⅲ-ⅴ族半导体材料与硅晶圆的晶圆级键合方法键合而成。

技术总结

本发明公开了一种Ⅲ‑Ⅴ族半导体材料与硅晶圆的晶圆级键合方法及键合结构,晶圆级键合方法包括:提供硅衬底,在硅衬底上形成槽结构,且利用槽结构在硅衬底上生长Ⅲ‑Ⅴ族半导体材料的异质外延层;利用异质外延层制作光电器件台面结构;在光电器件台面结构上形成第一金属键合结构;提供硅晶圆,在硅晶圆的表面上形成与第一金属键合结构对应的第二金属键合结构;将形成有光电器件台面结构的硅衬底与硅晶圆对位压合,第一金属键合结构与第二金属键合结构对位键合。本发明的Ⅲ‑Ⅴ族半导体材料与硅晶圆的晶圆级键合方法及键合结构,其能够实现Ⅲ‑Ⅴ族半导体材料与硅晶圆的晶圆级键合,提高封装效率。

技术研发人员:吴启花

受保护的技术使用者:苏州镓港半导体有限公司

技术研发日:

技术公布日:2025/3/24

- 还没有人留言评论。精彩留言会获得点赞!