一种用于精益化台区管理的断路器跳闸驱动电路的制作方法

1.本发明涉及低压电力台区的技术领域,具体地说是涉及一种用于精益化台区管理的断路器跳闸驱动电路。

背景技术:

2.随着智能电网的建设,低压电力台区的精益化管理成为了一种基本的需求,而其中的断路器,在抗干扰能力方面,也提出了更高的要求。现有的断路器跳闸驱动电路,多为单端驱动,当受到外界干扰时,易造成断路器误跳闸。

技术实现要素:

3.本发明所要解决的技术问题在于针对上述现有技术的不足,提供一种具有采用两个端口来控制断路器跳闸驱动电路,一个端口用于控制跳闸线圈的电源是否接通,另一个端口控制跳闸线圈是否流过电流,从而避免误触发断路器跳闸,提高断路器运行稳定性的用于精益化台区管理的断路器跳闸驱动电路。

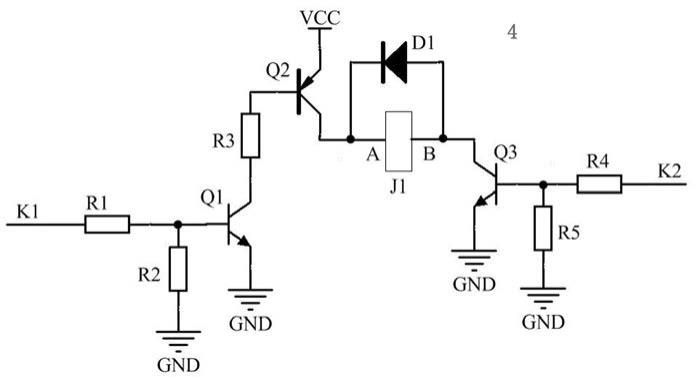

4.为解决上述技术问题,本发明采用的技术方案是:一种用于精益化台区管理的断路器跳闸驱动电路,包括电路,其特征在于:所述的电路两端分别安装有k1和k2,所述的k1和k2为同一个cpu的两个控制端,所述的k1与电阻r1相连,所述的电阻r1的另一端与电阻r2、npn三极管q1的基极相连,所述的电阻r2的另一端接地,所述的三极管q1的发射极接地,三极管q1的集电极与电阻r3相连,所述的电阻r3与pnp三极管q2的基极相连,所述的三极管q2的发射极接到电源的正极vcc,三极管q2的集电极接到二极管d1的负极和断路器跳闸线圈j1的a端,所述的跳闸线圈j1的b端与二极管d1的正极相连,也连接到npn三极管q3的集电极,所述的三极管q3的发射极接地,三极管q3的基极与电阻r4、r5相连,所述的电阻r5的另一端接地,所述的电阻r4的另一端接到cpu的一个控制脚k2上。

5.当k1为低电平时,三极管q1不导通,三极管q2也不导通,断路器跳闸线圈j1的a端无电源,无论k2是高电平还是低电平,断路器跳闸线圈j1两端均无电压,所以断路器不会发生跳闸现象。

6.当k1为高电平时,三极管q1导通,三极管q2也导通,断路器跳闸线圈j1的a端就有电源,此时,k2为低电平时,三极管q3不导通,断路器跳闸线圈j1中无电流流过,所以开关不会跳闸;而当k2为高电平时,三极管q3导通,断路器跳闸线圈j1中有电流流过,开关就能跳闸。

7.可见,只有k1、k2均为高电平时,才能使开关跳闸,而平时,k1、k2均为低电平,偶尔的干扰,使k1或k2其中的一个变为高电平时,也不会发生跳闸现象,提高了断路器运行的抗干扰性能。

8.本发明的有益效果是:这样的一种用于精益化台区管理的断路器跳闸驱动电路具有采用两个端口来控制断路器跳闸驱动电路,一个端口用于控制跳闸线圈的电源是否接通,另一个端口控制跳闸线圈是否流过电流,从而避免误触发断路器跳闸,提高断路器运行

稳定性的优点。

附图说明

9.图1为本发明的电路原理图。

具体实施方式

10.下面结合实施例对本发明作进一步详细说明。

11.如图1所示:一种用于精益化台区管理的断路器跳闸驱动电路,包括电路,其特征在于:所述的电路两端分别安装有k1和k2,所述的k1和k2为同一个cpu的两个控制端,所述的k1与电阻r1相连,所述的电阻r1的另一端与电阻r2、npn三极管q1的基极相连,所述的电阻r2的另一端接地,所述的三极管q1的发射极接地,三极管q1的集电极与电阻r3相连,所述的电阻r3与pnp三极管q2的基极相连,所述的三极管q2的发射极接到电源的正极vcc,三极管q2的集电极接到二极管d1的负极和断路器跳闸线圈j1的a端,所述的跳闸线圈j1的b端与二极管d1的正极相连,也连接到npn三极管q3的集电极,所述的三极管q3的发射极接地,三极管q3的基极与电阻r4、r5相连,所述的电阻r5的另一端接地,所述的电阻r4的另一端接到cpu的一个控制脚k2上。

12.当k1为低电平时,三极管q1不导通,三极管q2也不导通,断路器跳闸线圈j1的a端无电源,无论k2是高电平还是低电平,断路器跳闸线圈j1两端均无电压,所以断路器不会发生跳闸现象。

13.当k1为高电平时,三极管q1导通,三极管q2也导通,断路器跳闸线圈j1的a端就有电源,此时,k2为低电平时,三极管q3不导通,断路器跳闸线圈j1中无电流流过,所以开关不会跳闸;而当k2为高电平时,三极管q3导通,断路器跳闸线圈j1中有电流流过,开关就能跳闸。

14.可见,只有k1、k2均为高电平时,才能使开关跳闸,而平时,k1、k2均为低电平,偶尔的干扰,使k1或k2其中的一个变为高电平时,也不会发生跳闸现象,提高了断路器运行的抗干扰性能。

15.这样的一种用于精益化台区管理的断路器跳闸驱动电路具有采用两个端口来控制断路器跳闸驱动电路,一个端口用于控制跳闸线圈的电源是否接通,另一个端口控制跳闸线圈是否流过电流,从而避免误触发断路器跳闸,提高断路器运行稳定性的优点。

16.以上所述,仅是本发明的较佳实施例,并非对本发明作任何限制。凡是根据发明技术实质对以上实施例所作的任何简单修改、变更以及等效变化,均仍属于本发明技术方案的保护范围内。

技术特征:

1.一种用于精益化台区管理的断路器跳闸驱动电路,包括电路,其特征在于:所述的电路两端分别安装有k1和k2,所述的k1和k2为同一个cpu的两个控制端,所述的k1与电阻r1相连,所述的电阻r1的另一端与电阻r2、npn三极管q1的基极相连,所述的电阻r2的另一端接地,所述的三极管q1的发射极接地,三极管q1的集电极与电阻r3相连,所述的电阻r3与pnp三极管q2的基极相连,所述的三极管q2的发射极接到电源的正极vcc,三极管q2的集电极接到二极管d1的负极和断路器跳闸线圈j1的a端,所述的跳闸线圈j1的b端与二极管d1的正极相连,也连接到npn三极管q3的集电极,所述的三极管q3的发射极接地,三极管q3的基极与电阻r4、r5相连,所述的电阻r5的另一端接地,所述的电阻r4的另一端接到cpu的一个控制脚k2上。2.根据权利要求1所示的一种用于精益化台区管理的断路器跳闸驱动电路,其特征在于:所述的k1为低电平时,三极管q1不导通,三极管q2也不导通,断路器跳闸线圈j1的a端无电源,无论k2是高电平还是低电平,断路器跳闸线圈j1两端均无电压,所以断路器不会发生跳闸现象。3.根据权利要求1所示的一种用于精益化台区管理的断路器跳闸驱动电路,其特征在于:所述的k1为高电平时,三极管q1导通,三极管q2也导通,断路器跳闸线圈j1的a端就有电源,此时,k2为低电平时,三极管q3不导通,断路器跳闸线圈j1中无电流流过,所以开关不会跳闸;而当k2为高电平时,三极管q3导通,断路器跳闸线圈j1中有电流流过,开关就能跳闸。

技术总结

本发明涉及低压电力台区的技术领域,具体地说是涉及一种用于精益化台区管理的断路器跳闸驱动电路,其特征在于:所述的K1、K2均为高电平时,才能使开关跳闸,而平时,K1、K2均为低电平,偶尔的干扰,使K1或K2其中的一个变为高电平时,也不会发生跳闸现象,提高了断路器运行的抗干扰性能,这样的一种用于精益化台区管理的断路器跳闸驱动电路具有采用两个端口来控制断路器跳闸驱动电路,一个端口用于控制跳闸线圈的电源是否接通,另一个端口控制跳闸线圈是否流过电流,从而避免误触发断路器跳闸,提高断路器运行稳定性的优点。提高断路器运行稳定性的优点。提高断路器运行稳定性的优点。

技术研发人员:陈志广 吴卓霖 王振举 徐明明 王佳豪 边红旗 张海峰

受保护的技术使用者:联桥科技有限公司

技术研发日:2021.06.28

技术公布日:2021/11/14

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1