具有稳定放电机制的静电防护电路的制作方法

本发明是关于静电防护技术,尤其是关于一种具有稳定放电机制的静电防护电路。

背景技术:

1、静电放电(electrostatic discharge;esd)会造成电子元件、仪器设备永久性损坏,进而影响积体电路的电路功能,使产品无法正确工作。

2、静电放电的现象可能在晶片制造、封装、测试、存放或搬运的状况下产生。为了再现与预防静电放电,积体电路产品可产品通过静电防护的元件或是电路并搭配测试来增强积体电路对于静电放电的保护能力,进而提升电子产品的良率。

技术实现思路

1、鉴于先前技术的问题,本发明之一目的在于提供一种具有稳定放电机制的静电防护电路,以改善先前技术。

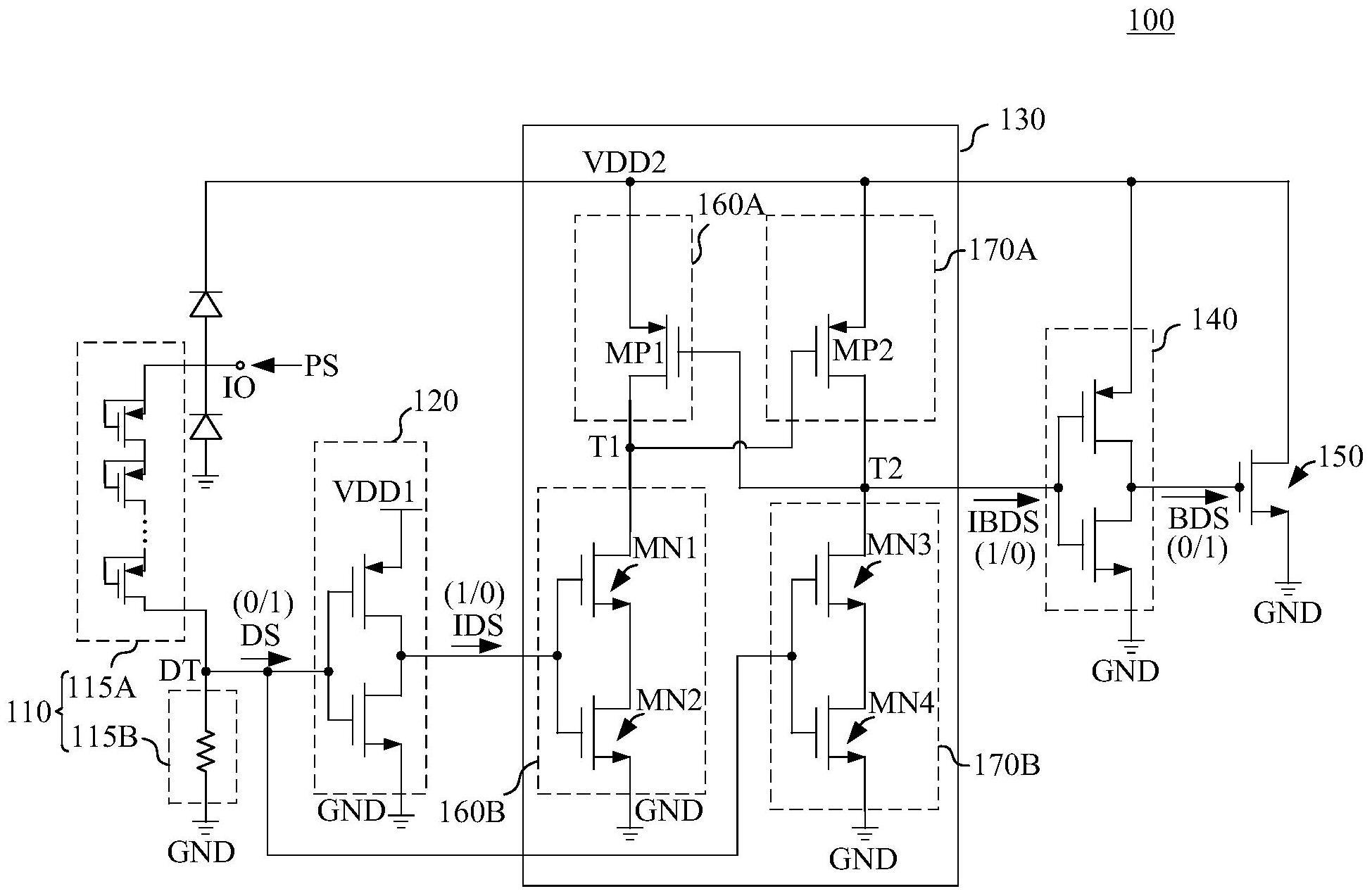

2、本发明包含一种具有稳定放电机制的静电防护电路,包含:分压电路、第一反相器、电压抬升电路、第二反相器以及静电放电晶体管。分压电路电性耦接于配置以接收电源信号的电压输入端,以在分压端产生检测信号。第一反相器配置以接收检测信号反相输出为反相检测信号。电压抬升电路包含:第一p型晶体管电路、第一n型晶体管电路、第二p型晶体管电路以及第二n型晶体管电路。第一p型晶体管电路以及第一n型晶体管电路通过第一端彼此相串联于电压输入端以及接地端间,分别具有电性耦接于第二端的第一p型晶体管控制端以及配置以接收反相检测信号的第一n型晶体管控制端。第二p型晶体管电路以及第二n型晶体管电路,通过第二端彼此串联于电压输入端以及接地端间,分别具有电性耦接于第一端的第二p型晶体管控制端以及配置以接收检测信号的第二n型晶体管控制端。第二反相器电性耦接于电压输入端以及接地端间,配置以自第二端接收反相抬升检测信号反相输出为抬升检测信号。静电放电晶体管电性耦接于电压输入端以及接地端间,配置以受抬升检测信号控制,以在导通时对电压输入端进行放电。

3、有关本案的特征、实践与效果,兹配合图式作较佳实施例详细说明如下。

技术特征:

1.一种具有稳定放电机制的静电防护电路,包含:

2.根据权利要求1所述的静电防护电路,其中该第一反相器根据一第一电压运作,该电压抬升电路、该第二反相器以及该静电放电晶体管根据由该电源信号产生的一第二电压运作,其中该第一电压小于该第二电压,且该第一电压为0.9伏特、1.2伏特或1.8伏特,该第二电压为3.3伏特。

3.根据权利要求1所述的静电防护电路,其中该分压电路包含一第一阻性电路以及一第二阻性电路,通过该分压端串联于该电压输入端以及该接地端间,其中该第一阻性电路以及该第二阻性电路中的每一个包含一电阻、一二极管、一二极管连接式晶体管、或者该电阻、该二极管、该二极管连接式晶体管的组合。

4.根据权利要求1所述的静电防护电路,其中在该电压输入端的电压大小并未超过一预设准位的一正常运作模式下,该检测信号位于一低态准位,该反相检测信号位于一高态准位,该第二p型晶体管电路以及该第一n型晶体管电路导通且该第一p型晶体管电路以及该第二n型晶体管电路关闭,该反相抬升检测信号位于该高态准位,该抬升检测信号位于该低态准位,进而使该静电放电晶体管关闭。

5.根据权利要求1所述的静电防护电路,其中在该电压输入端的电压大小因接收到一静电输入而超过一预设准位的一放电模式下,该检测信号位于一高态准位,该反相检测信号位于一低态准位,该第二p型晶体管电路以及该第一n型晶体管电路关闭且该第一p型晶体管电路以及该第二n型晶体管电路导通,该反相抬升检测信号位于该低态准位,该抬升检测信号位于该高态准位,进而使该静电放电晶体管导通。

6.根据权利要求1所述的静电防护电路,其中该第一n型晶体管电路以及该第二n型晶体管电路中的每一个包含相串联的一第一n型晶体管以及一第二n型晶体管,其中该第一n型晶体管为一输出入装置,该第二n型晶体管为一核心装置。

7.根据权利要求1所述的静电防护电路,其中该第二p型晶体管电路包含相串联的多个p型晶体管。

8.根据权利要求7所述的静电防护电路,其中该电压抬升电路还包含一n型晶体管,电性耦接于该第一端以及该接地端间,且具有电性耦接于该第二端的一第三n型晶体管控制端。

9.根据权利要求1所述的静电防护电路,其中第二电压由该电源信号产生,第一电压由另一独立电压源号产生。

10.根据权利要求1所述的静电防护电路,其中第二电压由该电源信号产生,第一电压由该电源信号分压产生。

技术总结

一种具有稳定放电机制的静电防护电路。分压电路根据电压输入端产生检测信号,第一反相器输出反相检测信号。电压抬升电路的第一P型及N型晶体管电路通过第一端串联于电压输入端及接地端间,第二P型及N型晶体管电路通过第二端串联于电压输入端及接地端间。第一及第二P型晶体管控制端分别电性耦接于第二端及第一端,第一及第二N型晶体管控制端分别接收反相检测信号及检测信号。第二反相器自第二端接收反相抬升检测信号反相输出为抬升检测信号。静电放电晶体管受抬升检测信号控制,以在导通时对电压输入端放电。

技术研发人员:黄崇祐

受保护的技术使用者:瑞昱半导体股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!