本发明涉及boost变换器导通时间测试技术,特别是一种boost变换器最小导通时间测试方法。

背景技术:

1、峰值电流模boost(升压)因其较为简单的环路补偿方式,因此在boost变换器架构中得到很广泛的使用。对于峰值电流模boost,下管开启瞬间由于封装和pcb板寄生电感的影响,导致sw(开关节点)处电压和电流有一定时间的rlc振荡(rlc即电阻电感电容),此振荡可能会使电感电流采样不准而导致pwm(脉宽调制)比较器误触发,因此通常会在pwm比较器中加入blanking电路(即屏蔽电路),在sw振荡期间屏蔽pwm比较器的比较输出信号,直到振荡结束电流采样信号变的平稳之后pwm比较器再进行比较输出。另外,由于pwm比较器和电流采样电路以及驱动电路都有一定的延迟时间,这些延迟时间和pwm比较器blanking时间的存在,都会影响boost变换器的最小导通时间,而最小导通时间决定了boost变换器所能实现的最小占空比,因此客户就尤为关心boost变换器最小导通时间这一参数。

2、对于峰值电流模boost(即电流模升压变换器),为了屏蔽下管(ls或lsd)开启瞬间寄生电感在sw(开关节点)的rlc振荡(rlc即电阻电感电容),而加入的blanking时间(即屏蔽时间),以及环路延迟时间,导致boost的最小导通时间通常难以测量或者测量不准。为了获得boost最小导通时间,一般采用在boost变换器闭环工作情况下,固定输出电压vout,通过逐渐增大输入电压vin,让vin渐次逼近vout,然后测量sw低电平脉宽的方法。这种基于闭环情况来获得boost最小导通时间的测试模式,效率较低,缺少即时性。

技术实现思路

1、本发明针对现有技术中存在的缺陷或不足,提供一种boost变换器最小导通时间测试方法。

2、本发明的技术解决方案如下:

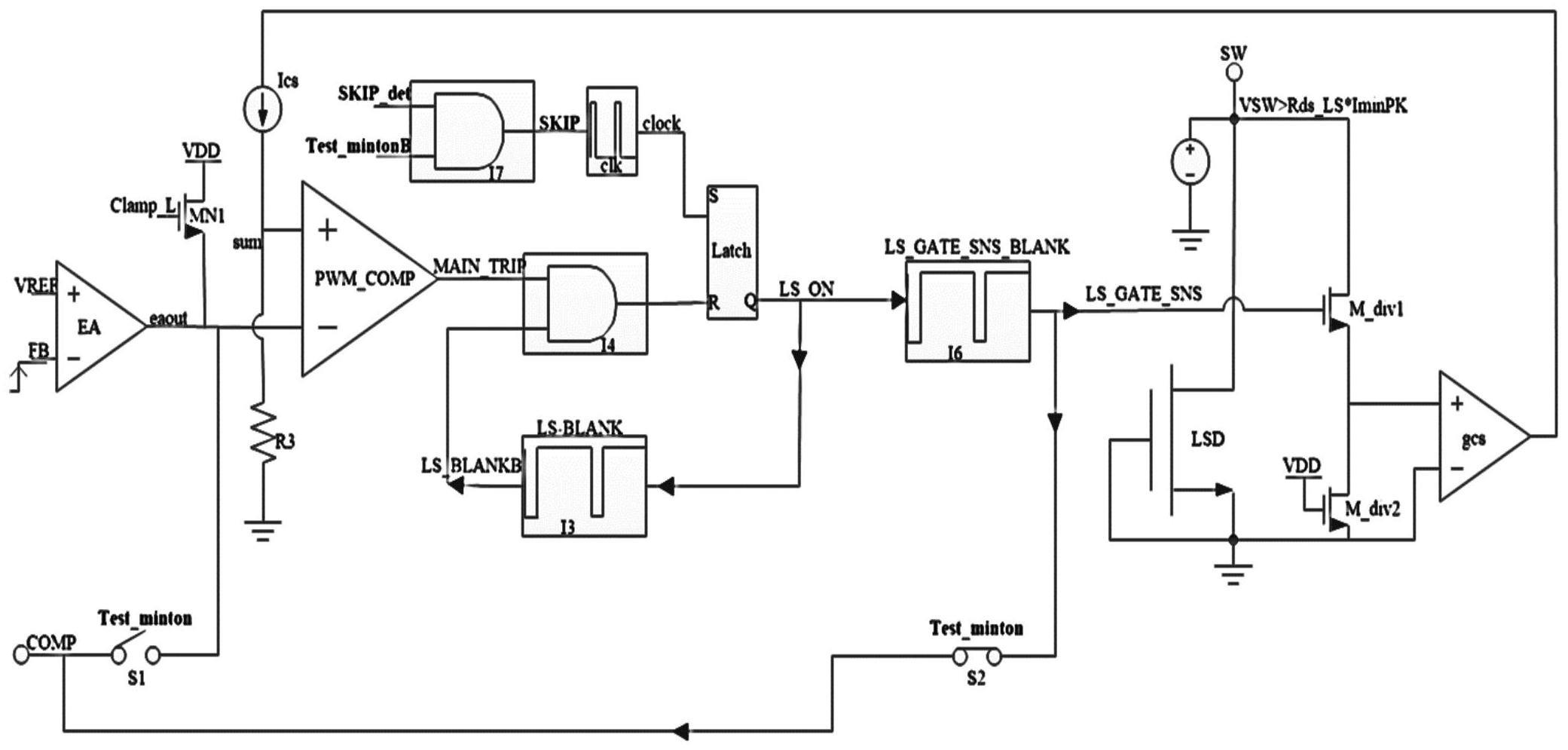

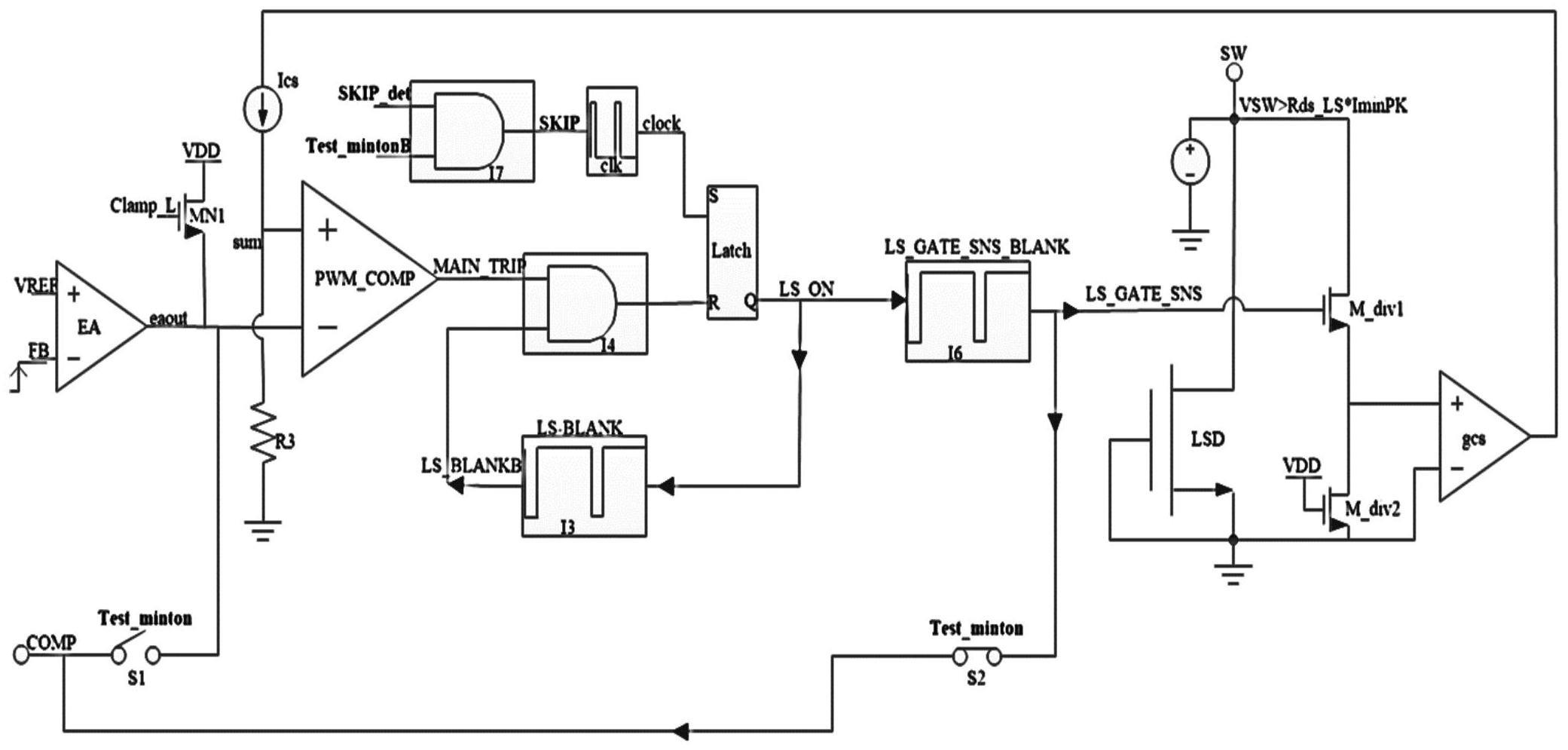

3、一种boost变换器最小导通时间测试方法,其特征在于,包括引入最小导通时间测试模式,所述最小导通时间测试模式通过还原导通时间通路上的延迟时间将下管导通采样控制信号第一个上升沿时刻设为t1,将下管导通采样控制信号第一个下降沿时刻设为t3,将boost变换器的最小导通时间设为minton,则minton=t3-t1,所述下管导通采样控制信号第一个上升沿是下管开启信号经过下管驱动电路中的第六屏蔽电路进行上升沿单边延迟后形成,以匹配下管刚好完全开启,所述下管导通采样控制信号第一个下降沿与所述下管开启信号的第一个下降沿同步,所述下管开启信号的第一个下降沿通过下管电流采样电路被关断而形成。

4、所述下管为nmos管,所述nmos管的栅源互连后接地,所述nmos管的漏极连接开关节点,所述开关节点连接电压源的正极,所述电压源的负极接地,所述开关节点连接所述下管电流采样电路。

5、所述下管电流采样电路包括第一分压采样nmos管,所述第一分压采样nmos管的漏极连接所述开关节点,所述第一分压采样nmos管的栅极连接所述第六屏蔽电路的输出端,所述第一分压采样nmos管的源极与第二分压采样nmos管的漏极互连后连接跨导放大器的正向输入端,所述跨导放大器的负向输入端与所述第二分压采样nmos管的源极均接地,所述第二分压采样nmos管的栅极连接电源电压端,所述跨导放大器的输出端连接采样节点,所述采样节点通过第三电阻接地。

6、所述采样节点连接脉宽调制比较器的正向输入端,所述脉宽调制比较器的负向输入端连接误差放大器的输出端,所述脉宽调制比较器的输出端连接第四与门逻辑电路第一输入端,所述第四与门逻辑电路第二输入端连接第三屏蔽电路的输出端,所述第四与门逻辑电路的输出端连接rs锁存器的第二输入端,所述rs锁存器的第一输入端连接时钟电路的输出端,所述rs锁存器的输出端第一路连接第六屏蔽电路的输入端,第二路连接所述第三屏蔽电路的输入端。

7、所述误差放大器的正向输入端连接参考电压端,负向输入端连接反馈电压端,输出端第一路连接第一nmos管的源极,第二路通过第一传输门开关连接高电平脉宽检测引脚,所述第一nmos管的栅极连接下钳位信号端,所述第一nmos管的漏极连接电源电压端,第六屏蔽电路的输出端通过第二传输门开关连接所述高电平脉宽检测引脚,测量每个内部时钟周期高电平脉宽即得boost变换器的最小导通时间minton。

8、在所述最小导通时间测试模式下,所述第一传输门开关处于关断状态,所述第二传输门开关处于开通状态。

9、所述时钟电路的输入端连接降频屏蔽电路。

10、所述降频屏蔽电路为第七与门逻辑电路,所述第七与门逻辑电路的第一输入端连接降频探测端,第二输入端连接最小导通时间测试信号。

11、本发明的技术效果如下:本发明一种boost变换器最小导通时间测试方法,通过引入最小导通时间测试模式,建立下管电流采样电路,在下管开启信号和下管导通采样控制信号之间设置上升沿单边延迟和下降沿同步的机制,能够有利于在开环情况下还原导通时间通路上的延迟时间,进而与pwm比较器blanking时间比较,二者中时间较长者决定boost的最小导通时间,然后输出到comp引脚,从而在开环情况下快速测试出最小导通时间并输出到芯片外部。

12、本发明能够具有的特点如下:1.在下管采样电路输入端设置强电压源,同时让误差放大器处于下钳位状态,确保下管采样电路只要打开就立马满足关断下管的条件。2.pwm比较器、电流采样电路以及驱动电路的延迟时间都在最小导通时间测试回路中。3.fb置高进行测试,但是内部时钟不会发生降频。

13、本发明与现有技术相比,具有以下优势:电路结构简单,构思巧妙,最小导通时间与实际工作情况基本一致。

技术特征:1.一种boost变换器最小导通时间测试方法,其特征在于,包括引入最小导通时间测试模式,所述最小导通时间测试模式通过还原导通时间通路上的延迟时间将下管导通采样控制信号第一个上升沿时刻设为t1,将下管导通采样控制信号第一个下降沿时刻设为t3,将boost变换器的最小导通时间设为minton,则minton=t3-t1,所述下管导通采样控制信号第一个上升沿是下管开启信号经过下管驱动电路中的第六屏蔽电路进行上升沿单边延迟后形成,以匹配下管刚好完全开启,所述下管导通采样控制信号第一个下降沿与所述下管开启信号的第一个下降沿同步,所述下管开启信号的第一个下降沿通过下管电流采样电路被关断而形成。

2.根据权利要求1所述的boost变换器最小导通时间测试方法,其特征在于,所述下管为nmos管,所述nmos管的栅源互连后接地,所述nmos管的漏极连接开关节点,所述开关节点连接电压源的正极,所述电压源的负极接地,所述开关节点连接所述下管电流采样电路。

3.根据权利要求2所述的boost变换器最小导通时间测试方法,其特征在于,所述下管电流采样电路包括第一分压采样nmos管,所述第一分压采样nmos管的漏极连接所述开关节点,所述第一分压采样nmos管的栅极连接所述第六屏蔽电路的输出端,所述第一分压采样nmos管的源极与第二分压采样nmos管的漏极互连后连接跨导放大器的正向输入端,所述跨导放大器的负向输入端与所述第二分压采样nmos管的源极均接地,所述第二分压采样nmos管的栅极连接电源电压端,所述跨导放大器的输出端连接采样节点,所述采样节点通过第三电阻接地。

4.根据权利要求2所述的boost变换器最小导通时间测试方法,其特征在于,所述采样节点连接脉宽调制比较器的正向输入端,所述脉宽调制比较器的负向输入端连接误差放大器的输出端,所述脉宽调制比较器的输出端连接第四与门逻辑电路第一输入端,所述第四与门逻辑电路第二输入端连接第三屏蔽电路的输出端,所述第四与门逻辑电路的输出端连接rs锁存器的第二输入端,所述rs锁存器的第一输入端连接时钟电路的输出端,所述rs锁存器的输出端第一路连接第六屏蔽电路的输入端,第二路连接所述第三屏蔽电路的输入端。

5.根据权利要求4所述的boost变换器最小导通时间测试方法,其特征在于,所述误差放大器的正向输入端连接参考电压端,负向输入端连接反馈电压端,输出端第一路连接第一nmos管的源极,第二路通过第一传输门开关连接高电平脉宽检测引脚,所述第一nmos管的栅极连接下钳位信号端,所述第一nmos管的漏极连接电源电压端,第六屏蔽电路的输出端通过第二传输门开关连接所述高电平脉宽检测引脚,测量每个内部时钟周期高电平脉宽即得boost变换器的最小导通时间minton。

6.根据权利要求5所述的boost变换器最小导通时间测试方法,其特征在于,在所述最小导通时间测试模式下,所述第一传输门开关处于关断状态,所述第二传输门开关处于开通状态。

7.根据权利要求4所述的boost变换器最小导通时间测试方法,其特征在于,所述时钟电路的输入端连接降频屏蔽电路。

8.根据权利要求7所述的boost变换器最小导通时间测试方法,其特征在于,所述降频屏蔽电路为第七与门逻辑电路,所述第七与门逻辑电路的第一输入端连接降频探测端,第二输入端连接最小导通时间测试信号。

技术总结一种BOOST变换器最小导通时间测试方法,通过引入最小导通时间测试模式,建立下管电流采样电路,在下管开启信号和下管导通采样控制信号之间设置上升沿单边延迟和下降沿同步的机制,能够有利于在开环情况下还原导通时间通路上的延迟时间,进而与PWM比较器blanking时间比较,二者中时间较长者决定BOOST的最小导通时间,然后输出到COMP引脚,从而在开环情况下快速测试出最小导通时间并输出到芯片外部。

技术研发人员:刘阳,于翔

受保护的技术使用者:圣邦微电子(北京)股份有限公司

技术研发日:技术公布日:2024/1/13