电源切换电路及存储器的制作方法

本公开涉及集成电路领域,尤其涉及一种电源切换电路及存储器。

背景技术:

1、在集成电路芯片中,电源切换电路用于根据输入信号的时序来向存储器中的电路提供电源。现有的电源切换电路通常使用独立控制逻辑来控制时钟交叠,或者使用标准非交叠(non-overlap)控制逻辑来控制时钟交叠,但是,该两种方法控制逻辑复杂,可靠性低,且对工艺敏感,无法满足需求。

技术实现思路

1、本公开所要解决的技术问题是,提供一种电源切换电路及存储器。

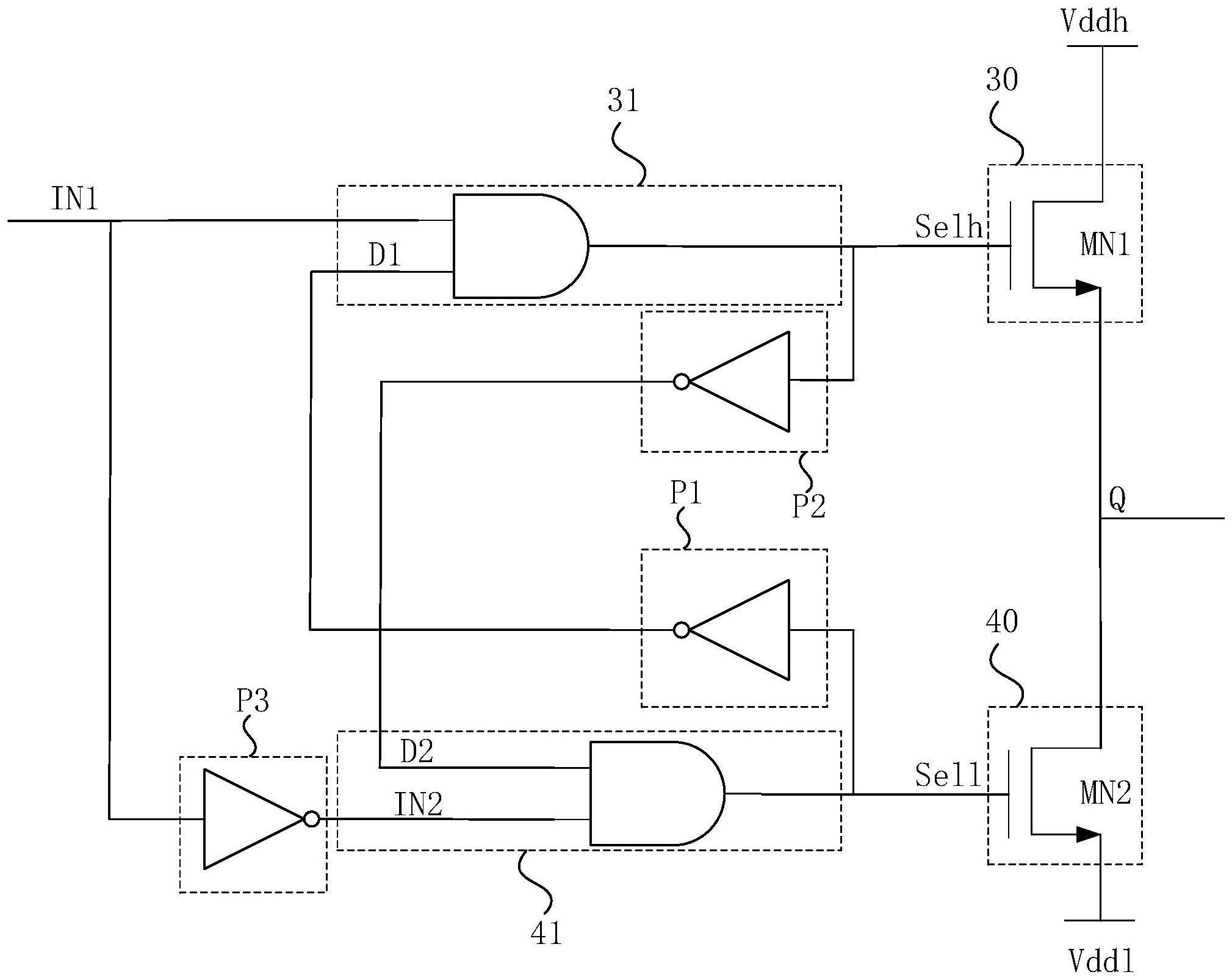

2、为了解决上述问题,本公开实施例提供了一种电源切换电路,其包括:第一输出单元,用于响应第一控制信号向输出节点提供第一电源电压信号;第一控制单元,耦接所述第一输出单元,用于响应第一驱动信号及第一输入信号而产生所述第一控制信号;第二输出单元,用于响应第二控制信号向所述输出节点提供第二电源电压信号;第二控制单元,耦接所述第二输出单元,用于响应第二驱动信号及第二输入信号而产生所述第二控制信号;其中所述第一输入信号与所述第二输入信号相位相反,所述第一驱动信号和所述第二控制信号的相位相反,所述第二驱动信号和所述第一控制信号的相位相反。

3、在本公开一实施例中,还包括:第一反相单元,耦接于所述第二控制单元的输出端和所述第一输出单元的一个输入端之间,用于响应所述第二控制信号而产生所述第一驱动信号;第二反相单元,耦接于所述第一控制单元的输出端和所述第二输出单元的一个输入端之间,用于响应所述第一控制信号而产生所述第二驱动信号。

4、在本公开一实施例中,所述第一反相单元包括奇数个串联的第一反相器。

5、在本公开一实施例中,所述第一反相器包括pmos晶体管与nmos晶体管,其中,至少一个所述第一反相器的所述nmos晶体管的尺寸大于所述pmos晶体管的尺寸。

6、在本公开一实施例中,所述第二反相单元包括奇数个串联的第二反相器。

7、在本公开一实施例中,所述第二反相器包括pmos晶体管与nmos晶体管,其中,至少一个所述第二反相器的所述nmos晶体管的尺寸大于所述pmos晶体管的尺寸。

8、在本公开一实施例中,所述第一反相单元包含的第一反相器的数量与所述第二反相单元包含的第二反相器的数量相同。

9、在本公开一实施例中,所述第一输出单元包括第一nmos晶体管,所述第一nmos晶体管的栅极接收所述第一控制信号,所述第一nmos晶体管的第一极接收所述第一电源电压信号,所述第一nmos晶体管的第二极连接所述输出节点;所述第二输出单元包括第二nmos晶体管,所述第二nmos晶体管的栅极接收所述第二控制信号,所述第二nmos晶体管的第一极接收所述第二电源电压信号,所述第二nmos晶体管的第二极连接所述输出节点。

10、在本公开一实施例中,所述第一控制单元包括第一逻辑门电路,所述第一逻辑门电路用于对所述第一输入信号和所述第一驱动信号进行逻辑与的运算。

11、在本公开一实施例中,所述第一逻辑门电路包括第一与门,所述第一与门的第一输入端接收所述第一输入信号,所述第一与门的第二输入端接收所述第一驱动信号,所述第一与门的输出端输出所述第一控制信号。

12、在本公开一实施例中,还包括第一延迟单元,所述第一延迟单元耦接于所述第一控制单元和所述第一输出单元之间。

13、在本公开一实施例中,所述第一逻辑门电路包括串联连接的第一与非门电路及第一非门电路。

14、在本公开一实施例中,还包括第二延迟单元,所述第二延迟单元耦接于所述第一与非门电路与所述第一非门电路之间。

15、在本公开一实施例中,所述第二控制单元包括第二逻辑门电路,所述第二逻辑门电路用于对所述第二输入信号和所述第二驱动信号进行逻辑与的运算。

16、在本公开一实施例中,所述第二逻辑门电路包括第三反相单元与第二与门,所述第三反相单元的输入端接收所述第一输入信号,所述第三反相单元的输出端输出所述第二输入信号,所述第二与门的第一输入端接收所述第二输入信号,所述第二与门的第二输入端接收所述第二驱动信号,所述第二与门的输出端输出所述第二控制信号。

17、在本公开一实施例中,还包括第三延迟单元,所述第三延迟单元耦接于所述第二控制单元和所述第二输出单元之间。

18、在本公开一实施例中,所述第二逻辑门电路包括串联连接的第二与非门电路及第二非门电路。

19、在本公开一实施例中,还包括第四二延迟单元,所述第四延迟单元耦接于所述第二与非门电路与所述第二非门电路之间。

20、在本公开一实施例中,所述第一电源电压信号为器件工作电压信号,所述第二电源电压信号为接地端电压信号。

21、本公开实施例还提供了一种存储器,其包括如上所述的电源切换电路。

22、本公开实施例提供的电源切换电路利用所述第一输入信号及与所述第二控制信号相位相反的所述第一驱动信号共同产生所述第一控制信号,利用所述第二输入信号及与所述第一控制信号相位相反的所述第二驱动信号共同产生所述第二控制信号,大大减小甚至消除了第一输出单元与第二输出单元同时开启或同时关闭的时间,即重叠(overlap)时间,实现输出节点的有效输出,提高器件的可靠性,并且,采用本公开的电源切换电路实现消除重叠时间相较于使用延迟消除重叠时间而言,控制逻辑简单,可靠,且对工艺不敏感,进一步提高了器件的可靠性。

技术特征:

1.一种电源切换电路,其特征在于,包括:

2.根据权利要求1所述电源切换电路,其特征在于,还包括:

3.根据权利要求2所述电源切换电路,其特征在于,所述第一反相单元包括奇数个串联的第一反相器。

4.根据权利要求3所述电源切换电路,其特征在于,所述第一反相器包括pmos晶体管与nmos晶体管,其中,至少一个所述第一反相器的所述nmos晶体管的尺寸大于所述pmos晶体管的尺寸。

5.根据权利要求2所述电源切换电路,其特征在于,所述第二反相单元包括奇数个串联的第二反相器。

6.根据权利要求5所述电源切换电路,其特征在于,所述第二反相器包括pmos晶体管与nmos晶体管,其中,至少一个所述第二反相器的所述nmos晶体管的尺寸大于所述pmos晶体管的尺寸。

7.根据权利要求2所述电源切换电路,其特征在于,所述第一反相单元包含的第一反相器的数量与所述第二反相单元包含的第二反相器的数量相同。

8.根据权利要求1所述电源切换电路,其特征在于,所述第一输出单元包括第一nmos晶体管,所述第一nmos晶体管的栅极接收所述第一控制信号,所述第一nmos晶体管的第一极接收所述第一电源电压信号,所述第一nmos晶体管的第二极连接所述输出节点;所述第二输出单元包括第二nmos晶体管,所述第二nmos晶体管的栅极接收所述第二控制信号,所述第二nmos晶体管的第一极接收所述第二电源电压信号,所述第二nmos晶体管的第二极连接所述输出节点。

9.根据权利要求1所述电源切换电路,其特征在于,所述第一控制单元包括第一逻辑门电路,所述第一逻辑门电路用于对所述第一输入信号和所述第一驱动信号进行逻辑与的运算。

10.根据权利要求9所述电源切换电路,其特征在于,所述第一逻辑门电路包括第一与门,所述第一与门的第一输入端接收所述第一输入信号,所述第一与门的第二输入端接收所述第一驱动信号,所述第一与门的输出端输出所述第一控制信号。

11.根据权利要求1所述电源切换电路,其特征在于,还包括第一延迟单元,所述第一延迟单元耦接于所述第一控制单元和所述第一输出单元之间。

12.根据权利要求9所述电源切换电路,其特征在于,所述第一逻辑门电路包括串联连接的第一与非门及第一非门,所述第一与非门的第一输入端接收所述第一输入信号,所述第一与非门的第二输入端接收所述第一驱动信号,所述第一非门的输出端输出所述第一控制信号。

13.根据权利要求12所述电源切换电路,其特征在于,还包括第二延迟单元,所述第二延迟单元耦接于所述第一与非门电路与所述第一非门电路之间。

14.根据权利要求1所述电源切换电路,其特征在于,所述第二控制单元包括第二逻辑门电路,所述第二逻辑门电路用于对所述第二输入信号和所述第二驱动信号进行逻辑与的运算。

15.根据权利要求14所述电源切换电路,其特征在于,所述第二逻辑门电路包括第三反相单元与第二与门,所述第三反相单元的输入端接收所述第一输入信号,所述第三反相单元的输出端输出所述第二输入信号,所述第二与门的第一输入端接收所述第二输入信号,所述第二与门的第二输入端接收所述第二驱动信号,所述第二与门的输出端输出所述第二控制信号。

16.根据权利要求1所述电源切换电路,其特征在于,还包括第三延迟单元,所述第三延迟单元耦接于所述第二控制单元和所述第二输出单元之间。

17.根据权利要求14所述电源切换电路,其特征在于,所述第二逻辑门电路包括第四反相单元及串联连接的第二与非门及第二非门,所述第四反相单元的输入端接收所述第一输入信号,所述第四反相单元的输出端输出所述第二输入信号,所述第二与非门的第一输入端接收所述第二输入信号,所述第二与非门的第二输入端接收所述第二驱动信号,所述第二非门的输出端输出所述第二控制信号。

18.根据权利要求17所述电源切换电路,其特征在于,还包括第四延迟单元,所述第四延迟单元耦接于所述第二与非门电路与所述第二非门电路之间。

19.根据权利要求1所述电源切换电路,其特征在于,所述第一电源电压信号为器件工作电压信号,所述第二电源电压信号为接地端电压信号。

20.一种存储器,其特征在于,包括权利要求1~19中任一项所述的电源切换电路。

技术总结

本公开实施例提供一种电源切换电路,其利用所述第一输入信号及与所述第二控制信号相位相反的所述第一驱动信号共同产生所述第一控制信号,利用所述第二输入信号及与所述第一控制信号相位相反的所述第二驱动信号共同产生所述第二控制信号,大大减小甚至消除了第一输出单元与第二输出单元同时开启或同时关闭的时间,即重叠(overlap)时间,实现输出节点的有效输出,提高器件的可靠性,并且,采用本公开的电源切换电路实现消除重叠时间相较于使用延迟消除重叠时间而言,控制逻辑简单,可靠,且对工艺不敏感,进一步提高了器件的可靠性。

技术研发人员:范玉鹏

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!