一种新型POC电路的制作方法

一种新型poc电路

技术领域

1.本实用新型涉及poc电路技术领域,更具体地说,涉及一种新型poc电路。

背景技术:

2.现有的poc电路中,串行解串器的视频和控制信号线d+串联了一个隔直通交的mlcc电容,用于给视频和控制信号d+提供低的阻抗,同时又隔绝直流电源vdd;电源线vdd上串联宽频高阻抗电感,阻碍视频和控制信号d+进入电源以防影响信号完整性,同时也防止电源噪声进入同轴线缆。

3.但是mlcc电容因为寄生电感的原因,高频时阻抗会增大,所以无法在较宽的频率范围内提供很低的阻抗,影响了视频和控制信号的质量。

技术实现要素:

4.本实用新型要解决的技术问题在于,针对现有技术的上述缺陷,提供一种新型poc电路。

5.本实用新型解决其技术问题所采用的技术方案是:

6.构造一种新型poc电路,包括串行解串器,其特征在于,还包括第一bdl滤波器,所述第一bdl滤波器的a极与所述串行解串器的信号线电连接,b极与同轴线缆电连接;所述第一bdl滤波器的b极电连接电源支路。

7.本实用新型所述的新型poc电路,其中,所述电源支路上设置有与所述第一bdl滤波器串联的电感。

8.本实用新型所述的新型poc电路,其中,所述电源支路上设置有抑制电源上emi噪声的π型滤波电路,所述电感的一端与所述第一bdl滤波器电连接,另一端所述π型滤波电路电连接。

9.本实用新型所述的新型poc电路,其中,所述π型滤波电路包括依次分布的第二bdl滤波器、磁珠和第三bdl滤波器;所述磁珠串联设置在所述电源支路上,所述第二bdl滤波器和所述第三bdl滤波器均并联接入所述电源支路。

10.本实用新型所述的新型poc电路,其中,所述第二bdl滤波器以及所述第三bdl滤波器型号均为bdl0805s110v101t。

11.本实用新型所述的新型poc电路,其中,所述第一bdl滤波器型号为bdl0805s110v101t。

12.本实用新型的有益效果在于:应用本申请的新型电路,第一bdl滤波器串联在串行解串器信号线上,因为第一bdl滤波器本身的结构设计,具有极低的esl(寄生电感),其内部有两个平衡电容器,使第一bdl滤波器具有比mlcc电容更宽的频率带和更低的阻抗,减小了dout+上信号的衰减。

附图说明

13.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将结合附图及实施例对本实用新型作进一步说明,下面描述中的附图仅仅是本发明的部分实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他附图:

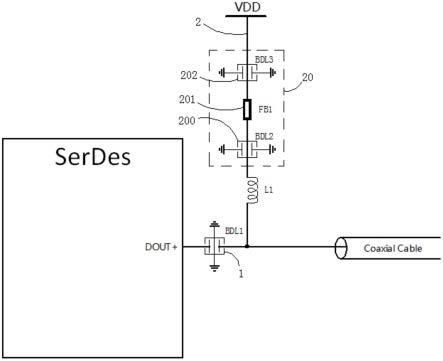

14.图1是本实用新型较佳实施例的新型poc电路电路图;

15.图2是本实用新型较佳实施例的新型poc电路bdl滤波器引脚示意图;

16.图3是本实用新型较佳实施例的新型poc电路bdl滤波器器件使用示意图。

具体实施方式

17.为了使本实用新型实施例的目的、技术方案和优点更加清楚,下面将结合本实用新型实施例中的技术方案进行清楚、完整的描述,显然,所描述的实施例是本实用新型的部分实施例,而不是全部实施例。基于本发明的实施例,本领域普通技术人员在没有付出创造性劳动的前提下所获得的所有其他实施例,都属于本实用新型的保护范围。

18.本实用新型较佳实施例的新型poc电路,如图1所示,包括串行解串器serdes,还包括第一bdl滤波器1,第一bdl滤波器1的a极与串行解串器serdes的信号线dout+电连接,b极与同轴线缆coaxial cable电连接;第一bdl滤波器1的b极电连接电源支路2;

19.应用本申请的新型电路,第一bdl滤波器1串联在串行解串器serdes的信号线dout+上,因为第一bdl滤波器1本身的结构设计,具有极低的esl(寄生电感),其内部有两个平衡电容器,使第一bdl滤波器具有比mlcc电容更宽的频率带和更低的阻抗,减小了dout+上信号的衰减。

20.优选的,电源支路2上设置有与第一bdl滤波器1串联的电感l1;电感l1在dout+信号频率段呈现高阻抗,防止dout+的信号进入电源vdd,减小了dout+上信号的衰减。

21.优选的,电源支路2上设置有抑制电源上emi噪声的π型滤波电路20,电感l1的一端与第一bdl滤波器1电连接,另一端π型滤波电路20电连接。

22.较佳的,π型滤波电路包括依次分布的第二bdl滤波器200、磁珠201和第三bdl滤波器202;磁珠串联设置在电源支路上,第二bdl滤波器和第三bdl滤波器均并联接入电源支路;

23.针对现有的poc电路中电源线上串联的电感无法很好地滤除电源上的emi噪声,会导致电源噪声通过同轴线缆传导和辐射出去的问题,采用由第二bdl滤波器200、磁珠201、第三bdl滤波器202构成的π型滤波电路极大抑制了电源vdd上的emi噪声,防止电源emi噪声从同轴线缆传导和辐射出去;

24.其中,bdl2和bdl3采用并联的接法,让电源vdd的电流以低阻抗通过的同时又具备极佳的滤波效果。

25.优选的,第二bdl滤波器以及第三bdl滤波器型号均为bdl0805s110v101t。

26.优选的,第一bdl滤波器型号为bdl0805s110v101t;

27.bdl滤波器为现有的芯片,大致情况说明如下:

28.电路引脚示意图如图2所示,器件使用示意图如图3所示;

29.引脚介绍:

30.1、器件a、b引脚不导通;

31.2、器件g1、g2引脚之间导通,电阻为0ω;

32.3、器件在电路中使用时,属于并联器件,此时一般都为a、b引脚并在信号两端;

33.4、器件的g1、g2在a、b并联在信号两端时,g1、g2需要接入一个干净的0v的gnd,来配合使用;

34.应当理解的是,对本领域普通技术人员来说,可以根据上述说明加以改进或变换,而所有这些改进和变换都应属于本实用新型所附权利要求的保护范围。

技术特征:

1.一种新型poc电路,包括串行解串器,其特征在于,还包括第一bdl滤波器,所述第一bdl滤波器的a极与所述串行解串器的信号线电连接,b极与同轴线缆电连接;所述第一bdl滤波器的b极电连接电源支路。2.根据权利要求1所述的新型poc电路,其特征在于,所述电源支路上设置有与所述第一bdl滤波器串联的电感。3.根据权利要求2所述的新型poc电路,其特征在于,所述电源支路上设置有抑制电源上emi噪声的π型滤波电路,所述电感的一端与所述第一bdl滤波器电连接,另一端所述π型滤波电路电连接。4.根据权利要求3所述的新型poc电路,其特征在于,所述π型滤波电路包括依次分布的第二bdl滤波器、磁珠和第三bdl滤波器;所述磁珠串联设置在所述电源支路上,所述第二bdl滤波器和所述第三bdl滤波器均并联接入所述电源支路。5.根据权利要求4所述的新型poc电路,其特征在于,所述第二bdl滤波器以及所述第三bdl滤波器型号均为bdl0805s110v101t。6.根据权利要求1或2所述的新型poc电路,其特征在于,所述第一bdl滤波器型号为bdl0805s110v101t。

技术总结

本实用新型涉及新型POC电路,包括串行解串器,还包括第一BDL滤波器,第一BDL滤波器的A极与串行解串器的信号线电连接,B极与同轴线缆电连接;第一BDL滤波器的B极电连接电源支路;应用本申请的新型电路,第一BDL滤波器串联在串行解串器信号线上,因为第一BDL滤波器本身的结构设计,具有极低的ESL(寄生电感),其内部有两个平衡电容器,使第一BDL滤波器具有比MLCC电容更宽的频率带和更低的阻抗,减小了DOUT+上信号的衰减。DOUT+上信号的衰减。DOUT+上信号的衰减。

技术研发人员:凌涛 杨晔龙 卓志达

受保护的技术使用者:深圳市韬略科技有限公司

技术研发日:2022.05.24

技术公布日:2022/9/13

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1