多路BUCK交错并联控制系统的制作方法

本发明涉及测量测试用电子设备,具体涉及一种多路buck交错并联控制系统。

背景技术:

1、在电力电子领域,很多应用场合中都会使用到大电流输出电源,例如电池包测试、燃料电池测试、电动汽车测试、dcdc电源测试、通讯电源测试等。所以大电流输出的测试电源的需求也日益旺盛。而在很多应用场合中,对输入电压纹波以及电压摆率有着非常高的要求,这就对测试电源提出了更高的要求。

2、目前大部分的测试电源最后一级拓扑普遍采用的是buck拓扑,众所周知,电容对改善电压纹波有着非常显著的效果,所以目前很多测试电源都是通过加大输出端的滤波电容的方式,来抑制输出的电压纹波。这种方式的优点很明显,即电路简单、对软件控制算法也没有特殊要求,较易实现,而且由于输出端电容较大,在环路参数的调节上也会变得容易很多。但这种方式的缺点也很明显,首先为了获取较大的容值,往往会采用电解电容,而大电流输出设备的输出端口的温度往往会比较高,这会大大缩短电解电容的使用寿命,也就意味着产品的寿命会大打折扣;其次,由于电容两端的电压不能够突变,所以输出端口的电容越大,电源的输出电压摆率就会越小,也就是说电容会严重限制电源的输出电压摆率,要想提高电源的电压摆率,就必须要想方设法减小输出端电容的容值。

3、当然目前也有很多采用多路buck交错并联的方式,来减小输出电压纹波,随着交错并联的路数增多,输出电压纹波会显著减小。但是随着交错并联路数的增加,buck电感的数量也会相应增多,同时buck电感电流采样支路也会相应增多,这就使得成本和体积增加。

4、在相关技术中,公布号为cn116345848a的专利申请文献中对每路buck进行电流采样,且采用的不是负buck,这就意味着每路的buck电感电流采样需要做隔离采样,电路会更复杂,且成本很高。公布号为cn114900041a的专利申请文献中采用的拓扑是buck-boost,而不是buck,且随着并联数量增加,相应的电感数量以及采用电路数量也会增加,这就导致并联数量是3路,不能更多。

5、因此,目前为了改善输入电压纹波以及电压摆率所采用的方式具有以下不足:

6、(1)通过增大输出端口电容容量的方式严重影响电源的输出电压摆率,同时也会影响电源的使用寿命。

7、(2)通过多路buck交错并联的方式,buck电感数量增加,采样支路也会相应增多,从而导致成本和体积增加。

技术实现思路

1、本发明所要解决的技术问题在于如何以低成本的方案,实现低纹波输出的多路buck交错并联控制。

2、本发明通过以下技术手段解决上述技术问题的:

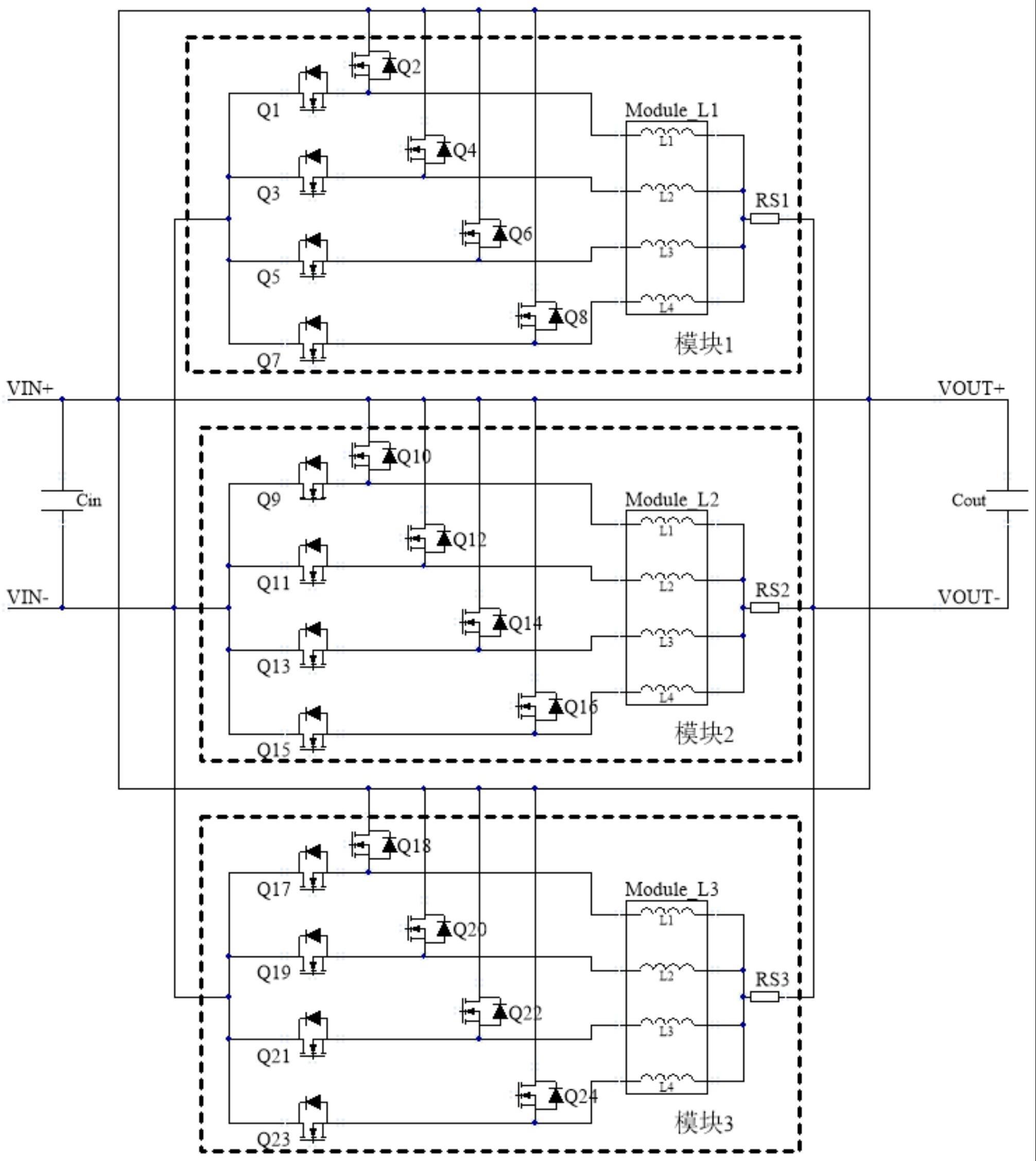

3、本发明提出了一种多路buck交错并联控制系统,所述系统包括交错并联的多个buck模块和均流控制模块,每个所述buck模块包括交错并联的多路buck电路,每路所述buck电路中的晶体管和电感接入负母线,每个所述buck模块中各所述buck电路中的电感分别为绕制于同一磁环上的线圈;每个所述buck模块的输出端分别经对应的采样电阻接入所述均流控制模块。

4、进一步地,每个所述buck模块的输出分别经对应的所述采样电阻连接输出滤波电容,所述采样电阻接入负母线。

5、进一步地,所述采样电阻采用低温漂精密电阻。

6、进一步地,每个所述buck模块的输入均并联母线电容。

7、进一步地,所述磁环采用铁硅材质。

8、进一步地,所述输出滤波电容采用薄膜电容。

9、进一步地,每路所述buck电路包括第一晶体管、第二晶体管和所述电感,所述第一晶体管的漏极接入负母线、源极接入所述第二晶体管的源极,所述第二晶体管的漏极接入正母线,所述第二晶体管的源极接入所述电感。

10、进一步地,所述均流控制模块包括采样调理电路和控制器,各所述采样电阻接入所述采样调理电路,所述采样调理电路的输出连接所述控制器;

11、所述采样调理电路用于采样每个所述采样电阻两端的电压信号,并对电压信号进行滤波处理,得到每个所述buck模块的实时电流值;

12、将各所述buck模块的实时电流值的平均值作为均流环参考值、将每个所述buck模块的实时电流值作为反馈量输入至所述控制器进行pi闭环控制,实现各所述buck模块之间的均流。

13、进一步地,所述均流控制模块包括控制器,所述控制器包括:

14、第一驱动单元,用于对每个所述buck模块中的每路所述buck电路进行交错并联控制,各所述buck电路中的第一晶体管的驱动波形在相位上各相差t/4,t为相位周期;

15、第二驱动单元,用于对每个所述buck模块进行交错并联控制,各所述buck模块中选取一个第一晶体管作为基准晶体管,各基准晶体管的驱动波形在相位上各相差t/3。

16、进一步地,所述控制器还包括:

17、总电流值输出单元,用于根据每个所述buck模块的实时电流值,计算输出总电流值。

18、本发明的优点在于:

19、(1)本发明采用多路buck交错并联的方式,在实现大电流输出的同时,实现超低纹波输出,并且考虑到传统的通过多路buck交错并联的方式会导致buck电感数量,采用将每个buck模块中各buck电路中的电感分别为绕制于同一磁环上的线圈形成的耦合电感形式,有效降低了电感的数量,从而大大降低了成本和体积;并且通过将所有交错并联的buck电路分为若干buck模块,不再对每个电感电流进行采样控制,仅需采样各个buck模块的总电流的方式来实现交错控制,从而进一步降低了电源的硬件成本和体积。此外,由于采用耦合电感的方式,使得模块内部各个硬件参数基本一致,所以每个模块内部4路buck电路可以实现良好均流,不需要额外的均流控制,这样一来也大大简化电路,节约成本,同时也更容易实现更多路的buck并联。

20、(2)晶体管mosfet和电感接入负母线,使得所有buck模块的采样电阻都处于低边,且所有采样电阻均与vout-相连,不需要再进行隔离采样,只需要采用低温漂精密电阻即可实现各个模块的电流采样,能够大大简化电路、节约成本。

21、(3)每个buck模块交错并联使得输出电压纹波会相互抵消,从而实现超低电压纹波输出,所以输出滤波电容不需要采用大容量电容,采用薄膜电容即可,使用寿命较长;且薄膜电容的容值可以取得非常小,从而实现高输出电压摆率。

22、本发明附加的方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本发明的实践了解到。

技术特征:

1.一种多路buck交错并联控制系统,其特征在于,所述系统包括交错并联的多个buck模块和均流控制模块,每个所述buck模块包括交错并联的多路buck电路,每路所述buck电路中的晶体管和电感接入负母线,每个所述buck模块中各所述buck电路中的电感分别为绕制于同一磁环上的线圈;每个所述buck模块的输出端分别经对应的采样电阻接入所述均流控制模块。

2.如权利要求1所述的多路buck交错并联控制系统,其特征在于,每个所述buck模块的输出分别经对应的所述采样电阻连接输出滤波电容,所述采样电阻接入负母线。

3.如权利要求1所述的多路buck交错并联控制系统,其特征在于,所述采样电阻采用低温漂精密电阻。

4.如权利要求1所述的多路buck交错并联控制系统,其特征在于,每个所述buck模块的输入均并联母线电容。

5.如权利要求1所述的多路buck交错并联控制系统,其特征在于,所述磁环采用铁硅材质。

6.如权利要求2所述的多路buck交错并联控制系统,其特征在于,所述输出滤波电容采用薄膜电容。

7.如权利要求1所述的多路buck交错并联控制系统,其特征在于,每路所述buck电路包括第一晶体管、第二晶体管和所述电感,所述第一晶体管的漏极接入负母线、源极接入所述第二晶体管的源极,所述第二晶体管的漏极接入正母线,所述第二晶体管的源极接入所述电感。

8.如权利要求1或7所述的多路buck交错并联控制系统,其特征在于,所述均流控制模块包括采样调理电路和控制器,各所述采样电阻接入所述采样调理电路,所述采样调理电路的输出连接所述控制器;

9.如权利要求7所述的多路buck交错并联控制系统,其特征在于,所述均流控制模块包括控制器,所述控制器包括:

10.如权利要求8所述的多路buck交错并联控制系统,其特征在于,所述控制器还包括:

技术总结

本发明公开一种多路BUCK交错并联控制系统,包括交错并联的多个BUCK模块和均流控制模块,每个所述BUCK模块包括交错并联的多路BUCK电路,每路所述BUCK电路中的晶体管和电感接入负母线,每个所述BUCK模块中各所述BUCK电路中的电感分别为绕制于同一磁环上的线圈;每个所述BUCK模块的输出端分别经对应的采样电阻接入所述均流控制模块;本发明可以低成本的方案,实现超低纹波输出的多路BUCK交错并联控制。

技术研发人员:钟钢炜,姚刘兆,汪坤圆,曹世明,蔡振鸿,唐德平

受保护的技术使用者:科威尔技术股份有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!