抗噪抗干扰的驱动电路的制作方法

本发明属于电子电路设计,尤其涉及抗噪抗干扰的驱动电路。

背景技术:

1、驱动电路位于电源主电路和数字控制核心之间,其本质是将数字控制核心产生的pwm信号进行功率放大,以驱动功率开关器件的开断。隔离型驱动电路是指包含光耦、变压器、电容等具有电气隔离功能器件的驱动电路;变压器驱动电路不仅可以起到驱动作用,还可用于电压隔离和阻抗匹配。

2、如申请号为2020104757177的中国专利申请中公开了一种变压器驱动电路,包括:隔直电容、变压器、第一整流电路、第二整流电路、第一开关管驱动电路、第二开关管驱动电路、第一开关管和第二开关管;隔直电容用于隔离初始驱动信号中的直流分量,第一变压器副边输出第二驱动信号,第二变压器副边输出第三驱动信号;第一整流电路对第二驱动信号叠加直流分量;第一开关管驱动电路根据该驱动信号驱动第一开关管通断;第二整流电路对第三驱动信号叠加直流分量;第二开关管驱动电路根据该驱动信号驱动第二开关管通断。本发明通过两个整流电路调整占空比不对称的驱动信号电平的高低,使驱动信号的高低电平趋向对称,从而实现变压器驱动电路的互补驱动需求。

3、以及申请号为2016111685853的中国专利申请中公开了驱动电路,该驱动电路包括:变压器,变压器包括彼此磁耦合的第一线圈、第二线圈和第三线圈,第一线圈耦合至直流源,第二线圈耦合至恒流型负载;以及储能器,耦合至变压器。此外,该驱动电路还包括控制器,耦合至储能器,并且被配置成使得在第一时间段期间经由变压器的第一线圈和第三线圈将来自直流源的功率传输至储能器,在第二时间段期间经由变压器的第一线圈和第二线圈将功率从储能器传输至恒流型负载。

4、在使用半桥电路作为输出的时候能量传递和信号传递分开从而提高电路的灵活性,但往往输出信号的波形边缘会出现上升变缓的情况,从而影响电路的驱动性能。

技术实现思路

1、本申请针对上述技术问题提出抗噪抗干扰的驱动电路,具体技术方案如下:

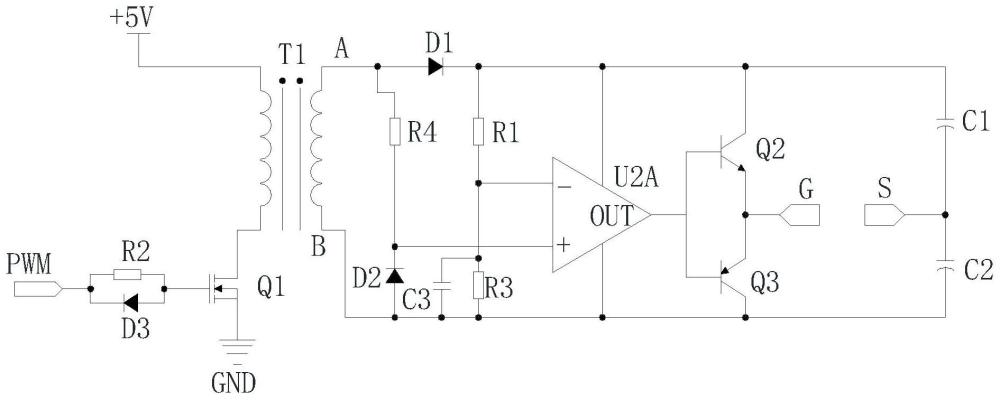

2、抗噪抗干扰的驱动电路,包括:

3、变压器t1;

4、输入端,与变压器t1初级绕组相连;

5、输出端,与变压器t1次级绕组相连,所述变压器t1的次级绕组之间接入图腾式输出电路,图腾式输出电路由npn型三极管q2和pnp型三极管q3组成,其中由npn型三极管q2的集电极与变压器t1的次级绕组a端相连,pnp型三极管q3的发射极与变压器t1的次级绕组b端相连,npn型三极管q2和pnp型三极管q3的基极相连并接入比较器u2a的输出端,npn型三极管q2和pnp型三极管q3的发射极相连形成输出端g,npn型三极管q2的集电极连接电容c1,pnp型三极管q的集电极连接电容c2,电容c1与电容c2相连形成输出端s,vgs作为输出信号;另外,npn型三极管q2的集电极与变压器t1的次级绕组a端之间连接有二极管d1,二极管d1的负极接入比较器u2a的一个输入端,且二极管d1与比较器u2a之间串联电阻r1,比较器u2a的另一个输入端与变压器t1的次级绕组b端相连,且比较器u2a与变压器t1的次级绕组b端之间串联二极管d2,比较器u2a与二极管d2的负极相连,同时二极管d2的负极与电阻r4相连,电阻r4的另一端与二极管d1的正极相连,变压器t1的次级绕组b端还连接电容c3和电阻r3,电容c3和电阻r3并联后与电阻r1相连。

6、进一步的,所述变压器t1的初级绕组一端与供电电源相连,另一端与场效应管q1漏极相连,场效应管q1的源极接地,场效应管q1的栅极与控制信号pwm输入相连,场效应管q1的栅极与控制信号pwm输入之间接入电阻r2和二极管d3,且电阻r2和二极管d3之间并联。

7、进一步的,电容c1与电容c2等值时,vgs输出正负电平对称的正负脉冲输出。

8、进一步的,电容c1与电容c2不等时,vgs输出正负电平不对称的正负脉冲输出。

9、本发明的有益效果为:本申请的抗噪抗干扰的驱动电路可以克服输出信号的波形边缘出现上升变缓的情况,使输出波形的边沿更陡峭抗干扰能力强,且可以控制输出正负脉冲电压。

技术特征:

1.抗噪抗干扰的驱动电路,其特征在于,包括:

2.根据权利要求1所述的抗噪抗干扰的驱动电路,其特征在于,所述变压器t1的初级绕组一端与供电电源相连,另一端与场效应管q1漏极相连,场效应管q1的源极接地,场效应管q1的栅极与控制信号pwm输入相连,场效应管q1的栅极与控制信号pwm输入之间接入电阻r2和二极管d3,且电阻r2和二极管d3之间并联。

3.根据权利要求1所述的抗噪抗干扰的驱动电路,其特征在于,电容c1与电容c2等值时,vgs输出正负电平对称的正负脉冲输出。

4.根据权利要求1所述的抗噪抗干扰的驱动电路,其特征在于,电容c1与电容c2不等时,vgs输出正负电平不对称的正负脉冲输出。

技术总结

本发明公开了抗噪抗干扰的驱动电路,包括:变压器T1;输入端,与变压器T1初级绕组相连;输出端,与变压器T1次级绕组相连,输出端接入图腾式输出电路以及比较器U2A,可以克服输出信号的波形边缘出现上升变缓的情况,使输出波形的边沿更陡峭抗干扰能力强,且可以控制输出正负脉冲电压。

技术研发人员:花峰,田瑶

受保护的技术使用者:苏州炬仁半导体有限公司

技术研发日:

技术公布日:2024/2/21

- 还没有人留言评论。精彩留言会获得点赞!