一种供电电路的制作方法

本发明涉及通讯,具体涉及一种供电电路。

背景技术:

1、现有1wi从芯片能够支持c类低压工作,但是由于电压余量不足,需要外接电容以在单线通信低电平期间为从芯片提供供电,同时芯片内部也需要超低功耗设计,从而提高了芯片成本和加大了芯片设计难度。另外需要1wi电源检测模块提供电平检测,控制时钟电路在通信低电平期间关闭,高电平期间开启,由于电源检测需要反应时间,时钟电路无法及时关闭,造成功耗无法控制在最低状态等问题。

技术实现思路

1、有鉴于此,本发明提供了一种供电电路,以解决由于电压余量不足,需要外接电容以在单线通信低电平期间为从芯片提供供电的问题。

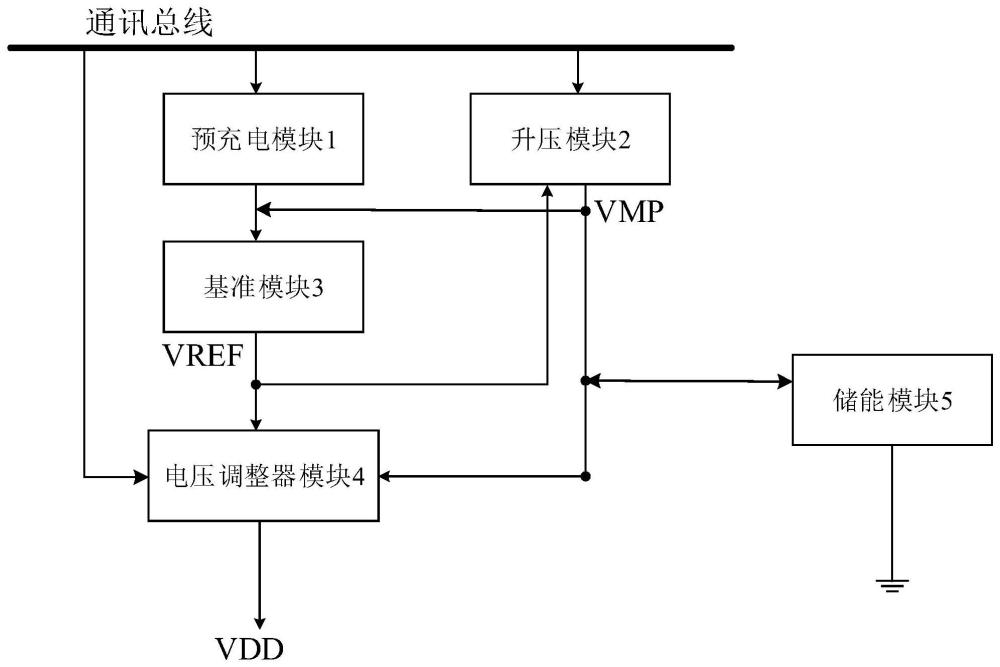

2、本发明提供了一种供电电路,供电电路集成于芯片中,供电电路包括:预充电模块、升压模块、基准模块、电压调整器模块及储能模块,其中,预充电模块,其第一端从通讯总线取能,其第二端与基准模块的第一端连接;芯片通过通讯总线与其它设备进行数据传输;升压模块,其第一端与通讯总线连接,其第二端与基准模块的第二端连接,其第三端与基准模块的第一端、储能模块的第一端、电压调整器模块的第一端连接;电压调整器模块,其第二端与基准模块的第二端连接,其第三端输出供电电压,其第四端与通讯总线连接,供电电压用于为芯片内部各模块供电;储能模块,其第二端接地;当芯片处于接收状态、且通讯总线接收到高电平时,预充电模块对基准模块预充电后,基准模块输出基准电压,升压模块将基准电压升压至预设电压后,预设电压使能电压调整器模块、为储能模块充电,电压调整器模块基于基准电压输出供电电压;当芯片处于接收状态、且通讯总线接收到低电平时,或者当芯片处于发送状态时,升压模块不再对基准电压升压,储能模块为基准模块及电压调整器模块,电压调整器模块基于基准电压输出供电电压。

3、本发明将通讯总线的电压进行升压后为芯片内部模块供电,从而解决了低压下内部电压余量不足问题,设计难度降低同时;也无需外部储能电容,节约了成本;同时升压模块电源自适应技术,无需电源检测模块,解决了电源检测模块响应速度带来的功耗浪费问题。

4、在一些可选的实施方式中,预充电模块包括:至少一个第一开关支路,其中,每个第一开关支路的第一端均从通讯总线取能,每个第一开关支路的第二端均与基准模块的第一端连接;通过控制第一开关支路的投入数量,控制对基准模块预充电的充电速度。

5、在一些可选的实施方式中,每个开关支路均包括:电力电子开关器件。

6、在一些可选的实施方式中,升压模块包括:时钟电路、至少一个升压子电路、电压检测电路,其中,时钟电路,其第一端与通讯总线连接,其第二端、第三端分别与升压子电路的控制端、控制端连接;全部的升压子电路串联连接后的第一端与基准模块的第二端连接,全部的升压子电路串联连接后的第二端与基准模块的第一端、储能模块的第一端、电压调整器模块的第一端连接;电压检测电路,其第一端与全部的升压子电路串联连接后的第二端连接,其第二端与时钟电路的使能端连接;当芯片处于接收状态、且通讯总线接收到高电平时,时钟电路输出时钟信号至升压子电路,全部的升压子电路对基准电压进行多级升压,电压检测电路检测到升压至预设电压时发送停止升压信号,时钟电路接收到停止升压信号后控制升压子电路不再升压;当芯片处于接收状态、且通讯总线接收到低电平时,或者当芯片处于发送状态时,时钟电路均不输出时钟信号至升压子电路。

7、本发明的升压模块内部的时钟电路能够自适应通讯总线及芯片不同状态,无需电源检测模块,解决了电源检测模块响应速度带来的功耗浪费问题。

8、在一些可选的实施方式中,升压子电路包括升压泵。

9、在一些可选的实施方式中,升压模块还包括:滤波电路,其第一端与全部的升压子电路串联连接后的第二端连接,其第二端接地。

10、在一些可选的实施方式中,滤波电路包括:滤波电容。

11、在一些可选的实施方式中,电压调整器模块包括:驱动电路、第二开关支路、第一下拉电阻及第二下拉电阻,其中,驱动电路,其第一端与升压模块的第三端、储能模块的第一端连接,其第二端与基准模块的第二端连接,其第三端与第二开关支路的控制端连接;第二开关支路,其第一端与通讯总线连接,其第二端与第一下拉电阻的第一端连接,第二端还输出供电电压;第一下拉电阻,其第二端与驱动电路的第四端连接,其第二端还通过第二下拉电阻接地;当芯片处于接收状态、且通讯总线接收到高电平时,升压模块输出预设电压,预设电压使能驱动电路,驱动电路驱动第二开关支路导通后,第二开关支路输出供电电压;当芯片处于接收状态、且通讯总线接收到低电平时,或者当芯片处于发送状态时,储能模块为基准模块及驱动电路供电驱动电路驱动第二开关支路导通后,第二开关支路输出供电电压;驱动电路还用于基于第一下拉电阻的第二端电压维持供电电压稳定。

12、在一些可选的实施方式中,驱动电路包括:运算放大器,其电源端与升压模块的第三端、储能模块的第一端连接,其同相输入端与基准模块的第二端连接,其反相输入端与第一下拉电阻的第二端连接,其输出端与第二开关支路的控制端连接。

13、在一些可选的实施方式中,第二开关支路包括:nmos管。

14、在一些可选的实施方式中,储能模块包括:储能电容。

技术特征:

1.一种供电电路,其特征在于,所述供电电路集成于芯片中,所述供电电路包括:预充电模块、升压模块、基准模块、电压调整器模块及储能模块,其中,

2.根据权利要求1所述的供电电路,其特征在于,所述预充电模块包括:至少一个第一开关支路,其中,

3.根据权利要求2所述的供电电路,其特征在于,每个所述开关支路均包括:电力电子开关器件。

4.根据权利要求1所述的供电电路,其特征在于,所述升压模块包括:时钟电路、至少一个升压子电路、电压检测电路,其中,

5.根据权利要求4所述的供电电路,其特征在于,所述升压子电路包括升压泵。

6.根据权利要求4所述的供电电路,其特征在于,所述升压模块还包括:

7.根据权利要求6所述的供电电路,其特征在于,所述滤波电路包括:滤波电容。

8.根据权利要求1所述的供电电路,其特征在于,所述电压调整器模块包括:驱动电路、第二开关支路、第一下拉电阻及第二下拉电阻,其中,

9.根据权利要求8所述的供电电路,其特征在于,所述驱动电路包括:

10.根据权利要求8所述的供电电路,其特征在于,所述第二开关支路包括:nmos管。

11.根据权利要求1所述的供电电路,其特征在于,所述储能模块包括:储能电容。

技术总结

本发明涉及通讯技术领域,公开了一种供电电路,升压模块将通讯总线的电压进行升压后为芯片内部模块供电,从而解决了低压下内部电压余量不足问题,设计难度降低同时;也无需外部储能电容,节约了成本;同时升压模块电源自适应技术,无需电源检测模块,解决了电源检测模块响应速度带来的功耗浪费问题。

技术研发人员:刘明磊,柳雪晶,张昱桐,李建波,邹锦,陈艳

受保护的技术使用者:北京中电华大电子设计有限责任公司

技术研发日:

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!