栅极驱动器电路的制作方法

本揭示涉及一种栅极驱动器电路。

背景技术:

1、单相桥接电路、h桥接电路、3相桥接电路等开关电路具备包含高侧臂与低侧臂的引线。高侧臂及低侧臂具备并联连接的功率晶体管及飞轮二极管。

2、各引线能切换高侧晶体管导通、低侧晶体管断开的高输出状态、与高侧晶体管断开、低侧晶体管导通的低输出状态。在从高输出状态向低输出状态转移,或从低输出状态向高输出状态转移的中途,如果高侧晶体管与低侧晶体管同时导通,那么贯通电流流动。为了防止所述贯通电流,对于从高输出状态向低输出状态的转移,或从低输出状态向高输出状态的转移,插入高侧晶体管与低侧晶体管这两个断开的高阻抗状态。所述高阻抗状态称为空载时间。

3、在驱动开关电路的栅极驱动器电路,安装自动插入空载时间的功能。此外,栅极驱动器电路具备用来设定空载时间的长度的设定引脚,用户能从外部设定空载时间的长度。

技术实现思路

1、[发明所要解决的问题]

2、有时不委托栅极驱动器电路产生空载时间,而想要在栅极驱动器电路外部的控制器电路中产生。以往在这种情况下,用户以栅极驱动器电路内部的空载时间的长度成为零的方式,设定栅极驱动器电路的设定引脚的状态。

3、然而,以往的栅极驱动器电路难以使在内部产生的空载时间的长度完全为零。因此,对在外部设定的空载时间加上非零的内部的空载时间,有导致空载时间变长的问题。较长的空载时间招致效率降低。

4、本揭示是鉴于所述问题而完成的,其某方面的例示性目的之一在于提供一种能使在栅极驱动器电路内部产生的空载时间(内部空载时间)的长度接近零的栅极驱动器电路。

5、[解决问题的技术方式]

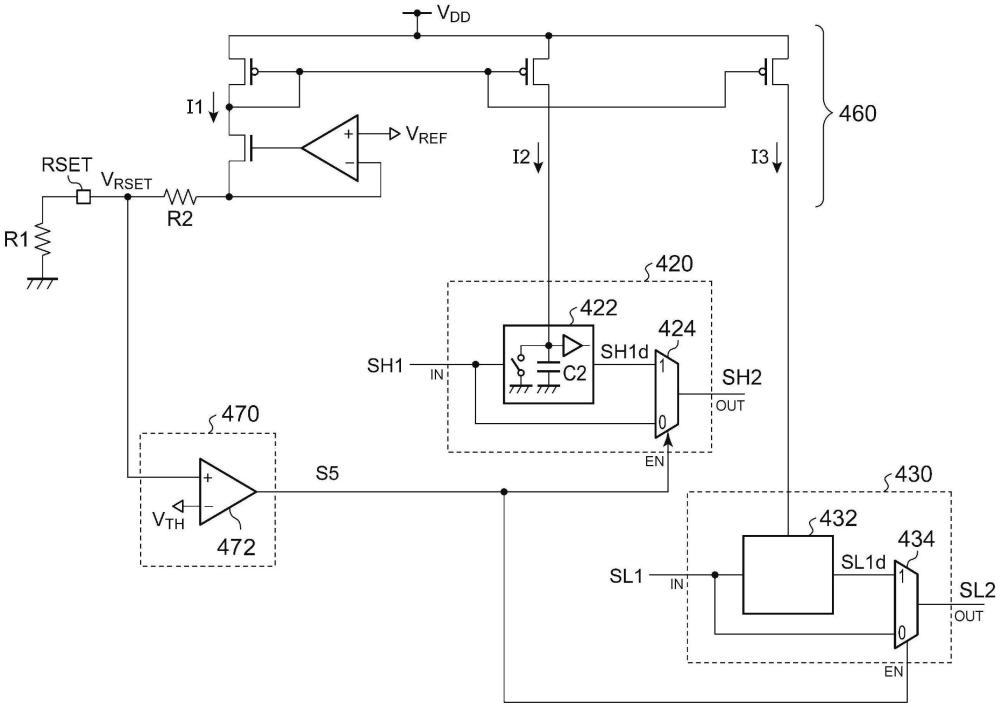

6、本揭示的某方面涉及一种栅极驱动器电路。栅极驱动器电路具备:逻辑电路,指定驱动对象的高侧晶体管及低侧晶体管的状态的每一个接收二值的第1控制输入及第2控制输入,根据第1控制输入及第2控制输入的信号电平的组合,产生规定高侧晶体管的导通、断开的第1高侧控制信号、与规定低侧晶体管的导通、断开的第1低侧控制信号;设定引脚,应将外部电阻连接;高侧用空载时间电路,接收第1高侧控制信号,产生第2高侧控制信号;低侧用空载时间电路,接收第1低侧控制信号,产生第2低侧控制信号;高侧选择器,接收第1高侧控制信号与第2高侧控制信号,在高侧晶体管的关断动作时选择第1高侧控制信号,在高侧晶体管的接通动作时选择第2高侧控制信号;及低侧选择器,接收第1低侧控制信号与第2低侧控制信号,在低侧晶体管的关断动作时选择第1低侧控制信号,在低侧晶体管的接通动作时选择第2低侧控制信号。高侧用空载时间电路包含:高侧用模拟延迟电路,将第1高侧控制信号延迟与外部电阻的电阻值对应的延迟时间,产生延迟高侧控制信号;及高侧用选择器,接收第1高侧控制信号与延迟高侧控制信号,选择与设定引脚的电状态对应的一个,作为第2高侧控制信号输出。低侧用空载时间电路包含:低侧用模拟延迟电路,将第1低侧控制信号延迟与外部电阻的电阻值对应的延迟时间,产生延迟低侧控制信号;及低侧用选择器,接收第1低侧控制信号与延迟低侧控制信号,选择与设定引脚的电状态对应的一个,作为第2低侧控制信号输出。

7、另外,任意组合以上的构成要件的方面、将构成要件或表现在方法、装置、系统等之间互相置换的方面也作为本发明或本揭示的方面有效。而且,所述项目(解决问题的技术方式)的记载并非说明本发明不可欠缺的所有特征,因此,记载的这些特征的子组合也可为本发明。

8、[发明的效果]

9、根据本揭示的某方面,能使栅极驱动器电路内部的空载时间接近零。

技术特征:

1.一种栅极驱动器电路,具备:

2.根据权利要求1所述的栅极驱动器电路,还具备产生与所述外部电阻的电阻值对应的充电电流的模拟调节电路,

3.根据权利要求2所述的栅极驱动器电路,还具备将所述设定引脚的电压与阈值电压进行比较的比较器,

4.根据权利要求2或3所述的栅极驱动器电路,其中所述模拟调节电路包含:

5.根据权利要求1到4中任一权利要求所述的栅极驱动器电路,用于电动机的驱动。

6.根据权利要求1到5中任一权利要求所述的栅极驱动器电路,在一个半导体衬底一体集成化。

技术总结

本揭示涉及一种栅极驱动器电路。本揭示的目的在于使在栅极驱动器电路内部产生的空载时间的长度接近零。在设定引脚连接外部电阻。高侧用空载时间电路接收第1高侧控制信号,产生第2高侧控制信号。模拟延迟电路将第1高侧控制信号延迟与外部电阻的电阻值对应的延迟时间,产生延迟高侧控制信号。选择器接收第1高侧控制信号与延迟高侧控制信号,选择与设定引脚的电状态对应的一个,作为第2高侧控制信号输出。

技术研发人员:杉江尚

受保护的技术使用者:罗姆股份有限公司

技术研发日:

技术公布日:2024/8/21

- 还没有人留言评论。精彩留言会获得点赞!