半桥功率电路、用于半桥功率电路的控制器和控制方法与流程

1.本发明涉及一种半桥功率电路、用于半桥功率电路的控制器、以及控制半桥功率电路的方法。具体地,本发明涉及具有可控的空置时间的半桥功率电路,以及控制半桥功率电路的空置时间的方法。

背景技术:

2.半桥功率电路通过交替地闭合上部开关(high-side switch,hs)和下部开关(low-side switch,ls)来产生方波信号。图1所示是一种半桥功率电路100及施加在其开关上的控制信号。半桥功率电路100包括上部开关(hs)102和下部开关(ls)104。hs 102和ls 104串联连接在供电电源和地之间,交替地闭合以从输入电压v2中产生输出电压v1。信号106施加到hs 102,信号108施加到ls 104,以控制各开关处于导通/关断状态。

3.如图1所示的,hs 102和ls 104不同时闭合,以避免供电电源与地之间短路,该短路情况通常被称为直通(shoot-through)。具体地,在信号106的导通on状态和随后的信号108的导通on状态之间,存在一个时间间隔。因此,hs 102和ls 104的导通之间存在延迟时间,以保证hs 102和ls 104不同时导通。该时间间隔,亦称为空置时间,有必要被控制得越短越好,以使功率损失最小。此外,该空置时间还应当在防止直通的情况下足够充足来容许制程、电压、温度(process,voltage,temperature,pvt)的变化。

技术实现要素:

4.本发明内容被提供以介绍以下具体实施方式部分详述的概念中经选择的简化部分。本发明内容并不意欲确定权利要求中内容的关键或必要特征,亦不意欲使其限制权利要求的范围。

5.根据一种实施方式,一种用于半桥功率电路的控制器,其中所述半桥功率电路包括上部开关和下部开关,上部开关和下部开关串联连接在供电电压和地之间,上部开关和下部开关之间的半桥节点提供半桥电压;所述控制器包括:

6.测量电路,配置为连接到半桥节点,其中测量电路配置为测量半桥电压,以及产生能够表示所测量的半桥电压的多位状态信号;

7.连接到测量电路的控制器电路,控制器电路配置为从测量电路接收状态信号,其中控制器电路配置为基于状态信号产生至少一个延迟控制信号;

8.连接到控制器电路以接收延迟控制信号的上部延迟电路,其中上部延迟电路配置为响应于延迟控制信号而提供上部控制信号,以将上部开关导通/关断;以及

9.连接到控制器电路以接收延迟控制信号的下部延迟电路,其中下部延迟电路配置为响应于延迟控制信号而提供下部控制信号,以将下部开关导通/关断。

10.在一个或多个实施方式中:控制器电路配置为响应于状态信号而产生上升空置时间设置信号作为延迟控制信号,以及其中上部延迟电路包括:

11.上部导通on延迟电路,配置为从控制器电路接收上升空置时间设置信号,以及据

以产生上部导通on信号;

12.上部缓冲器电路,配置为接收pwm信号的翻转信号,以及响应于pwm信号的翻转信号而产生上部关断off信号;以及

13.连接到上部导通on延迟电路和上部缓冲器电路的上部触发器电路,配置为基于上部导通on信号和上部关断off信号而产生上部控制信号。

14.在一个或多个实施方式中:所述控制器进一步包括连接到上部延迟电路以接收上部控制信号的上部驱动器电路;其中

15.上部驱动器电路配置为响应于上部控制信号而产生上部驱动器信号,以及提供上部驱动器信号以控制上部开关;以及其中

16.控制器电路进一步配置为响应于状态信号而产生上部转换速率控制信号;以及

17.上部驱动器电路进一步连接到控制器电路以接收上部转换速率控制信号,以及其中上部驱动器信号基于上部转换速率控制信号而产生。

18.在一个或多个实施方式中,下部延迟电路包括:

19.下部关断off延迟电路,配置为从控制器电路接收上升空置时间设置信号,以及据以产生下部关断off信号;

20.下部导通on延迟电路,配置为接收pwm信号的翻转信号,以及响应于pwm信号的翻转信号而产生下部导通on信号;以及

21.连接到下部关断off延迟电路和下部导通on延迟电路的下部触发器电路,配置为基于下部关断off信号和下部导通on信号而产生下部控制信号;

22.其中控制器进一步包括连接到下部延迟电路以接收下部控制信号的下部驱动器电路,下部驱动器电路配置为响应于下部控制信号而产生下部驱动器信号,以及提供下部驱动器信号以控制下部开关。

23.在一个或多个实施方式中:控制器电路配置为响应于状态信号而产生下降空置时间设置信号作为延迟控制信号,以及其中下部延迟电路包括:

24.下部导通on延迟电路,配置为从控制器电路接收下降空置时间设置信号,以及据以产生下部导通on信号;

25.下部缓冲器电路,配置为接收pwm信号,以及响应于pwm信号而产生下部关断off信号;以及

26.连接到下部导通on延迟电路和下部缓冲器电路的下部触发器电路,配置为基于下部导通on信号和下部关断off信号而产生下部控制信号。

27.在一个或多个实施方式中:所述控制器进一步包括连接到下部延迟电路以接收下部控制信号的下部驱动器电路;其中

28.下部驱动器电路配置为响应于下部控制信号而产生下部驱动器信号,以及将下部驱动器信号提供给下部开关,以及其中

29.控制器电路进一步配置为响应于状态信号而产生下部转换速率控制信号;以及

30.下部驱动器电路进一步连接到控制器电路以接收下部转换速率控制信号,以及其中下部驱动器信号基于下部转换速率控制信号而产生。

31.在一个或多个实施方式中,上部延迟电路包括:

32.上部关断off延迟电路,配置为从控制器电路接收下降空置时间设置信号,以及据

以产生上部关断off信号;

33.上部导通on延迟电路,配置为接收pwm信号,以及响应于pwm信号而产生上部导通on信号;以及

34.连接到上部关断off延迟电路和上部导通on延迟电路的上部触发器电路,配置为基于上部关断off信号和上部导通on信号而产生上部控制信号;

35.其中控制器进一步包括连接到上部延迟电路以接收上部控制信号的上部驱动器电路,上部驱动器电路配置为响应于上部控制信号而产生上部驱动器信号,以及将上部驱动器信号提供给上部开关。

36.在一个或多个实施方式中:控制器电路配置为响应于第一状态信号而产生上升空置时间设置信号,以及响应于第二状态信号而产生下降空置时间设置信号,以及其中上部延迟电路包括:

37.上部导通on延迟电路,配置为接收来自控制器电路的下降空置时间设置信号和接收pwm信号,以及据以产生上部导通on信号;

38.上部关断off延迟电路,配置为接收来自控制器电路的上升空置时间设置信号和接收pwm信号的翻转信号,以及据以产生上部关断off信号;以及

39.连接到上部导通on延迟电路和上部关断off延迟电路的上部触发器电路,配置为基于上部导通on信号和上部关断off信号而产生上部控制信号。

40.在一个或多个实施方式中:所述控制器进一步包括连接到上部延迟电路以接收上部控制信号的上部驱动器电路,其中

41.控制器电路进一步配置为响应于状态信号而产生上部转换速率控制信号,以及将上部转换速率控制信号提供给上部驱动器电路;以及其中

42.上部驱动器电路配置为基于上部控制信号和上部转换速率控制信号而产生上部驱动器信号,以及将上部驱动器信号提供给上部开关。

43.在一个或多个实施方式中:控制器电路配置为响应于第一状态信号而产生上升空置时间设置信号,以及响应于第二状态信号而产生下降空置时间设置信号,以及其中下部延迟电路包括:

44.下部导通on延迟电路,配置为接收来自控制器电路的上升空置时间设置信号和接收pwm信号的翻转信号,以及据以产生下部导通on信号;

45.下部关断off延迟电路,配置为接收来自控制器电路的下降空置时间设置信号和接收pwm信号,以及据以产生下部关断off信号;以及

46.连接到下部导通on延迟电路和下部关断off延迟电路的下部触发器电路,配置为基于下部导通on信号和下部关断off信号而产生下部控制信号。

47.在一个或多个实施方式中:所述控制器进一步包括连接到下部延迟电路以接收下部控制信号的下部驱动器电路,其中

48.控制器电路进一步配置为响应于状态信号而产生下部转换速率控制信号,以及将下部转换速率控制信号提供给下部驱动器电路;以及其中

49.下部驱动器电路配置为基于下部控制信号和下部转换速率控制信号而产生下部驱动器信号,以及将下部驱动器信号提供给下部开关。

50.在一个或多个实施方式中:上部延迟电路配置为提供上部控制信号以在导通/关

断上部开关时施加延迟,下部延迟电路配置为提供下部控制信号以在导通/关断下部开关时施加延迟;其中在半桥电压的上升阶段:

51.上部延迟电路配置为提供上部控制信号来

52.响应于状态信号表示半桥电压被测量为低于第一下限电压而将导通上部开关的延迟减小;以及

53.响应于状态信号表示半桥电压被测量为高于第一上限电压而将导通上部开关的延迟增大;

54.以及下部延迟电路配置为提供下部控制信号来

55.响应于状态信号表示半桥电压被测量为低于第一下限电压而将关断下部开关的延迟增大;以及

56.响应于状态信号表示半桥电压被测量为高于第一上限电压而将关断下部开关的延迟减小。

57.在一个或多个实施方式中:上部延迟电路配置为提供上部控制信号以在导通/关断上部开关时施加延迟,下部延迟电路配置为提供下部控制信号以在导通/关断下部开关时施加延迟;其中在半桥电压的下降阶段:

58.下部延迟电路配置为提供下部控制信号来

59.响应于状态信号表示半桥电压被测量为高于第二上限电压而将导通下部开关的延迟减小;以及

60.响应于状态信号表示半桥电压被测量为低于第二下限电压而将导通下部开关的延迟增大;

61.以及上部延迟电路配置为提供上部控制信号来

62.响应于状态信号表示半桥电压被测量为高于第二上限电压而将关断上部开关的延迟增大;以及

63.响应于状态信号表示半桥电压被测量为低于第二下限电压而将关断上部开关的延迟减小。

64.根据一种实施方式,一种运行半桥功率电路的方法,其中半桥功率电路包括连接在供电电压和半桥节点之间的上部开关、以及连接在上部开关和地之间的下部开关;所述方法包括:

65.连接到半桥节点的测量电路测量半桥节点上的半桥电压,以及产生能够表示所测量的半桥电压的多位状态信号;

66.连接到测量电路的控制器电路基于状态信号产生至少一个延迟控制信号;

67.连接到控制器电路的上部延迟电路使用延迟控制信号产生上部控制信号,其中上部开关基于上部控制信号而导通/关断;

68.连接到控制器电路的下部延迟电路使用延迟控制信号产生下部控制信号,其中下部开关基于下部控制信号而导通/关断;以及

69.半桥节点提供半桥功率电路的半桥电压。

70.在一个或多个实施方式中,产生多位状态信号包括:

71.测量电路将半桥电压与第一参考电压比较,以及产生能够表示半桥电压是否高于第一参考电压的状态信号的第一位;

72.测量电路将半桥电压与至少一个第二参考电压比较,以及产生能够表示半桥电压是否高于第二参考电压的状态信号的第二位;以及

73.测量电路将第一位和至少所述第二位提供为状态信号。

74.在一个或多个实施方式中,所述方法进一步包括:

75.在半桥电压的上升阶段,控制器电路将多位状态信号的值与对应于第一下限电压的第一下限值比较,以确定半桥电压是否低于第一下限电压;以及

76.上部延迟电路使用延迟控制信号来产生上部控制信号,以响应于半桥电压低于第一下限电压而从当前第一延迟时间中减小预定的延迟时间;

77.其中所述方法进一步包括:上部开关响应于上部控制信号来通过施加第一延迟时间而导通;

78.以及其中所述方法进一步包括:

79.在半桥电压的上升阶段,下部延迟电路使用延迟控制信号来产生下部控制信号,以响应于半桥电压低于第一下限电压而向当前第二延迟时间中增加预定的延迟时间;以及

80.下部开关响应于下部控制信号来通过施加第二延迟时间而关断。

81.在一个或多个实施方式中,所述方法进一步包括:

82.在半桥电压的上升阶段,控制器电路将多位状态信号的值与对应于第一上限电压的第一上限值比较,以确定半桥电压是否高于第一上限电压;以及

83.上部延迟电路使用延迟控制信号来产生上部控制信号,以响应于半桥电压高于第一上限电压而向当前第一延迟时间中增加预定的延迟时间;

84.其中所述方法进一步包括:

85.在半桥电压的上升阶段,下部延迟电路使用延迟控制信号来产生下部控制信号,以响应于半桥电压高于第一上限电压而从当前第二延迟时间中减小预定的延迟时间。

86.在一个或多个实施方式中,所述方法进一步包括:

87.在半桥电压的下降阶段,控制器电路将多位状态信号的值与对应于第二上限电压的第二上限值比较,以确定半桥电压是否高于第二上限电压;以及

88.下部延迟电路使用延迟控制信号来产生下部控制信号,以响应于半桥电压高于第二上限电压而从当前第三延迟时间中减小预定的延迟时间;

89.其中所述方法进一步包括:下部开关响应于下部控制信号来通过施加第三延迟时间而导通;

90.以及其中所述方法进一步包括:

91.在半桥电压的上升阶段,上部延迟电路使用延迟控制信号来产生上部控制信号,以响应于半桥电压高于第二上限电压而向当前第四延迟时间中增加预定的延迟时间;以及

92.上部开关响应于上部控制信号来通过施加第四延迟时间而关断。

93.在一个或多个实施方式中,所述方法进一步包括:

94.在半桥电压的下降阶段,控制器电路将多位状态信号的值与对应于第二下限电压的第二下限值比较,以确定半桥电压是否低于第二下限电压;以及

95.下部延迟电路使用延迟控制信号来产生下部控制信号,以响应于半桥电压低于第二下限电压而向当前第三延迟时间中增加预定的延迟时间;

96.其中所述方法进一步包括:

97.在半桥电压的下降阶段,上部延迟电路使用延迟控制信号来产生上部控制信号,以响应于半桥电压低于第二下限电压而从当前第四延迟时间中减小预定的延迟时间。

98.在一个或多个实施方式中,所述方法进一步包括:

99.控制器电路响应于状态信号而产生上部转换速率控制信号和下部转换速率控制信号;

100.控制器电路将上部转换速率控制信号提供给上部驱动器电路;

101.控制器电路将下部转换速率控制信号提供给下部驱动器电路;

102.上部驱动器电路基于上部控制信号和上部转换速率控制信号而产生上部驱动器信号,以及使用上部驱动器信号驱动上部开关;以及

103.下部驱动器电路基于下部控制信号和下部转换速率控制信号而产生下部驱动器信号,以及使用下部驱动器信号驱动下部开关。

附图说明

104.为使本发明前述内容可以更具体的方式得以理解,本发明的进一步详细的描述可以参考实施方式而得到,其中部分由所附的图例而展示。所附图例仅展示本发明的典型实施方式,且因本发明可以具有其他相同地有效实施方式,所附图例不应理解为限制本发明的范围。附图是为便于理解而非测量本发明而绘制。对于本领域的技术人员而言,在阅读了本描述并结合所附图例,所要求的发明主题的益处将易于理解。在附图中,相似的标记数字被用来指示相似的元件,以及:

105.图1是一种半桥功率电路和施加到其开关上的控制信号;

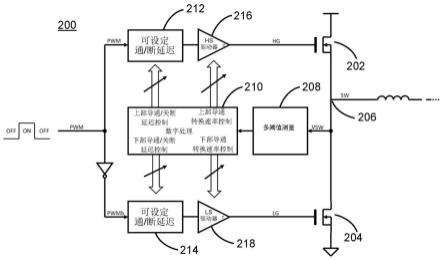

106.图2是包括半桥功率电路和根据一种实施方式的控制器的系统的框图;

107.图3是半桥功率电路和图2的控制器的电路图;

108.图4是根据一种实施方式的测量电路的电路图;

109.图5是根据一种实施方式的延时电路的电路图;

110.图6是根据一种实施方式的控制器产生延时控制信号和转换速率控制信号的方法的流程图;

111.图7是根据一种实施方式的输入信号、输出信号和施加到开关的控制信号的波形图;

112.图8是输入pwm信号和控制信号的波形图;

113.图9是根据一种实施方式的驱动器电路的电路图;

114.图10a是未调整控制信号中的延迟时间的输出信号的波形图;

115.图10b是根据一种实施方式的调整了延迟时间的输出信号的波形图;

116.图11是半桥功率电路和根据另一实施方式的控制器的框图;以及

117.图12是半桥功率电路和根据另一实施方式的控制器的框图。

具体实施方式

118.图2所示的是根据一个或多个实施方式的系统200的框图,系统200包括半桥功率电路和控制器。半桥功率电路包括上部开关(hs)202和下部开关(ls)204,hs 202和ls 204串联连接在供电电源和地之间。在hs 202和ls 204之间的半桥节点206提供半桥电压sw,典

型地,半桥电压sw是方波。

119.图2的系统200还包括控制器,控制器包括用于连接到半桥节点206的测量电路208、控制器电路210、上部延迟电路212、下部延迟电路214、上部驱动器电路216、以及下部驱动器电路218。测量电路208测量半桥电压vsw。作为响应,测量电路208产生多位的状态信号,其表征所测量的半桥电压vsw。

120.测量电路208将状态信号提供给控制器的控制器电路210。控制器电路210连接到测量电路以接收状态信号,并基于该状态信号产生至少一个延迟控制信号。控制器电路210将所产生的延迟控制信号提供给上部延迟电路212和下部延迟电路214。上部延迟电路212和下部延迟电路214均连接到控制器电路210。如图2所示的,控制器电路210可以实现为数字处理电路,其能够处理数字化的多位状态信号。在图2所示的实施方式中,上部延迟电路212和下部延迟电路214是可设置开关延迟电路,其接收开关信号pwm,并向开关信号中引入延迟,该延迟根据从控制器电路210所接收的延迟控制信号而设置。作为响应,上部延迟电路212产生上部控制信号,而下部延迟电路214产生下部控制信号。

121.连接到上部延迟电路212的上部驱动器电路216接收上部控制信号,连接到下部延迟电路214的下部驱动器电路218接收下部控制信号。上部驱动器电路216进一步地连接到上部开关202,以提供上部驱动器信号,该上部驱动器信号响应于上部控制信号而产生。来自上部驱动器电路216的上部驱动器信号将上部开关202闭合/关断。类似地,下部驱动器电路218进一步地连接到下部开关204,以提供下部驱动器信号,该下部驱动器信号响应于下部控制信号而产生。来自下部驱动器电路218的下部驱动器信号将下部开关204闭合/关断。

122.如图2所示的,根据本实施方式,控制器电路210响应于来自测量电路208的状态信号而进一步地产生上部转换速率控制信号,并将上部转换速率控制信号提供给上部驱动器电路216。上部驱动器电路216连接到控制器电路210以接收上部转换速率控制信号,并据此而基于上部控制信号和上部转换速率控制信号来产生上部驱动器信号。亦如图2所示的,控制器电路210响应于来自测量电路208的状态信号而产生下部转换速率控制信号,并将下部转换速率控制信号提供给下部驱动器电路218。下部驱动器电路218连接到控制器电路210以接收下部转换速率控制信号,并据此而基于下部控制信号和下部转换速率控制信号来产生下部驱动器信号。

123.图3是图2中的系统200的更详细的示图。在系统200的控制器中,测量电路208包括第一测量电路222和第二测量电路224,第一测量电路222和第二测量电路224均连接到半桥节点206以接收半桥电压sw。对应地,第一测量电路222测量半桥电压vsw中的上升沿,而第二测量电路224测量半桥电压sw中的下降沿。第一测量电路222和第二测量电路224分别产生表征所测量的上升沿/下降沿的状态信号。

124.如图3所示的,控制器电路210包括第一控制器226和第二控制器228。整体而言,第一控制器226连接到第一测量电路222以接收状态信号,并被用来响应于来自第一测量电路222的状态信号表明半桥电压sw中的上升沿被测量而产生上升空置时间设置信号,以控制上部开关202。第二控制器228连接到第二测量电路224以接收状态信号,并被用来响应于来自第二测量电路224的状态信号表明半桥电压sw中的下降沿被测量而产生下降空置时间设置信号,以控制下部开关204。如图2所示的,第一控制器226和第二控制器228可以实现为数字积分器。

125.上部延迟电路212包括上部导通on延迟电路232、上部关断off延迟电路234、以及上部触发器电路236。上部导通on延迟电路232从第二控制器228接收下降空置时间设置信号以及pwm信号,并作为响应而产生上部导通on信号hs_on。上部导通on延迟电路232将上部导通on信号hs_on提供给上部触发器电路236。上部关断off延迟电路234从第一控制器226接收上升空置时间设置信号和pwm信号的反信号pwmb,并作为响应而产生上部关断off信号hs_off。上部关断off延迟电路234将上部关断off信号hs_off提供给上部触发器电路236。上部触发器电路236具有第一输入端s和第二输入端r,第一输入端s连接到上部导通on延迟电路232以接收上部导通on信号hs_on,第二输入端r连接到上部关断off延迟电路234以接收上部关断off信号hs_off。上部触发器电路236产生上部控制信号作为响应,并将上部控制信号提供给上部驱动器电路216。

126.亦如图3中所示的,下部延迟电路214包括下部导通on延迟电路242、下部关断off延迟电路244、以及下部触发器电路246。下部导通on延迟电路242从第一控制器226接收上升空置时间设置信号以及pwm信号的反信号pwmb,并作为响应而产生下部导通on信号ls_on。下部导通on延迟电路242将下部导通on信号ls_on提供给下部触发器电路246。下部关断off延迟电路244从第二控制器228接收下降空置时间设置信号以及pwm信号,并作为响应产生下部关断off信号ls_off。下部关断off延迟电路244将下部关断off信号ls_off提供给下部触发器电路246。下部触发器电路246具有第一输入端s和第二输入端r,第一输入端s连接到下部导通on延迟电路242以接收下部导通on信号ls_on,第二输入端r连接到下部关断off延迟电路244以接收下部关断off信号ls_off。下部触发器电路246产生下部控制信号作为响应,并将下部控制信号提供给下部驱动器电路218。

127.图4示出了根据一种实施方式的用于测量半桥电压sw中的上升沿的测量电路的电路图。测量电路400可以实施为图3中的第一测量电路222。测量电路400从半桥节点206接收半桥电压sw,并测量其电压vsw。在所示的实施方式中,测量电路400将电压vsw与多个(n个)参考电压vt_rise《1》到vt_rise《n》进行比较,以确定电压vsw是否高于各个对应的参考电压。具体地,测量电路400包括n个比较器402,每个比较器402接收半桥电压sw和相应一个参考电压。每个比较器402将半桥电压sw的电压vsw与对应的参考电压进行比较,并各自产生表示其比较结果的比较器输出信号。

128.测量电路400进一步包括多个(n个)触发器电路404,每个触发器电路404对应于一个比较器402,以及每个触发器电路404可以实施为所示的置位复位锁存器(set-reset latch,sr锁存器)。每个触发器电路404在其置位端(或称s端)接收来自对应的比较器402的比较器输出信号,以及在其复位端(或称r端)接收pwm信号的反信号pwmb。每个触发器电路404各产生状态信号中的n比特位中的一位。在pwm信号的一个周期中,如果半桥电压vsw不高于对应的参考电压,则s端为高,从而该触发器电路404据以产生一位“1”。另一方面,若半桥电压sw的电压vsw高于对应的参考电压,则s端为低,从而相对应的触发器电路404保持其缺省位“0”作为输出。状态信号在pwm信号的下一周期的开始时,对应于pwm转为低的时刻(故此pwmb转为高,将r端置为高以将锁存器复位),复位为多个比特位“0”。

129.应当理解的是,测量半桥电压sw的下降沿的测量电路224的实施可以与图4的测量电路400具有类似的配置。然而,为测量半桥电压sw中的下降沿,比较器在其反相输入端接收半桥电压sw,以及在正输入端接收参考电压。另外,为测量半桥电压sw中的下降沿,触发

器电路在r端接收pwm信号。

130.图5是根据一种实施方式的延迟电路500的电路图。延迟电路500可以是图2中的上部延迟电路212的一种实施示例,或者是图3中所示的上部导通on延迟电路232的一种实施示例。延迟电路500自控制器电路212接收延迟控制信号,以及使用延迟控制信号中的每一位来确定是否向所接收的输入信号in中施加对应的延迟。具体地,延迟电路500包括反相器502,反相器502接收温度计码的延迟控制信号on_delay_ctrl,并将延迟控制信号中的每一位翻转,成为翻转延迟控制信号on_delay_ctrl_b。温度计码信号是指信号的值等于信号中的位“1”的数量的信号。例如,温度计码信号“001111”的值是4,温度计码信号“0000111”的值是3。延迟控制电路500还包括多个延迟单元504以及对应的多个复用器mux电路506。多个延迟单元504串联连接,每个延迟单元504向经过了前级延迟单元504的延迟的输入信号in施加预定的延迟。每个延迟单元504的输入和输出均被提供给对应的复用器mux电路506,复用器mux电路506接收翻转延迟控制信号on_delay_ctrl_b中的对应一位,并使用该接收的位来确定是否将对应的延迟单元504所引入的延迟施加到输入信号in上。

131.作为示例,温度计码延迟控制信号on_delay_ctrl的“000011”将被反相器502转换为翻转延迟控制信号on_delay_ctrl_b而成为“111100”。随后,由于在翻转延迟控制信号on_delay_ctrl_b中有4个位“1”,4倍的预定延迟将被引入到输入信号in中,以成为延迟电路500的最终输出信号out。上部关断off延迟电路234和下部关断off延迟电路的实施方式具有与图5中的延迟控制电路500类似的配置,但不包括用来翻转温度计码延迟控制信号off_delay_ctrl的反相器。

132.回到图1,通常而言半桥功率电路100运行于第一阶段122、第二阶段124、第三阶段126和第四阶段128,在第一阶段122中hs 102和ls 104均处于关断状态,在第二阶段124中hs 102导通而ls 104保持关断,在第三阶段126中hs 102关断而ls 104保持关断,在第四阶段128中hs 102保持关断而ls 104导通。半桥功率电路100重复地运行于该四个阶段,据此,在第一阶段122和第三阶段126中hs 102和ls 104均关断,这被称为“空置时间”。可以理解的是:在第一阶段122中,hs 102被延迟导通,直至第二阶段124的起始;在第三阶段126中,ls 104被延迟导通,直至第四阶段128的起始。另一方面,在第三阶段126中hs 102关断,在第一阶段中ls 104关断,需要的是延迟将hs 102或ls 104转为关断,这是出于金属氧化物场效应晶体管mosfet的体二极管的反向恢复电流的原因,其将在下文中进一步详细描述。

133.图6所示的是一种实施方式中由例如图3中的第一控制器226产生延迟控制信号的方法的流程图。在此,该方法将参照测量半桥电压vsw中的上升沿的第一测量电路222、以及参照展示图3中的系统200的信号的附图7来描述。方法始自阶段702,阶段702可以是如上所述的第四阶段,其中hs 202和ls 204均响应于施加在其控制端上的低电平控制信号lg、hs而处于关断状态。如图7所示,在第四阶段702中,下部开关控制信号lg为低以试图关断ls 204,在ls 204中将出现反向恢复电流,导致ls 204两端产生负电压降。如图7中的标记704所示,在半桥节点206上的半桥电压vsw变得低于地电平。

134.在第四阶段702中的负电压降是ls 204中的体二极管导通的结果。在随后的第一阶段706中,hs 202开始响应于施加到其控制端上的控制信号hg上升而导通,半桥电压sw的电压vsw开始从开关的体二极管仍导通的状况下的负电压水平上开始上升,这将浪费效率,亦称为“反向恢复损失”。测量电路222对半桥电压vsw进行测量,并据以调整施加到hs 202

上的控制信号hg转变为高电平之前的时间阶段702。经调整的时间阶段702将有利于避免半桥电压vsw从很低的负电压上开始增长,因而半桥功率电路的整体效率能够提升。在本实施方式中,半桥电压vsw的电压水平典型地是-0.7v,而需要的是半桥电压vsw不下降到-0.7v之低,而是需要其处于较优的-0.5v至-0.3v的电压范围内。

135.具体地,测量电路222利用比较器,例如图4中的比较器402,来将半桥电压sw的电压vsw与多个参考电压相比较,以产生具有多个位的状态信号vsw_rise_status。多个参考电压vt_rise《1》至vt_rise《n》配置为在0v和例如-0.7v的负电压电平之间的电压,其间隔根据粒度需求而配置。在多个实施方式中,图4的测量电路400包括2至8个比较器,每个比较器配置为产生状态信号中的一个比特位。状态信号vsw_rise_status中的位,亦即状态信号vsw_rise_status的值表示半桥电压vsw是否高于或低于相对应的参考电压。例如,参考图4所示,如果测量电路400包括7个比较器,每个比较器在其正输入端上接收对应的参考电压0v、-0.1v、-0.2v、

……

、-0.7v,则具有-0.55v的电压vsw的半桥电压sw将得到状态信号vsw_rise_status为“0011111”,表明该半桥电压vsw高于-0.6v且低于-0.5v。作为另一示例,-0.25v的半桥电压vsw得到“0000111”的状态信号vsw_rise_status。

136.回到图6,在步骤602中,控制器电路执行上电复位(power on reset,por)以将延迟控制信号dt_ctrl初始化为“0”。在步骤604中,初始延迟控制信号被保持,并准备进行可能的后续改变。在步骤606中,确定当前进程是否在当前pwm时钟周期中。如果pwm时钟周期已过,则延迟控制信号被保持为与先前一致。否则,如果当前pwm时钟周期尚未过去,本方法进行步骤608。在步骤608中,控制器电路将状态信号vsw_status的值与下限值进行比较。以上述为例,如果需要半桥电压sw在此后不是从常规的最低电压-0.7v、而是从下限的-0.5v上即被拉升,表示半桥电压vsw为-0.55v的“0011111”的状态信号vsw_rise_status将在本步骤608中被确定为低于下限电压-0.5v,从而该方法进行步骤610。

137.在步骤610中,延迟控制信号ct_ctrl被修改,以使在下一周期中hs 202可以更早地被导通。如图5所示的,延迟控制信号on_delay_ctrl的“0”位的数量决定施加到hs 202的控制端上的控制信号中被引入的延迟。故此,在本实施方式中,步骤610可以实施为减少延迟控制信号dt_ctrl中的位“0”的数量。具体地,当前延迟控制信号dt_ctrl被向左移位一位,延迟控制信号的最右位被置为“1”。通过在延迟控制信号的右侧加入位“1”,该延迟控制信号中的“0”位的数量得以减少,从而引入到用于hs 202的控制信号中的延迟时间亦得以减少。该方法随后进行步骤604以保持经移位的延迟控制信号,并为下一次可能的通过步骤606、608进行的移位做好准备。

138.另一方面,如果步骤608确定状态信号表明半桥电压vsw不低于下限电压,则该方法进行步骤612,控制器电路210将状态信号vsw_status的值与上限电压值相比较。与前述的示例类似地,如果需要半桥电压sw应当在ls 204已经从体二极管导通中合理地恢复、半桥电压sw在不高于-0.3v的合理范围内时被上拉,则状态信号vsw_rise_status为“0000011”表明半桥电压vsw为-0.25v将在本步骤612中确定为高于上限电压-0.3v,本方法将进行步骤614。

139.与步骤610所进行的运作类似地,步骤614将延迟控制信号dt_ctrl修改为使得hs 202在随后的下一周期中被稍晚地导通。如图5所示的,延迟控制信号on_delay_ctrl中的位“0”越多,施加到hs 202的控制端上的控制信号中被引入的延迟时间就越多,该步骤614从

而将当前延迟控制信号向右移位一位,延迟控制信号的最左侧位设为“0”。如此,延迟控制信号被加入了一位“0”,随后通过延迟电路500来向用于hs 202的控制信号中引入更多的延迟时间。该方法随后进行步骤604,将经移位的延迟控制信号保持,并准备下一次可能的由步骤606、608进行的移位。

140.参考图7,在第四阶段702开始的pwm信号的上升沿,由于如标注708所示的施加到ls 204上的控制信号lg从高电平转低,在ls 204中出现反向恢复电流。在测量了负电压704后,施加到hs 202的控制信号hg由延迟控制信号on_delay_ctrl延迟一个时间阶段,如标注710所示。其后,控制信号hg开始在后续的阶段712和706中被上拉。在阶段712期间,控制信号hg被拉向hs 202的导通阈值电压,因此在阶段712中hs 202沿未导通。在控制信号hg达到hs 202的导通阈值电压后的阶段706中,hs 202由经过上拉的高电平控制信号hg导通,产生高电平半桥电压vsw。

141.回到图2,在半桥电压sw的上升阶段,若hs 202被控制为通过将用于hs 202导通的当前延迟时间中减少一个延迟时间而较早地转为导通,其亦可实施为在该半桥电压sw的上升阶段当其被测量为太低而小于下限电压时,在关断ls 204时增加一个延迟时间。类似地,当半桥电压sw被测量为高于上限电压时,若hs 202被控制为通过在使hs 202导通的当前延迟时间中加入一个延迟时间来较晚地转为导通,其亦可实施为在该半桥电压sw上升的阶段在使ls 204关断时减少一个延迟时间。

142.在控制信号hg下降为低电平以关断hs 202时,也可能产生类似的反向恢复电流。类似于如图6所示的方法,第二测量电路224测量半桥电压sw的电压水平vsw中的下降沿,如有需要调整用于导通ls 204的施加到ls 204上的控制信号lg中引入的延迟时间。简言之,在半桥电压sw的下降阶段,如果其被测量为过高而高于第二上限电压,ls 204将被控制为通过从当前延迟时间中减少一个延迟时间而被导通,从而ls204被较早地导通以将半桥电压下拉。此外,hs 202可以被控制为,响应于半桥电压vsw被测量为在其下降阶段高于第二上限电压,通过向当前关断延迟时间中加入一个延迟时间而关断。另一方面,在半桥电压vsw的该下降阶段,如果其被测量为低于第二下限电压,ls 204可被控制为通过向当前ls导通延迟时间中加入一个延迟时间而被导通得更晚,及/或hs 202可以被控制为通过从当前hs关断延迟时间中减少一个延迟时间而被关断得更早。

143.在一个或多个实施方式中,半桥电压sw的测量还可以用来调整用于hs 202或ls 204的控制信号hg、lg被上拉以用来使开关导通的时间。参考图7,在阶段712中,控制信号hg的斜率反映控制信号hg在达到hs 202的导通阈值电压之前被拉升的速度。该阶段712始自延迟时间结束、控制信号开始上升,直至控制信号hg达到对应的hs 202的阈值电压。控制信号hg或lg被上拉的速度还称为控制信号hg/lg的导通转换速率。控制信号的斜率越大,控制信号的转换速率越高。

144.参考图8,其示出了输入pwm信号和施加到开关上的控制信号hg或lg的信号波形。在延迟时间802期间,输入pwm信号已经为高电平,而控制信号hg或lg仍处在被上拉前的延迟阶段。在延迟时间802结束时,控制信号hg或lg被上拉而增大,该增大的速率是可调整的,如标注804所示的。在该控制信号hg或lg的可调整的增长阶段末尾,达到开关的阈值电压,控制信号hg或lg被强上拉至导通电压水平806,从而将hs 202或ls 204导通。如所知的,控制信号hg或lg在达到开关的阈值电平后方才导通hs 202或ls 204,因而控制信号的转换速

率亦影响了开关导通前的空置时间。由图8所示可见,较慢的控制信号hg/lg上拉速度会使上部开关hs和下部开关ls均关断的空置时间延长。然而,考虑到控制信号的太慢增大可能对开关hs/ls对于控制信号的响应带来挑战,实施方式中控制信号的转换速率是可配置的,并保持开关响应的可靠。

145.回到图2和图3,控制信号转换速率也可以基于来自测量电路222或224的状态信号而调节。第一控制器226和第二控制器228基于状态信号而产生转换速率控制信号。图9所示的是上部驱动器216和上部开关hs 202的一种示例的实施方式的电路图。上部驱动器216使用来自控制器电路210的转换速率控制信号来调节施加到hs 202的栅极端上的栅极控制信号的电压。上部驱动器216包括连接在充分上拉电压和hs202的控制端之间的第一开关902、以及连接在hs 202的控制端和地之间的第二开关904。第一开关902能够可控地导通,以将施加到hs 202上的控制信号hg快速地拉升到充分上拉电压而使hs 202充分导通。第二开关904能够可控地导通,以将施加到hs 202上的控制信号hg快速地拉到地电平而关断hs 202。

146.图9的上部驱动器216包括多个调节开关906。调节开关906中的每一个接收转换速率控制信号中的一位,例如如上所述的由第一控制器226所产生的。调节开关906在响应于转换速率控制信号中的对应控制位而变为导通时,向提供到hs 202的控制信号hg中加入一个值,随后加快控制信号hg的增大速度,直至hs 202的阈值电压。

147.回到图6所示的,转换速率控制信号可以由第一控制器226以类似于延迟时间控制信号dt_ctrl被产生的方式而产生,在此不再详述。大体而言,如果状态信号显示半桥电压sw的电压vsw低于下限电压,如在步骤608中所确定的,应需要将控制信号hg更快地拉升。据此,图6的步骤610将转换速率控制信号sr_ctrl向左移位一位,并在转换速率控制信号sr_ctrl的最右一位加入位“1”。参照图9,步骤610从而向栅极控制信号hg中加入一个值,以能够将控制信号hg更快地上拉。图6的步骤614则将转换速率控制信号sr_ctrl向右移位一位,并把转换速率控制信号sr_ctrl的最左一位设为“0”,以在栅极控制信号hg中减小一个值,来降低控制信号hg被上拉的速度。用于下部开关204的下部驱动器可以实施为与图9所示的类似的结构。

148.回到参考图3所示,第二测量电路224测量半桥电压sw的电压vsw中的下降沿,并产生能够表征所测量的半桥电压的状态信号vsw_fall_status。与参考第一控制器226和上部开关202所描述的类似地,下降沿状态信号vsw_fall_status被第二控制器228用来向关断hs 202和ls 204的控制信号hg和lg中引入延迟,以消减由于hs 202中的反向恢复电流而导致的半桥电压sw中的过高电压。图10a和图10b显示的是半桥电压的信号波形。图10a示出的是控制开关的控制信号中没有经调节的延迟时的半桥电压,其中在通过导通上部开关而将半桥电压上拉之前出现低于低电压水平的负电压,且半桥电压在被上拉后以衰减方式在高电压水平上振荡。图10b示出的是可以通过测量半桥电压来检测开关中的体二极管导通、并据以设定和调节用于开关的控制信号的延迟时间的半桥电压。在图10b中,在低电压水平之下的负电压极大地得到抑制,并且半桥电压在被上拉后亦得以稳定。

149.图11示出根据另一实施方式的半桥功率系统的示意图。该半桥功率系统1100与图3中的实施方式类似。半桥功率系统1100包括测量电路1102和控制器1104。测量电路1102测量半桥电压中的上升沿,并产生表征该测量的状态信号vsw_rise_status。控制器1104接收状态信号,并产生延迟控制信号,可选地产生转换速率控制信号。控制器1104将延迟控制信

号提供给上部导通on延迟电路1106,上部导通on延迟电路1106还接收输入pwm信号。上部导通on延迟电路1106使用来自控制器1104的延迟控制信号来向pwm信号中施加延迟,并且类似于图3中的实施方式地,将上部导通信号hs_on提供给上部触发器电路1108,用以产生上部控制信号来控制上部开关。上部触发器电路1108在其复位端(r端)接收经上部缓冲器电路1112缓冲的、由上部反相器1110翻转的,作为上部关断off信号hs_off的缓冲翻转pwm信号。据此,当pwm信号为低电平时,上部开关关断。

150.在图11的下部部分,下部触发器电路1114在置位端(s端)接收下部导通on信号ls_on,下部导通on信号ls_on是由反相器1110转换的、由下部导通延迟电路1116施加了固定导通on延迟的pwm信号。据此,在pwm信号转为低电平后,下部开关导通。下部触发器电路1110还在其复位端(r端)接收下部关断off信号ls_off,下部关断off信号ls_off可以由下部关断off延迟电路1118基于来自控制器1104的根据了状态信号的延迟时间控制信号来设置/调节。下部关断off信号ls_off为高态时,将下部触发器电路1110的输出信号复位,据以将下部开关关断。控制器1104可以运行于类似于图6的实施方式的流程中,以产生延迟控制信号来调节各开关导通/关断前的延迟时间。

151.图12示出了半桥功率系统的另一实施方式。该半桥功率系统1200包括测量电路1202,测量电路1202用于测量半桥电压sw中的下降沿,以及产生能够表征该测量的状态信号vsw_fall_status。半桥功率系统1200的控制器1204使用状态信号vsw_fall_status来调节下部开关导通前的延迟时间、以及上部开关关断前的延迟时间,其类似于参考图11所述的。

152.所描述的控制器和半桥功率系统测量半桥电压中的上升/下降沿,以确定开关中的体导通状态,并利用该测量来调节开始导通/关断各开关的时间。此外,该测量和所产生的多位状态信号还可以用来调节开关被控制导通的控制信号的转换速率。该半桥功率电路具有可调节/可设置的开关控制延迟时间,因而更具效率,并因减小了反向恢复损失而变得高效。由于半桥功率电路中的开关受因于制程、电压、和温度(pvt)的变化,关于开关的行为的测量和检测、以及其后使用该检测的调节,增强了半桥功率电路应对pvt变化的稳健程度。

153.在此参考了特定的所示的例子对于各种示例的实施方式进行了描述。所述示例的例子被选择为辅助本领域的技术人员来形成对于各实施方式的清晰理解并得实施。然而,可以构建为包括一个或多个实施方式的系统、结构和器件的范围,以及根据一个或多个实施方式实施的方法的范围,并不为所展示的示例性例子所限制。相反地,所属技术领域的技术人员基于本说明书可以理解:可以根据各实施方式来实施出很多其他的配置、结构和方法。

154.应当理解的是,就于本发明在前描述中所使用的各种位置指示来说,例如顶、底、上、下,彼等指示仅是参考了相应的附图而给出,并且当器件的朝向在制造或工作中发生变化时,可以代替地具有其他位置关系。如上所述,那些位置关系只是为清楚起见而描述,并非限制。

155.本说明的前述描述是参考特定的实施方式和特定的附图,但本发明不应当限制于此,而应当由权利要求书所给出。所描述的各附图都是示例性的而非限制性的。在附图中,为示例的目的,各元件的尺寸可能被放大,且可能没有绘制为特定的比例尺。本说明也应当

包括各元件、工作方式在容限和属性上的不连续的变换。还应当包括本发明的各种弱化实施。

156.本说明及权利要求书中所使用的词汇“包括”并不排除其他元件或步骤。除非特别指出,在使用单数形式如“一”、“一个”指代确定或不确定的元件时,应当包括该元件的复数。从而,词汇“包括”不应当被理解为限于在其后所列出的条目,不应当理解为不包括其他元件或步骤;描述“器件包括项目a和b”的范围不应当限制为只包括元件a和b的器件。该描述表示,就于本说明而言,只有器件的元件a和b是相关的。尽管耦合通常包括电感性的连接、连接通常意为通过例如电线的连接,然而此处所述“连接”、“耦接”、“耦合”均表示在相耦接或相连接的元件之间存在电学的联系,且不意味着其间没有中间元件。在描述晶体管及其连接时,词语栅、漏、和源与栅极、漏极、源极以及栅极端、漏极端、源极端是可互换的。

157.对于所属领域的技术人员而言,在不背离本发明的权利要求的范畴内可以作出多种具体变化。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1