半导体结构及其形成方法与流程

本发明涉及半导体制造领域,尤其涉及一种半导体结构及其形成方法。

背景技术:

1、在目前的半导体产业中,集成电路产品主要可分为三大类型:逻辑、存储器和模拟电路,其中存储器件在集成电路产品中占了相当大的比例。

2、随着存储技术的发展,出现了各种类型的半导体存储器,例如静态随机随机存储器(sram,static random access memory)、动态随机存储器(dram,dynamic randomaccess memory)、可擦除可编程只读存储器(eprom,erasable programmable read-onlymemory)、闪存(flash)等等。

3、然而,现有技术中的eprom存储器的集成度和性能仍然有待改善。

技术实现思路

1、本发明解决的技术问题是提供一种半导体结构的形成方法和半导体结构,以改善半导体结构的集成度和性能。

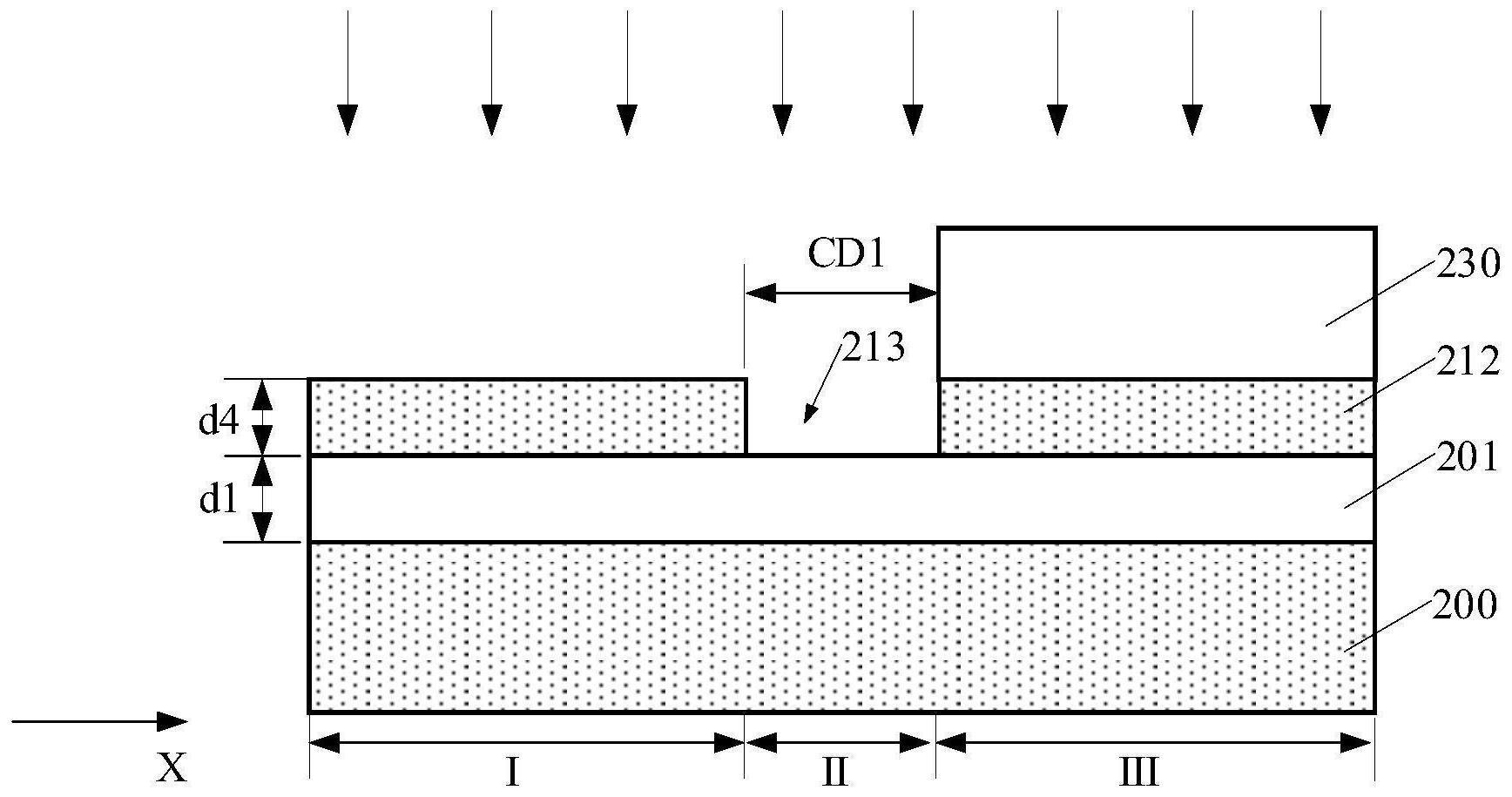

2、为解决上述技术问题,本发明的技术方案提供一种半导体结构,包括:衬底,所述衬底包括相邻且沿第一方向排布的第一区、第二区和第三区,所述第一区和第三区表面具有第一氧化层,所述第一氧化层内具有隧穿层开口,所述隧穿层开口底部暴露出第二区表面,在所述第一方向上,所述隧穿层开口的宽度在预设宽度以下;位于所述隧穿层开口内的隧穿层,并且,所述隧穿层的厚度小于所述隧穿层开口的深度。

3、可选的,所述预设宽度为0.2微米。

4、可选的,所述第一氧化层为高压氧化层,所述隧穿层为低压氧化层。

5、可选的,在所述第一方向上,所述第一区和第二区的总宽度大于0.4微米,所述第二区和第三区的总宽度大于0.4微米。

6、可选的,所述第一氧化层的厚度在200埃以下,所述隧穿层的厚度在80埃以下。

7、可选的,所述衬底还包括沿第二方向交替排布的若干有源区和若干隔离区,所述第二方向垂直于所述第一方向,在所述第二方向上,所述第一区、第二区和第三区均贯穿若干有源区和若干隔离区,所述第一氧化层还位于所述有源区的表面,所述隔离区内和隔离区上具有隔离结构,且所述隔离结构表面高于所述第一氧化层表面。

8、可选的,还包括:位于连接的第一氧化层和隧穿层表面的浮栅极,所述浮栅极沿第二方向横跨若干有源区和若干隔离区;位于所述浮栅极表面的控制栅。

9、相应的,本发明的技术方案还提供一种半导体结构的形成方法,包括:提供衬底,所述衬底包括相邻且沿第一方向排布的第一区、第二区和第三区,所述第一区、第二区和第三区表面具有第一氧化层;在所述第一氧化层表面形成掩膜材料层;对所述掩膜材料层进行第一次图形化步骤,在垂直于衬底表面的方向上,减薄第二区和第三区的掩膜材料层的厚度,形成初始掩膜层;对所述初始掩膜层进行第二次图形化步骤,形成掩膜层,所述掩膜层内具有掩膜开口,所述掩膜开口底部暴露出第二区上的第一氧化层表面;以所述掩膜层为掩膜刻蚀所述第一氧化层,在所述第一氧化层内形成隧穿层开口,所述隧穿层开口底部暴露出所述第二区表面;在所述隧穿层开口内形成隧穿层,并且,所述隧穿层的厚度小于所述隧穿层开口的深度。

10、可选的,对所述掩膜材料层进行第一次图形化步骤的方法包括:在所述第一区上形成第一光刻层,所述第一光刻层暴露出所述第二区和第三区上的掩膜材料层;以所述第一光刻层为掩膜刻蚀所述掩膜材料层,以对所述第二区和第三区的掩膜材料层进行减薄。

11、可选的,以所述第一光刻层为掩膜刻蚀所述掩膜材料层的工艺包括各向异性的干法刻蚀工艺。

12、可选的,还包括:在形成初始掩膜层之后,去除所述第一光刻层。

13、可选的,对所述初始掩膜层进行第二次图形化步骤的方法包括:在去除所述第一光刻层之后,在所述第三区上形成第二光刻层,所述第二光刻层暴露出第一区和第二区上的初始掩膜层;以所述第二光刻层为掩膜刻蚀所述初始掩膜层,直至暴露出第二区的第一氧化层表面,形成所述掩膜层。

14、可选的,以所述第二光刻层为掩膜刻蚀所述初始掩膜层的工艺包括各向异性的干法刻蚀工艺,或者,干法刻蚀工艺和湿法刻蚀工艺。

15、可选的,以所述掩膜层为掩膜,刻蚀所述第一氧化层的工艺包括湿法刻蚀工艺。

16、可选的,以所述掩膜层为掩膜刻蚀所述第一氧化层的所述湿法刻蚀工艺中,对所述第一氧化层和所述掩膜层的材料的刻蚀选择比在5:1以上。

17、可选的,所述掩膜层的材料包括介电材料,并且,所述掩膜层的材料与第一氧化层的材料不同。

18、可选的,所述第一氧化层的材料包括氧化硅,所述掩膜层的材料包括氮氧化硅。

19、可选的,所述隧穿层的材料包括氧化硅。

20、可选的,所述掩膜材料层的厚度在600埃以下,所述掩膜开口的深度范围是200埃~300埃。

21、可选的,在所述第一方向上,所述隧穿层开口的宽度在0.2微米以下。

22、可选的,在所述第一方向上,所述第一区和第二区的总宽度大于0.4微米,所述第二区和第三区的总宽度大于0.4微米。

23、可选的,所述衬底还包括沿第二方向交替排布的若干有源区和若干隔离区,所述第二方向垂直于所述第一方向,在所述第二方向上,所述第一区、第二区和第三区均贯穿若干有源区和若干隔离区,所述第一氧化层还位于所述有源区的表面,所述隔离区内和隔离区上具有隔离结构,并且,所述隔离结构表面高于所述第一氧化层表面,所述掩膜材料层还位于所述隔离结构表面。

24、可选的,还包括:形成所述隧穿层之后,在连接的第一氧化层和隧穿层表面形成浮栅极,所述浮栅极沿第二方向横跨若干所述有源区和若干所述隔离区;在所述浮栅极上形成控制栅。

25、与现有技术相比,本发明实施例的技术方案具有以下有益效果:

26、本发明的技术方案提供的半导体结构的形成方法中,对所述掩膜材料层进行第一次图形化步骤,以减薄第二区和第三区的掩膜材料层的厚度形成初始掩膜层,并且,对所述初始掩膜层进行第二次图形化步骤,形成具有掩膜开口的掩膜层。分别以两次图形化步骤传递掩膜开口的图形,能够在形成关键尺寸更小的掩膜开口的同时,使每次图形化步骤中形成的光刻层的关键尺寸远大于光刻工艺的极限尺寸,从而,使光刻层的形貌更好,进而,使掩膜开口的图形形貌更好。由此,根据掩膜开口的图形向第一氧化层传递图形而形成的隧穿层开口,兼顾了较小的关键尺寸和较好的形貌,能够形成的小尺寸、形貌好的隧穿层,从而,提高了半导体结构的集成度和性能。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.如权利要求1所述的半导体结构,其特征在于,所述预设宽度为0.2微米。

3.如权利要求1所述的半导体结构,其特征在于,所述第一氧化层为高压氧化层,所述隧穿层为低压氧化层。

4.如权利要求1所述的半导体结构,其特征在于,在所述第一方向上,所述第一区和第二区的总宽度大于0.4微米,所述第二区和第三区的总宽度大于0.4微米。

5.如权利要求1所述的半导体结构,其特征在于,所述第一氧化层的厚度在200埃以下,所述隧穿层的厚度在80埃以下。

6.如权利要求1所述的半导体结构,其特征在于,所述衬底还包括沿第二方向交替排布的若干有源区和若干隔离区,所述第二方向垂直于所述第一方向,在所述第二方向上,所述第一区、第二区和第三区均贯穿若干有源区和若干隔离区,所述第一氧化层还位于所述有源区的表面,所述隔离区内和隔离区上具有隔离结构,且所述隔离结构表面高于所述第一氧化层表面。

7.如权利要求6所述的半导体结构,其特征在于,还包括:位于连接的第一氧化层和隧穿层表面的浮栅极,所述浮栅极沿第二方向横跨若干有源区和若干隔离区;位于所述浮栅极表面的控制栅。

8.一种半导体结构的形成方法,其特征在于,包括:

9.如权利要求8所述的半导体结构的形成方法,其特征在于,对所述掩膜材料层进行第一次图形化步骤的方法包括:在所述第一区上形成第一光刻层,所述第一光刻层暴露出所述第二区和第三区上的掩膜材料层;以所述第一光刻层为掩膜刻蚀所述掩膜材料层,以对所述第二区和第三区的掩膜材料层进行减薄。

10.如权利要求9所述的半导体结构的形成方法,其特征在于,以所述第一光刻层为掩膜刻蚀所述掩膜材料层的工艺包括各向异性的干法刻蚀工艺。

11.如权利要求9所述的半导体结构的形成方法,其特征在于,还包括:在形成初始掩膜层之后,去除所述第一光刻层。

12.如权利要求11所述的半导体结构的形成方法,其特征在于,对所述初始掩膜层进行第二次图形化步骤的方法包括:在去除所述第一光刻层之后,在所述第三区上形成第二光刻层,所述第二光刻层暴露出第一区和第二区上的初始掩膜层;以所述第二光刻层为掩膜刻蚀所述初始掩膜层,直至暴露出第二区的第一氧化层表面,形成所述掩膜层。

13.如权利要求12所述的半导体结构的形成方法,其特征在于,以所述第二光刻层为掩膜刻蚀所述初始掩膜层的工艺包括各向异性的干法刻蚀工艺。

14.如权利要求8所述的半导体结构的形成方法,其特征在于,以所述掩膜层为掩膜,刻蚀所述第一氧化层的工艺包括湿法刻蚀工艺,或者,干法刻蚀工艺和湿法刻蚀工艺。

15.如权利要求14所述的半导体结构的形成方法,其特征在于,以所述掩膜层为掩膜刻蚀所述第一氧化层的所述湿法刻蚀工艺中,对所述第一氧化层和所述掩膜层的材料的刻蚀选择比在5:1以上。

16.如权利要求8所述的半导体结构的形成方法,其特征在于,所述掩膜层的材料包括介电材料,并且,所述掩膜层的材料与第一氧化层的材料不同。

17.如权利要求16所述的半导体结构的形成方法,其特征在于,所述第一氧化层的材料包括氧化硅,所述掩膜层的材料包括氮氧化硅。

18.如权利要求8所述的半导体结构的形成方法,其特征在于,所述隧穿层的材料包括氧化硅。

19.如权利要求8所述的半导体结构的形成方法,其特征在于,所述掩膜材料层的厚度在600埃以下,所述掩膜开口的深度范围是200埃~300埃。

20.如权利要求8所述的半导体结构的形成方法,其特征在于,在所述第一方向上,所述隧穿层开口的宽度在0.2微米以下。

21.如权利要求8所述的半导体结构的形成方法,其特征在于,在所述第一方向上,所述第一区和第二区的总宽度大于0.4微米,所述第二区和第三区的总宽度大于0.4微米。

22.如权利要求8所述的半导体结构的形成方法,其特征在于,所述衬底还包括沿第二方向交替排布的若干有源区和若干隔离区,所述第二方向垂直于所述第一方向,在所述第二方向上,所述第一区、第二区和第三区均贯穿若干有源区和若干隔离区,所述第一氧化层还位于所述有源区的表面,所述隔离区内和隔离区上具有隔离结构,并且,所述隔离结构表面高于所述第一氧化层表面,所述掩膜材料层还位于所述隔离结构表面。

23.如权利要求22所述的半导体结构的形成方法,其特征在于,还包括:形成所述隧穿层之后,在连接的第一氧化层和隧穿层表面形成浮栅极,所述浮栅极沿第二方向横跨若干所述有源区和若干所述隔离区;在所述浮栅极上形成控制栅。

技术总结

一种半导体结构及其形成方法,其中,方法包括:提供衬底,所述衬底包括第一区、第二区和第三区,所述第一区、第二区和第三区表面具有第一氧化层;在所述第一氧化层表面形成掩膜材料层;对所述掩膜材料层进行第一次图形化步骤,减薄第二区和第三区的掩膜材料层的厚度,形成初始掩膜层;对所述初始掩膜层进行第二次图形化步骤,形成掩膜层,所述掩膜层内具有掩膜开口;以所述掩膜层为掩膜刻蚀所述第一氧化层,形成隧穿层开口;在所述隧穿层开口内形成隧穿层,并且,所述隧穿层的厚度小于所述隧穿层开口的深度。所述形成方法能够提高所形成的半导体结构的集成度和性能。

技术研发人员:钟怡,董天化

受保护的技术使用者:中芯国际集成电路制造(上海)有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!