一种对管电路的制作方法

1.本发明涉及一种集成电路,尤其涉及一种在同一个基底上的对管电路。

背景技术:

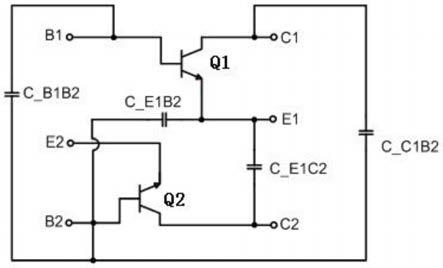

2.对管电路就是将两个一模一样的晶体管制作在同一个基底上,两个晶体管的温度会相互影响,环境温度对晶体管也产生同样的影响。理论上,两个晶体管的噪声系数、特性曲线、放大倍数等都要求一致,这样在差分电路的应用中,可以在相当程度上抵消掉共模信号对差模信号的影响,抵消温度影响造成的零点漂移。除了差分电路,常见的压控振荡器(vco)电路结构也是由一个振荡管和一个放大管组成,因此也可以用对管电路搭建vco。

3.传统的对管电路在设计时,两个晶体管之间没有电气隔离,相互之间的端口间的寄生参数很多,影响电路的高频性能,如图1中极间的寄生电容:c_b1b2、c_e1b2、c_e1c2、c_c1b2。

技术实现要素:

4.鉴于现有技术的不足,本发明提出了一种高性能的对管电路,两个晶体管之间由端口到地(gnd)的隔离单元进行电气隔离,减少相互之间的串扰,并且gnd单元提供了到地的散热途径。为了减小晶体管的密勒电容,在进行版图设计时,加宽了晶体管基极和发射极的金属宽度。并且为了提高电路的抗驻波能力,晶体管的每个端口都有到地的双向(正向、反向)esd(electro static discharge)保护单元。

5.本发明的技术方案是:

6.基于同一个基底上由两组晶体管t1、t2组成,每组晶体管由数目相同工艺一致的多只晶体管并联构成;

7.两组晶体管t1、t2之间无电气连接,两组晶体管t1、t2之间有到地gnd1、gnd2的隔离单元进行去耦隔离,隔离单元由损耗结构构成,如隔离单元为电阻。

8.两组晶体管t1、t2的每个端口b1、e1、c1、b2、e2、c2都有单独的到地的双向esd保护单元,双向esd保护单元为二极管串。

9.gnd单元提供了到热沉的散热途径;绘制版图时,均匀分布多个gnd单元。

10.在版图设计时,加宽基极(b1、b2)和发射极(e1、e2)金属连线,靠近晶体管管脚时使用渐变传输线。

11.整体电路在绘制版图时,完全对称,可以180度旋转,隔离单元位置不变,晶体管位置重合。

12.两组晶体管t1、t2用hbt的半导体制程工艺,或用bjt的半导体制程工艺,用fet的半导体制程工艺。

13.本发明的有益效果:

14.提出了一种高性能、高隔离度的对管电路,对管之间无电气连接,并且有隔离单元隔离,提高对称性,减少串扰和寄生参数,改善高频性能;并且改善了散热环境,适用于大功

率应用。

附图说明

15.图1是传统的对管电路。

16.图2是本发明的结构图之一。

17.图3是本发明的结构图之二。

18.图4是本发明结构图之二的电路图。

具体实施方式

19.以下结合附图进一步说明本发明电路:

20.在同一个基底上,设置两组晶体管t1和t2,每组晶体管可以根据成本、输出功率、工作频率等要求,选用相应的半导体制程工艺。如为节约成本选用si基bjt半导体制程工艺,为提高输出功率选用gan hemt半导体制程工艺,为提高工作频率选用gaas hbt半导体制程工艺。

21.每组均由多只晶体管并联构成,一般可以是1~4只晶体管,两组晶体管的并联晶体管数目一致,工艺一致。晶体管t1和晶体管t2之间无电气连接,由一个端口到地的隔离单元进行去耦隔离,隔离单元分布在晶体管t1、t2之间的位置,如图2中隔离单元45度斜跨在gnd1和gnd2之间,有效减少晶体管t1和晶体管t2之间的串扰,提高电路整体工作频率。该隔离单元一般由损耗结构构成,例如是电阻。

22.晶体管t1和晶体管t2的各个端口,即发射极e1、e2,集电极c1、c2,基极b1、b2,都有单独的到地的双向esd保护单元,可以提高电路的抗烧毁能力。esd保护单元一般由二极管串构成。二极管的数量可以根据需要保护静电电压的大小来设置。

23.gnd单元提供了到热沉(thermalshunt)的散热途径,有利于电路应用于大功率场景。绘制版图时可根据具体的散热需求,均匀分布各个gnd单元,以及调整gnd数量。

24.晶体管t1和晶体管t2在版图设计时,通过加宽基极b1、b2和发射极e1、e2金属连线,靠近晶体管管脚处使用渐变传输线、改变管脚传输线的特征阻抗,有效减小密勒电容,改善电路频率特性。

25.整体电路在绘制版图时,以基底中心点180度旋转,晶体管t1、t2位置对称,可以,更有利于两组晶体管t1、t2电气性能完全对称的实现,使得电路更适用于差分电路结构。

26.如图3所示,用作差分电路结构时,可以将两组晶体管t1、t2的发射极e1和e2通过gnd单元进行电气连接,进一步提高电路的对称性。图中晶体管t1和晶体管t2的发射极e1和e2通过gnd3和gnd4进行了电气连接,也可以通过gnd2和gnd1进行电气连接,保证电路布图时尽量对称即可,以保障晶体管的对称性。

27.所有gnd单元在芯片封装后仅代表一个引脚功能,在进行后续基于pcb的系统方案设计时,可以不跟系统地相连。

技术特征:

1.一种对管电路,其特征在于同一个基底上由两组晶体管(t1、t2)组成,每组晶体管由数目相同工艺一致的多只晶体管并联构成;两组晶体管(t1、t2)之间无电气连接,两组晶体管(t1、t2)之间有到地(gnd1、gnd2)的隔离单元进行去耦隔离,隔离单元由损耗结构构成;两组晶体管(t1、t2)的每个端口(b1、e1、c1、b2、e2、c2)都有单独的到地的双向esd保护单元。2.根据权利要求1所述的一种对管电路,其特征在于:两组晶体管(t1、t2)的发射极(e1和e2)通过gnd单元进行电气连接。3.根据权力要求1~2之一所述的一种对管电路,其特征在于:每一组晶体管(t1或t2)的数量是1~4只。4.根据权利要求3所述的一种对管电路,其特征在于:gnd单元提供了到热沉的散热途径;绘制版图时,均匀分布多个gnd单元。5.根据权利要求4所述的一种对管电路,其特征在于:隔离单元为电阻。6.根据权利要求5所述的一种对管电路,其特征在于:esd保护单元为二极管串。7.根据权利要求6所述的一种对管电路,其特征在于:在版图设计时,加宽基极(b1、b2)和发射极(e1、e2)金属连线,靠近晶体管管脚时使用渐变传输线。8.根据权利要求7所述的一种对管电路,其特征在于:整体电路在绘制版图时,以中心点180度旋转,两组晶体管(t1、t2)的物理位置对称。9.根据权利要求6所述的一种对管电路,其特征在于:两组晶体管(t1、t2)用hbt的半导体制程工艺,或用bjt的半导体制程工艺,或用fet的半导体制程工艺。

技术总结

本发明公开了一种对管电路,其包括:于同一个基底上由两组晶体管组成,每组晶体管由数目相同工艺一致的多只晶体管并联构成。两组晶体管之间无电气连接,两组晶体管之间的隔离单元由损耗结构构成。两组晶体管的每个端口都有单独的到地的双向ESD保护单元,ESD保护单元一般由二极管串构成。GND单元提供了到热沉的散热途径;绘制版图时,均匀分布多个GND单元。在版图设计时,加宽基极和发射极金属连线,靠近晶体管管脚时使用渐变传输线。整体电路在绘制版图时,完全对称,可以180度旋转。本发明有效地提高了电路的高频差分性能。地提高了电路的高频差分性能。地提高了电路的高频差分性能。

技术研发人员:高怀 田婷

受保护的技术使用者:厦门英诺迅科技有限公司

技术研发日:2022.01.08

技术公布日:2022/4/12

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1