延迟锁相环、延迟锁相环控制方法及电子设备与流程

本公开涉及集成电路,具体而言,涉及一种延迟锁相环、延迟锁相环控制方法及电子设备。

背景技术:

1、延迟锁相环(delay-locked loop,dll)是对时钟信号进行延迟调整,以实现系统中时钟信号同步的电路。由于该同步不随外界条件,如温度、电压等的变化而改变,因此,被广泛地应用在时序领域。

2、然而,现有的延迟锁相环,为了保证cpu(central processing unit,中央处理器)读取数据的精确性,无论是在工作状态,还是在待机状态,均处于高频状态,导致延迟锁相环功耗较高。

3、需要说明的是,在上述背景技术部分公开的信息仅用于加强对本公开的背景的理解,因此可以包括不构成对本领域普通技术人员已知的现有技术的信息。

技术实现思路

1、本公开的目的在于提供一种延迟锁相环、延迟锁相环控制方法及电子设备,以降低延迟锁相环的功耗。

2、本公开的其他特性和优点将通过下面的详细描述变得显然,或部分地通过本发明的实践而习得。

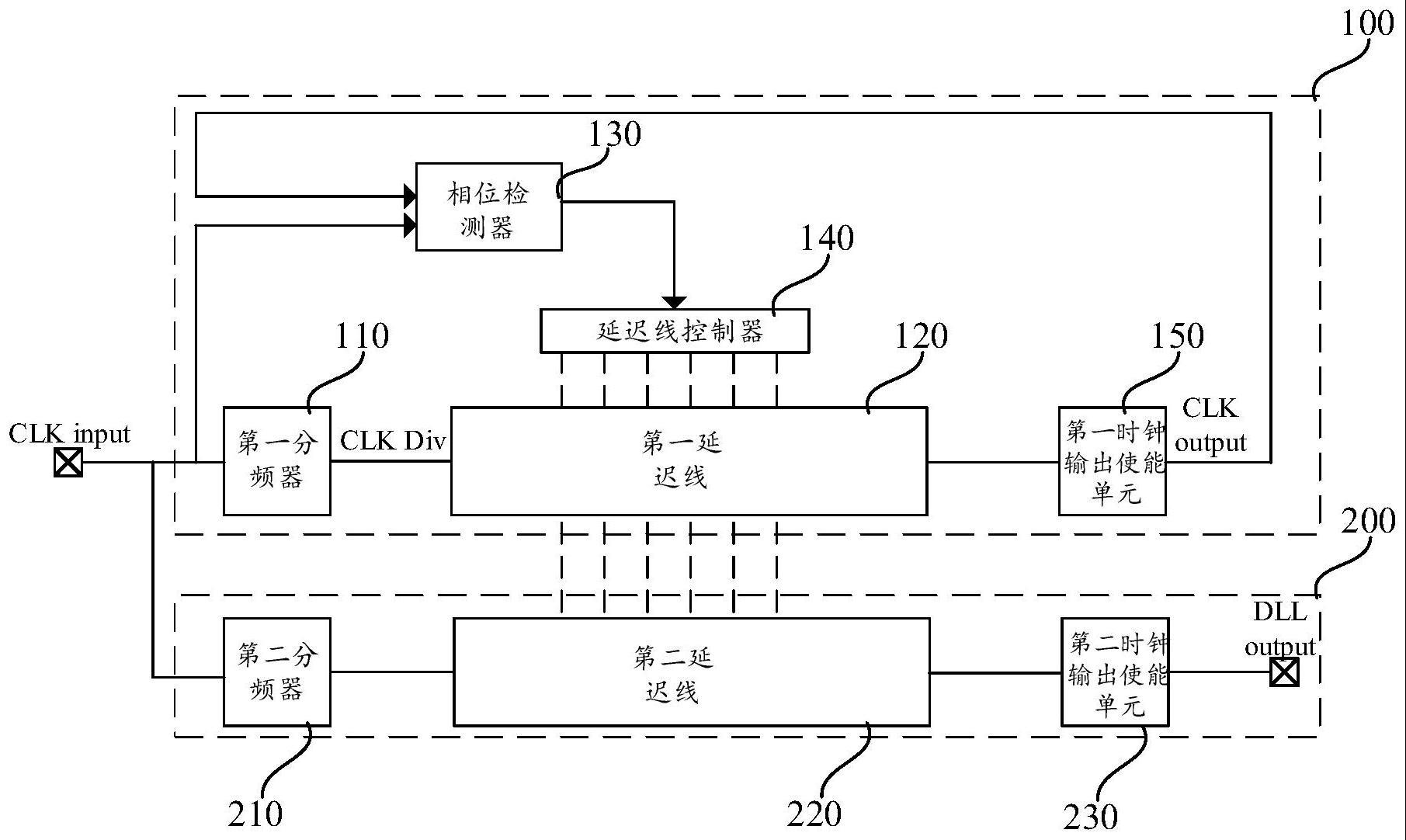

3、根据本公开的第一方面,提供一种延迟锁相环,包括:副通路,用于将输入时钟信号进行分频产生分频时钟信号,在所述延迟锁相环锁定过程中,对具有第一频率的所述分频时钟信号进行调整获得输出时钟信号;在所述延迟锁相环锁定处于待机状态的情况下,调整所述分频时钟信号具有第二频率;其中,所述第二频率低于所述第一频率;主通路,用于在获取到目标指令的情况下,输出与所述输出时钟信号相位相同的输出时钟复制信号。

4、在本公开的一种示例性实施方式中,所述副通路包括:第一分频器,用于将输入时钟信号进行分频产生所述分频时钟信号;第一延迟线,用于对所述分频时钟信号进行延迟调整,以获得具有目标相位的所述输出时钟信号;相位检测器,用于获取所述输出时钟信号,并将所述输出时钟信号与所述输入时钟信号进行比较,确定出所述输出时钟信号与所述输入时钟信号的相位差,根据所述相位差产生控制信号,并将所述控制信号发送给延迟线控制器;所述延迟线控制器,用于基于所述控制信号输出对应的调整信号,以调整所述第一延迟线的延迟参数。

5、在本公开的一种示例性实施方式中,所述主通路包括:第二分频器,与所述第一分频器具有相同的固有延迟;第二延迟线,跟随所述第一延迟线对所述分频时钟信号进行延迟调整,以获得所述输出时钟复制信号。

6、在本公开的一种示例性实施方式中,所述副通路还包括第一时钟输出使能单元,所述输出时钟信号通过所述第一时钟输出使能单元传输至所述相位检测器;所述主通路还包括第二时钟输出使能单元,所述第二时钟输出使能单元在接收到所述目标指令的情况下,控制延迟锁相环的输出端输出所述输出时钟复制信号。

7、在本公开的一种示例性实施方式中,所述第一时钟输出使能单元的固有延迟与所述第二时钟输出使能单元的固有延迟相同。

8、在本公开的一种示例性实施方式中,所述第一分频器用于,在所述第一延迟线锁定后,将所述分频时钟信号的频率从所述第一频率降低为所述第二频率。

9、在本公开的一种示例性实施方式中,所述第一分频器包括:分频单元,用于对所述输入时钟信号进行分频处理;延迟单元,用于补偿所述分频单元的延迟;第一多路选择器,输入端用于接入所述分频单元的输出端和所述延迟单元的输出端,控制端用于接入逻辑与门的输出端;所述逻辑与门的输入端接入延迟锁相环锁定信号和第一测试信号,用于在所述延迟锁相环锁定信号和所述第一测试信号同时使能的情况下,控制所述第一多路选择器输出所述延迟单元的输出信号,在所述第一测试信号未使能的情况下,控制所述第一多路选择器输出所述分频单元的输出信号。

10、在本公开的一种示例性实施方式中,所述分频单元包括多个依次串接的触发器,和多个第二多路选择器;前一级所述触发器的输出端连接后一级所述触发器的输入端;多个所述第二多路选择器用于将每一级所述触发器的输出端分别引向第一级所述触发器的输入端,以实现对所述输入时钟信号的分频。

11、在本公开的一种示例性实施方式中,所述触发器有四个,所述第二多路选择器有三个;其中两个所述第二多路选择器的四个输入端分别接入四个所述触发器的输出端,所述其中两个所述第二多路选择器的输出端接入第三个所述第二多路选择器的输入端;第三个所述第二多路选择器的输出端接入第一级所述触发器的输入端;三个所述第二多路选择器的控制端分别接入三个第二测试信号,用于在三个不同的所述第二测试信号的组合下,控制所述输入时钟信号产生不同的所述分频时钟信号。

12、在本公开的一种示例性实施方式中,所述延迟单元包括多个串接的反相器。

13、在本公开的一种示例性实施方式中,在所述反相器和所述触发器的延迟相同的情况下,所述反相器的个数与所述触发器的个数相同。

14、在本公开的一种示例性实施方式中,所述第一分频器还包括驱动器,所述驱动器的输入端与所述第一多路选择器的输出端相连,所述驱动器的输出端输出所述分频时钟信号。

15、在本公开的一种示例性实施方式中,所述第二分频器与所述第一分频器具有相同的结构。

16、根据本公开的第二方面,提供一种延迟锁相环控制方法,所述延迟锁相环包括主通路和副通路;所述控制方法包括:将输入时钟信号进行分频产生分频时钟信号;在所述延迟锁相环锁定过程中,通过所述副通路对具有第一频率的所述分频时钟信号进行调整获得输出时钟信号;在所述延迟锁相环锁定处于待机状态的情况下,调整所述分频时钟信号具有第二频率;其中,所述第二频率低于所述第一频率;在获取到目标指令的情况下,控制所述主通路输出与所述输出时钟信号相位相同的输出时钟复制信号。

17、根据本公开的第三方面,提供一种电子设备,包括:上述的延迟锁相环。

18、本公开提供的技术方案可以包括以下有益效果:

19、本公开示例性实施方式中,通过将延迟锁相环分为副通路和主通路,通过副通路对输入时钟信号进行调整,以获得输出时钟信号,同时,通过主通路将与输出时钟信号具有相同相位的输出时钟复制信号输出,用于后续的指令控制中。由于副通路在相位调整过程中会先对输入时钟信号进行分频,并且在延时锁相环锁定过程中,以及待机状态下,分频时钟信号具有不同的频率;通过在待机状态下使用较低的第二频率,可以在延迟锁相环待机的情况下,在不影响延迟锁相环输出精度的情况下,减小延迟锁相环的待机电流,达到减小延迟锁相环功耗的目的。

20、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本公开。

技术特征:

1.一种延迟锁相环,其特征在于,包括:

2.根据权利要求1所述的延迟锁相环,其特征在于,所述副通路包括:

3.根据权利要求2所述的延迟锁相环,其特征在于,所述主通路包括:

4.根据权利要求3所述的延迟锁相环,其特征在于,所述副通路还包括第一时钟输出使能单元,所述输出时钟信号通过所述第一时钟输出使能单元传输至所述相位检测器;

5.根据权利要求4所述的延迟锁相环,其特征在于,所述第一时钟输出使能单元的固有延迟与所述第二时钟输出使能单元的固有延迟相同。

6.根据权利要求2-5中任一项所述的延迟锁相环,其特征在于,所述第一分频器用于,在所述第一延迟线锁定后,将所述分频时钟信号的频率从所述第一频率降低为所述第二频率。

7.根据权利要求6所述的延迟锁相环,其特征在于,所述第一分频器包括:

8.根据权利要求7所述的延迟锁相环,其特征在于,所述分频单元包括多个依次串接的触发器,和多个第二多路选择器;

9.根据权利要求8所述的延迟锁相环,其特征在于,所述触发器有四个,所述第二多路选择器有三个;

10.根据权利要求8所述的延迟锁相环,其特征在于,所述延迟单元包括多个串接的反相器。

11.根据权利要求10所述的延迟锁相环,其特征在于,在所述反相器和所述触发器的延迟相同的情况下,所述反相器的个数与所述触发器的个数相同。

12.根据权利要求7-11中任一项所述的延迟锁相环,其特征在于,所述第一分频器还包括驱动器,所述驱动器的输入端与所述第一多路选择器的输出端相连,所述驱动器的输出端输出所述分频时钟信号。

13.根据权利要求3所述的延迟锁相环,其特征在于,所述第二分频器与所述第一分频器具有相同的结构。

14.一种延迟锁相环控制方法,其特征在于,所述延迟锁相环包括主通路和副通路;所述控制方法包括:

15.一种电子设备,其特征在于,包括:如权利要求1-13中任一项所述的延迟锁相环。

技术总结

本公开是关于一种延迟锁相环、延迟锁相环控制方法及电子设备,涉及集成电路技术领域。该延迟锁相环包括:副通路,用于将输入时钟信号进行分频产生分频时钟信号,在延迟锁相环锁定过程中,对具有第一频率的分频时钟信号进行调整获得输出时钟信号;在延迟锁相环锁定处于待机状态的情况下,调整分频时钟信号具有第二频率;其中,第二频率低于第一频率;主通路,用于在获取到目标指令的情况下,输出与输出时钟信号相位相同的输出时钟复制信号。本公开可以降低延迟锁相环的功耗。

技术研发人员:谷银川

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!