放大器的制作方法

本申请内容系关于电路,尤指一种放大器电路。

背景技术:

1、对于包含两级放大电路的放大器来说,若第二级放大电路是由叠接的晶体管构成,则为使第二级放大电路能具有ab类放大性的特性,叠接的p型晶体管和n型晶体管的输入电压可能无法设计成相等。也就是说,对于叠接的p型晶体管和n型晶体管需给予不同的输入电压以确保工作正常。一般的作法会使用交流(ac)耦合电容耦接在叠接的p型晶体管的闸极和n型晶体管的闸极之间,但这样的作法会导致第一级放大电路的输出讯号在传输至第二级放大电路的过程中衰减,导致放大电路整体的效能不佳。

技术实现思路

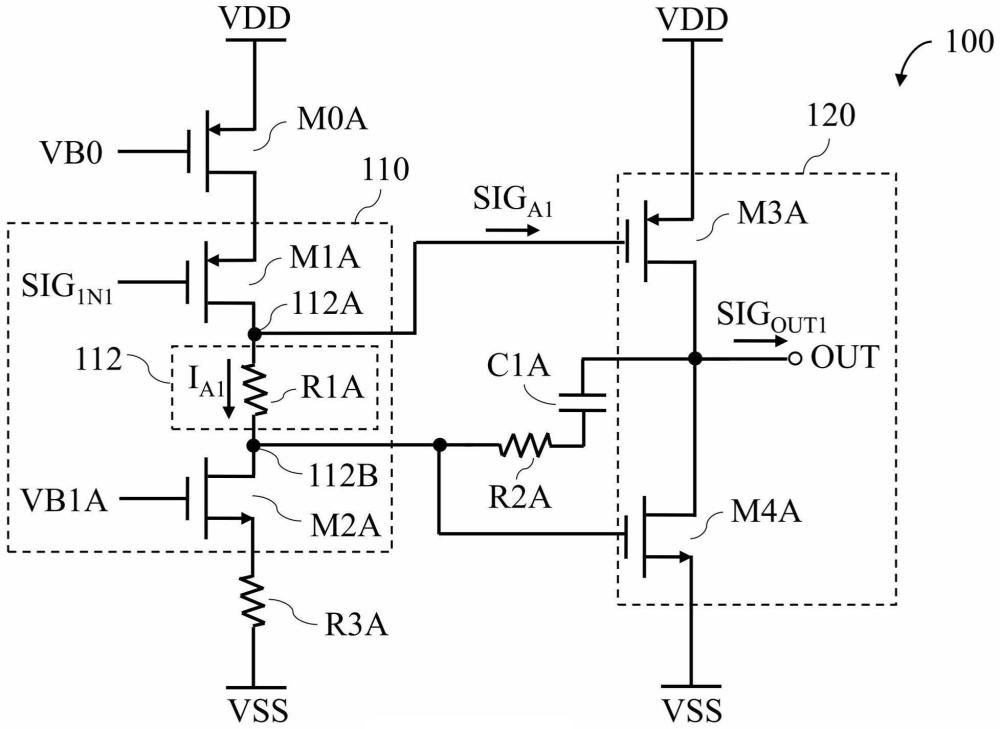

1、本揭露的一实施例提供一种放大器,放大器包含第一级放大电路及第二级放大电路。第一级放大电路包含第一晶体管、第二晶体管及第一电位差产生单元。第一晶体管具有第一端、第二端及控制端,该第一晶体管之该第二端用以输出第一放大讯号,及该第一晶体管之该控制端用以接收第一输入讯号。第二晶体管具有第一端、第二端及控制端,该第二晶体管之控制端用以接收第一偏压。第一电位差产生单元耦接于该第一晶体管之该第二端及该第二晶体管之该第二端之间,用以依据流经该第一晶体管及该第二晶体管的一电流,于该第一电位差产生单元的一第一端及一第二端之间提供一电位差。第二级放大电路包含第三晶体管及第四晶体管。第三晶体管具有第一端、第二端及控制端,该第三晶体管之该第一端用以接收第一电压及该第三晶体管之该第二端用以输出第一输出讯号。第四晶体管具有第一端、第二端及控制端,该第四晶体管之该第一端用以接收第二电压,及该第四晶体管之该第二端耦接于该第三晶体管的该第二端。其中该第三晶体管的该控制端及该第四晶体管的该控制端耦接于该第一电位差产生单元的相异两端。

2、本申请的实施例所提供的放大器可以利用电位差产生单元在第一级放大电路的输出端提供电位差,使得第二级放大电路中叠接的晶体管可以接收到不同直流位准的输入讯号,从而提高放大器的效能。此外,由于电位差产生单元是通过电阻性的阻抗来提供直流电位差,因此相较于在第二级放大电路中使用交流耦合电容的放大器,本申请的放大器可以支持输入讯号为低频的应用,且第一级放大电路所输出的放大讯号传递至第二级也较不会衰减,因此可以提高放大器的整体效能。

技术特征:

1.一种放大器,包含:

2.如权利要求1所述之放大器,其中:

3.如权利要求1所述之放大器,其中:

4.如权利要求1至3中任一项所述之放大器,其中:

5.如权利要求1至3中任一项所述之放大器,其中:

6.如权利要求1至3中任一项所述之放大器,其中该第一级放大电路还包括一第九晶体管,具有第一端、第二端及控制端,且其中:

7.如权利要求1至3中任一项所述之放大器,其中该第一电位差产生单元包括一电阻。

8.如权利要求1至3中任一项所述之放大器,其中该第一电位差产生单元包括:

9.如权利要求8所述之放大器,其中该第一电位差产生单元还包括:

10.如权利要求1至3中任一项所述之放大器,还包含串联在该第一电位差产生单元之该第二端及该第三晶体管之该第二端之间的一电阻及一电容。

技术总结

本公开涉及放大器。放大器包含第一级放大电路及第二级放大电路。第一级放大电路包含第一晶体管、第二晶体管及电位差产生单元。第一晶体管具有第一端、第二端用以输出放大讯号,及控制端用以接收输入讯号。第二晶体管具有第一端、第二端及控制端用以接收偏压。电位差产生单元用以依据流经第一晶体管及第二晶体管的电流,于第一电位差产生单元的第一端及第二端之间提供电位差。第二级放大电路是以第一电位差产生单元的第一端及第二端的电压作为第二级放大电路的输入讯号。

技术研发人员:黄诗雄

受保护的技术使用者:瑞昱半导体股份有限公司

技术研发日:

技术公布日:2024/1/25

- 还没有人留言评论。精彩留言会获得点赞!