电路板的制备方法与流程

本申请涉及电路板设计领域,具体涉及一种电路板的制备方法。

背景技术:

1、电路板的不同线路层之间的电连接通常通过在电路板中开设盲孔并在盲孔中形成导电件的方式实现。制备导电件的方式包括但不限于化学镀和电镀。由于盲孔尺寸相对较小,导电件的形成过程中需要对电路板整个板面进行化学镀或电镀,导致电路板板面在盲孔区域外的导电层上也形成镀层。因此后续需要同时蚀刻导电层和导电层上的镀层,从而增加了形成第二线路层时的蚀刻厚度,蚀刻厚度的增加导致第二线路层的线宽损失增加。

技术实现思路

1、鉴于此,本申请提供一种减少第二线路层线宽损失的电路板的制备方法。

2、本申请提供的一种电路板的制备方法,包括:

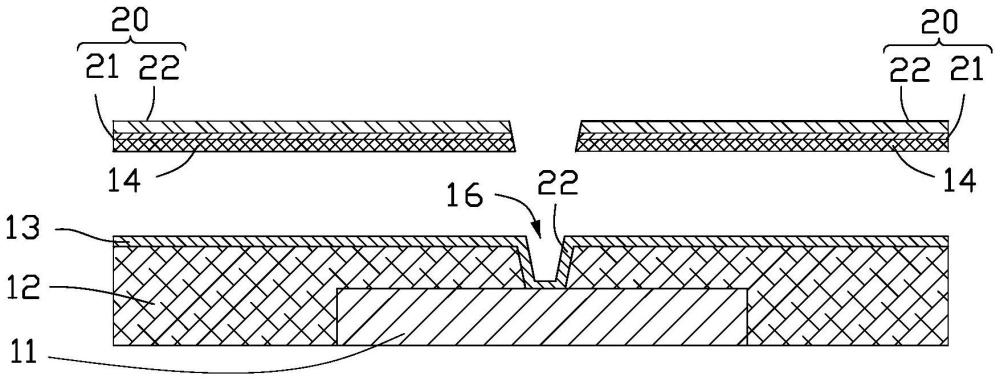

3、提供线路基板,所述线路基板包括第一线路层和依次叠设的基材层、第一导电层和可剥离层,所述第一线路层内埋于所述基材层或设置于所述基材层远离所述第一导电层的表面,所述可剥离层开设有盲孔,所述盲孔贯穿所述可剥离层和所述基材层,且所述第一线路层形成所述盲孔的底部;

4、在所述盲孔内以及在所述可剥离层上形成第二导电层;

5、剥离所述可剥离层,从而露出所述第一导电层和形成导电孔;

6、在所述第一导电层的表面形成线路图案,部分所述线路图案还填充于所述导电孔内形成导电件,所述导电件电连接所述第一线路层和所述线路图案,部分所述第一导电层露出于所述线路图案;

7、蚀刻露出于所述线路图案的所述第一导电层,蚀刻后的所述第一导电层和所述线路图案共同形成第二线路层,得到所述电路板。

8、可选地,所述线路基板的制备包括:

9、将半固化片压合在线路单元上,所述线路单元包括基层和设于所述基层表面的所述第一线路层,使得所述半固化片位于所述基层的表面且所述第一线路层内埋于所述半固化片中,所述基层和所述半固化片共同形成所述基材层;

10、依次叠设含有所述第一线路层的所述基材层、所述第一导电层和所述可剥离层,并进行压合;

11、开设贯穿所述可剥离层和所述基材层的所述盲孔。

12、可选地,所述第二导电层的制备包括:

13、通过化学镀在所述盲孔内和所述可剥离层上形成第一镀层;

14、在所述第一镀层上电镀形成第二镀层,在所述盲孔内,所述第二镀层咬蚀所述第一镀层,且所述第二镀层连接于所述盲孔上。

15、可选地,所述第二镀层采用水平电镀方式形成。

16、可选地,所述可剥离层的材料为热解胶,所述可剥离层通过加热方式剥离。

17、可选地,形成所述线路图案的步骤包括:

18、在所述第一导电层上贴图形化干膜,所述图形化干膜暴露所述导电孔和部分所述第一导电层;

19、在所述导电孔内以及露出的部分所述第一导电层上进行电镀;

20、移除图形化干膜。

21、可选地,所述线路图案采用垂直连续电镀方式形成。

22、可选地,通过激光开孔形成所述盲孔。

23、可选地,所述导电件为导电柱。

24、相比于现有技术,本申请通过在基板中开设盲孔暴露第一线路层,之后在盲孔和可剥离层上形成第二导电层,使得盲孔变成导电孔(后续电镀形成电连接的导电柱)。之后再将可剥离层剥离,使得在可剥离层上的第二导电层被剥离,减少后续蚀刻形成第二线路层的蚀刻厚度,因此可以减少线路蚀刻对第二线路的宽度影响,减少第二线路层的线宽损失。

技术特征:

1.一种电路板的制备方法,其特征在于,包括:

2.如权利要求1所述的电路板的制备方法,其特征在于,所述线路基板的制备包括:

3.如权利要求1所述的电路板的制备方法,其特征在于,所述第二导电层的制备包括:

4.如权利要求3所述的电路板的制备方法,其特征在于,所述第二镀层采用水平电镀方式形成。

5.如权利要求1所述的电路板的制备方法,其特征在于,所述可剥离层的材料为热解胶,所述可剥离层通过加热方式剥离。

6.如权利要求1所述的电路板的制备方法,其特征在于,形成所述线路图案的步骤包括:

7.如权利要求6所述的电路板的制备方法,其特征在于,所述线路图案采用垂直连续电镀方式形成。

8.如权利要求1所述的电路板的制备方法,其特征在于,通过激光开孔形成所述盲孔。

9.如权利要求1所述的电路板的制备方法,其特征在于,所述导电件为导电柱。

技术总结

本申请提出一种电路板的制备方法,包括:提供包括第一线路层和依次叠设的基材层、第一导电层和可剥离层的线路基板,第一线路层内埋于基材层或设置于基材层远离第一导电层的表面,可剥离层开设有贯穿可剥离层和基材层的盲孔,第一线路层形成盲孔的底部;盲孔内以及可剥离层上形成第二导电层;剥离可剥离层,从而露出第一导电层和形成导电孔;第一导电层的表面形成线路图案,部分线路图案还填充于导电孔内形成导电件,导电件电连接第一线路层和线路图案,部分第一导电层露出于线路图案;蚀刻露出于线路图案的第一导电层,蚀刻后的第一导电层和线路图案共同形成第二线路层。本申请提供电路板的制备方法可以减少第二线路层的线宽损失。

技术研发人员:王玉超

受保护的技术使用者:礼鼎半导体科技秦皇岛有限公司

技术研发日:

技术公布日:2024/1/25

- 还没有人留言评论。精彩留言会获得点赞!