SRAM单元及其形成方法、以及SRAM器件与流程

本发明实施例涉及半导体制造领域,尤其涉及一种sram单元及其形成方法、以及sram器件。

背景技术:

1、在目前的半导体产业中,集成电路产品主要可分为三大类型:逻辑、存储器和模拟电路,其中存储器件在集成电路产品中占了相当大的比例。随着半导体技术发展,对存储器件进行更为广泛的应用,需要将所述存储器件与其他器件区同时形成在一个芯片上,以形成嵌入式半导体存储装置。例如将所述存储器件内嵌置于中央处理器,则需要使得所述存储器件与嵌入的中央处理器平台进行兼容,并且保持原有的存储器件的规格及对应的电学性能。

2、一般地,需要将所述存储器件与嵌入的标准逻辑装置进行兼容。对于嵌入式半导体器件来说,其通常分为逻辑区和存储区,逻辑区通常包括逻辑器件,存储区则包括存储器件。随着存储技术的发展,出现了各种类型的半导体存储器,例如静态随机存储器(staticrandom access memory,sram)、动态随机存储器(dynamic random access memory,dram)、可擦除可编程只读存储器(erasable programmable read-only memory,eprom)、电可擦除可编程只读存储器(electrically erasable programmable read-only,eeprom)和闪存(flash)。由于静态随机存储器具有低功耗和较快工作速度等优点,使得静态随机存储器及其形成方法受到越来越多的关注。

3、但是,sram器件的面积仍有待缩小。

技术实现思路

1、本发明实施例解决的问题是提供一种sram单元及其形成方法、以及sram器件,减小sram所占据的面积,有利于缩小sram器件尺寸,有利于使相邻器件之间实现更小的距离,进而有利于提高器件的集成度。

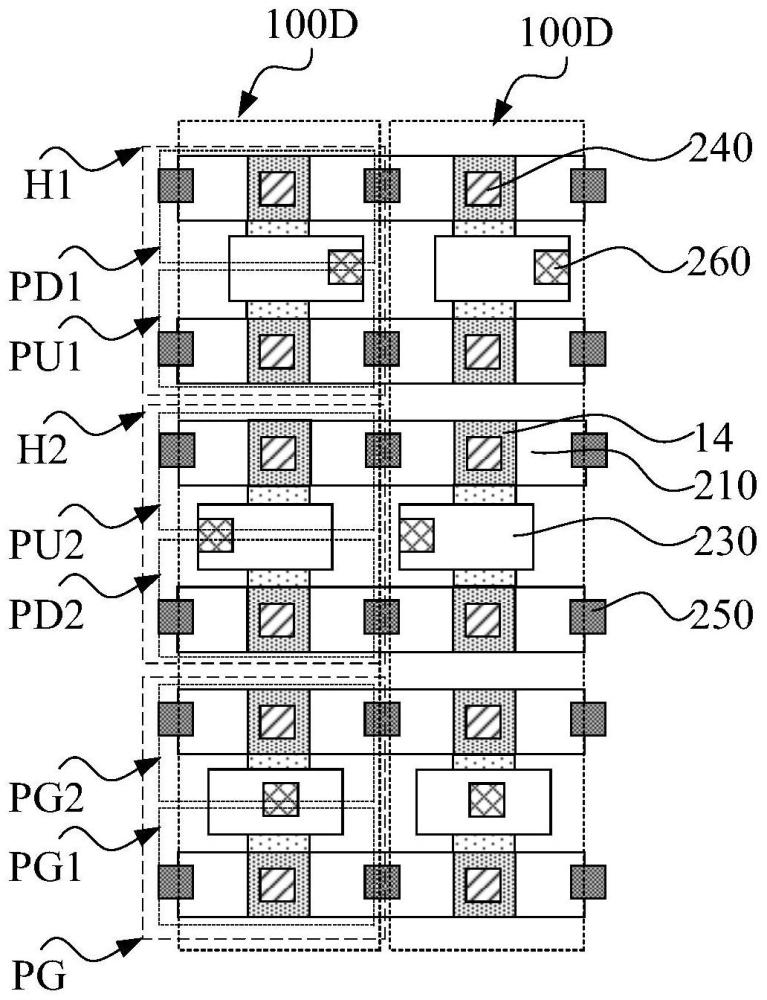

2、为解决上述问题,本发明实施例提供一种sram单元,包括:衬底,包括沿第一方向排列的第一反相器区、第二反相器区以及传送门区;第一反相器区、第二反相器区以及传送门区均包括沿第一方向排列的相邻有源区;叠层结构,位于有源区的衬底上,叠层结构包括沿垂直于衬底方向依次堆叠的底部掺杂层、沟道层以及顶部掺杂层,底部掺杂层和顶部掺杂层的掺杂类型相同;第一反相器区和第二反相器区中,相邻有源区的沟道层的导电类型不同;传送门区中,相邻有源区的沟道层的导电类型相同;第一介电层,沿第一方向位于叠层结构之间且覆盖叠层结构顶部;栅极结构,位于相邻有源区之间的第一介电层中,栅极结构沿垂直于衬底的方向延伸且与沟道层相对设置。

3、相应的,本发明实施例还提供一种sram器件,包括:多个阵列排布的sram单元,sram单元为本实施例提供的sram单元。

4、相应的,本发明实施例还提供一种sram单元的形成方法,包括:提供衬底,包括sram单元区,sram单元区沿第一方向排列的第一反相器区、第二反相器区以及传送门区;第一反相器区、第二反相器区以及传送门区均包括沿第一方向排列的相邻有源区;在衬底上形成位于有源区的叠层结构、以及沿第一方向位于叠层结构之间且覆盖叠层结构顶部的第一介电层,叠层结构包括沿垂直于衬底方向依次堆叠的底部掺杂层、沟道层以及顶部掺杂层,底部掺杂层和顶部掺杂层的掺杂类型相同;第一反相器区和第二反相器区中,相邻有源区的沟道层的导电类型不同;传送门区中,相邻有源区的沟道层的导电类型相同;在相邻有源区之间的第一介电层中形成栅极结构,栅极结构沿垂直于衬底的方向延伸且与沟道层相对设置。

5、与现有技术相比,本发明实施例的技术方案具有以下优点:

6、本发明实施例提供的sram单元,叠层结构中的底部掺杂层、沟道层以及顶部掺杂层沿垂直于衬底方向依次堆叠,栅极结构位于相邻有源区之间的第一介电层中,栅极结构与相邻的叠层结构用于构成mos器件,与平面型器件、以及栅极结构环绕或包围沟道层的器件相比,本发明实施例提供的sram单元中,栅极结构沿垂直于衬底的方向延伸且与沟道层相对设置,且第一反相器区、第二反相器区以及传送门区中,相邻的有源区共用栅极结构,有利于减小sram单元占据的面积,相应有利于缩小器件尺寸;而且,第一介电层的设置,一方面能够为垂直堆叠的叠层结构提供机械支撑作用,降低叠层结构在半导体结构的形成制程中,发生倒塌的几率,另一方面还有利于允许相邻器件之间实现更小的间距(proximity),进而有利于提高器件的集成度。

7、本发明实施例提供的sram单元的形成方法中,第一反相器区、第二反相器区以及传送门区均包括沿第一方向排列的相邻有源区;在衬底上形成位于有源区的叠层结构、以及沿第一方向位于叠层结构之间且覆盖叠层结构顶部的第一介电层,叠层结构中的底部掺杂层、沟道层以及顶部掺杂层沿垂直于衬底方向依次堆叠,并且在相邻有源区的第一介电层中形成栅极结构,栅极结构沿垂直于衬底的方向延伸且与沟道层相对设置,栅极结构与相邻的叠层结构用于构成mos器件,与平面型器件、以及栅极结构环绕或包围沟道层的器件相比,本发明实施例形成的sram单元中,栅极结构沿垂直于衬底的方向延伸且与沟道层相对设置,且第一反相器区、第二反相器区以及传送门区中,相邻的有源区共用栅极结构,有利于减小sram单元占据的面积,相应有利于缩小器件尺寸;而且,第一介电层一方面能够为垂直堆叠的叠层结构提供机械支撑作用,降低叠层结构在半导体结构的形成制程中,发生倒塌的几率,另一方面还有利于允许相邻器件之间实现更小的间距(proximity),进而有利于提高器件的集成度。

技术特征:

1.一种sram单元,其特征在于,包括:

2.如权利要求1所述的sram单元,其特征在于,所述sram单元还包括:底部互连层,在所述叠层结构和第一介电层侧部的衬底上,沿第二方向上,所述底部互连层与底部掺杂层的侧壁对应相接触且暴露出所述沟道层,所述第二方向平行于衬底且与第一方向相垂直;

3.如权利要求2所述的sram单元,其特征在于,所述叠层结构中,所述底部掺杂层用于作为源极,所述顶部掺杂层用于作为漏极;所述底部互连层用于作为电源轨;

4.如权利要求2所述的sram单元,其特征在于,所述叠层结构中,所述底部掺杂层用于作为漏极,所述顶部掺杂层用于作为源极;

5.如权利要求1所述的sram单元,其特征在于,所述叠层结构中,所述底部掺杂层和顶部掺杂层中的任意一个用于作为源极,另一个用于作为漏极;所述叠层结构还包括位于所述沟道层和漏极之间的缓变掺杂层,所述缓变掺杂层的掺杂类型与漏极的掺杂类型相同,且所述缓变掺杂层的掺杂浓度低于所述漏极的掺杂浓度。

6.如权利要求1所述的sram单元,其特征在于,所述sram单元还包括:第二介电层,位于所述叠层结构和第一介电层侧部的衬底上且覆盖所述底部互连层;所述底部导电结构贯穿位于所述底部互连层顶部上的第二介电层。

7.如权利要求1所述的sram单元,其特征在于,所述栅极结构与相邻的叠层结构之间具有间隔。

8.一种sram器件,其特征在于,包括:多个阵列排布的sram单元,所述sram单元为如权利要求1至7任一项所述的sram单元。

9.一种sram单元的形成方法,其特征在于,包括:

10.如权利要求9所述的sram单元的形成方法,其特征在于,平行于衬底且与第一方向相垂直的方向为第二方向,所述sram单元的形成方法还包括:

11.如权利要求10所述的sram单元的形成方法,其特征在于,所述叠层结构中,所述底部掺杂层用于作为源极,所述顶部掺杂层用于作为漏极;形成所述底部互连层的步骤中,所述底部互连层用于作为电源轨;

12.如权利要求10所述的sram单元的形成方法,其特征在于,所述叠层结构中,所述底部掺杂层用于作为漏极,所述顶部掺杂层用于作为源极;

13.如权利要求9所述的sram单元的形成方法,其特征在于,所述衬底还包括沿第二方向与所述有源区相邻的互连区;形成所述叠层结构和第一介电层的步骤包括:在所述衬底上形成位于有源区和互连区的初始叠层结构以及沿第一方向位于所述初始叠层结构之间的初始隔离墙,所述初始叠层结构和初始隔离墙沿所述第二方向延伸;

14.如权利要求13所述的sram单元的形成方法,其特征在于,形成所述初始叠层结构和初始隔离墙的步骤包括:在所述衬底上形成分立的初始隔离墙,暴露出所述有源区;在所述初始隔离墙之间的衬底上形成所述初始叠层结构。

15.如权利要求9所述的sram单元的形成方法,其特征在于,形成所述叠层结构和第一介电层的步骤中,所述叠层结构中,所述底部掺杂层和顶部掺杂层中的任意一个用于作为源极,另一个用于作为漏极;在形成所述叠层结构的步骤中,所述叠层结构还包括位于所述沟道层和漏极之间的缓变掺杂层,所述缓变掺杂层的掺杂类型与漏极的掺杂类型相同,且所述缓变掺杂层的掺杂浓度低于所述漏极的掺杂浓度。

16.如权利要求10所述的sram单元的形成方法,其特征在于,在形成所述底部互连层之后,在所述栅极区的第一介电层中形成栅极结构。

17.如权利要求10或16所述的sram单元的形成方法,其特征在于,形成所述底部互连层的步骤包括:在所述叠层结构和第一介电层侧部的衬底上覆盖互连材料层,暴露出所述沟道层和顶部掺杂层;去除位于所述互连区之间的互连材料层,剩余位于所述互连区上的互连材料层用于作为所述底部互连层。

18.如权利要求10所述的sram单元的形成方法,其特征在于,所述sram单元的形成方法还包括:在形成所述底部互连层之后,且在形成底部导电结构之前,在所述叠层结构和第一介电层侧部的衬底上形成第二介电层,覆盖所述底部互连层;在形成所述底部导电结构的步骤中,所述底部导电结构贯穿位于所述底部互连层顶部上的第二介电层。

19.如权利要求9所述的sram单元的形成方法,其特征在于,在所述栅极区的第一介电层中形成栅极结构的步骤包括:在所述栅极区的第一介电层中形成栅极沟槽,沿垂直于衬底的投影面上,所述栅极沟槽与所述沟道层之间具有重叠区域,且所述栅极沟槽的侧壁与所述叠层结构之间具有间隔;在所述栅极沟槽内形成所述栅极结构。

技术总结

一种SRAM单元及其形成方法、以及SRAM器件,SRAM单元包括:第一反相器区、第二反相器区以及传送门区均包括沿第一方向排列的相邻有源区;叠层结构,位于有源区的衬底上,叠层结构包括沿垂直于衬底方向依次堆叠的底部掺杂层、沟道层以及顶部掺杂层;第一反相器区和第二反相器区中,相邻有源区的沟道层的导电类型不同;传送门区中,相邻有源区的沟道层的导电类型相同;第一介电层,沿第一方向位于叠层结构之间且覆盖叠层结构顶部;栅极结构,位于相邻有源区之间的第一介电层中,栅极结构沿垂直于衬底的方向延伸且与沟道层相对设置。本发明实施例减小SRAM单元占据的面积,使相邻器件之间实现更小的距离,进而有利于提高器件的集成度。

技术研发人员:汪刘建,纪世良,张海洋

受保护的技术使用者:中芯国际集成电路制造(上海)有限公司

技术研发日:

技术公布日:2024/3/5

- 还没有人留言评论。精彩留言会获得点赞!