半导体结构及其形成方法与流程

本发明实施例涉及半导体制造领域,尤其涉及一种半导体结构及其形成方法。

背景技术:

1、半导体集成电路(ic)行业经历了快速增长。集成电路行业在材料和设计方面的技术进步已经产生了一代又一代的集成电路。每一代都有比前一代更小且更复杂的电路。但是,这些进步增加了加工和制造集成电路的复杂性,为了实现这些进步,在集成电路加工和制造方面也需要有类似的发展。在集成电路的发展过程中,功能密度(即每个芯片面积上的互连器件数量)逐渐提高,而几何尺寸(即使用制造工艺可以制造的最小元件)却在逐步减小。

2、一种类型的电容器是金属-绝缘体-金属(metal insulator metal,mim)电容器,通常用于混合信号器件和逻辑器件(如嵌入式存储器和射频器件等)中。mim电容器通常用于在各种半导体器件中储存电荷。目前,为了满足高性能计算机(high performancecomputing,hpc)高性能计算的性能需求,mim电容的电容密度也在逐渐增加,一般一层绝缘体可以提供20ff/um^2的电容,对于需要提供较高电容(例如300ff/um^2)的mim电容器,目前的做法就是堆叠,详情如专利us9627312b2所述,而传统的mim电容器,一个极板就需要一张光罩,堆叠多层极板就需要更多的光罩。如图1所示,传统mim电容的结构包括:自下而上依次堆叠的底部电极层21、介质层20以及顶部电极层22,然而每个电极层的形貌不同,都需要采用不同的光罩形成,电极层的个数越多,所需的光罩也越多,从而mim电容的形成方法较为复杂,工艺成本较高。

技术实现思路

1、本发明实施例解决的问题是提供一种半导体结构及其形成方法,有利于节约工艺光罩,从而节约工艺成本。

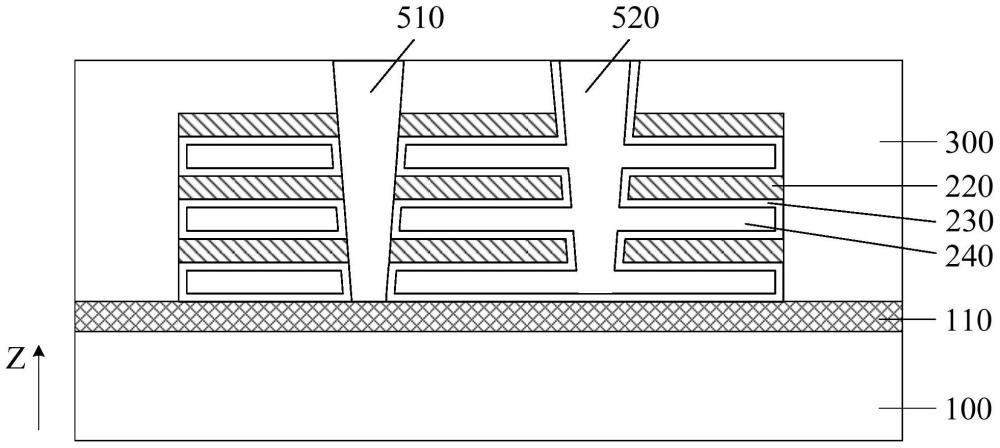

2、为解决上述问题,本发明实施例提供一种半导体结构,包括:基底;电极叠层,位于所述基底上,所述电极叠层包括多个沿纵向依次交替堆叠的第一电极层和第二电极层;第一电连接结构,贯穿所述电极叠层且与所述第一电极层电连接;第二电连接结构,贯穿所述电极叠层且与所述第二电极层电连接;介质层,位于相邻所述第一电极层和第二电极层之间,所述介质层还沿所述第一电连接结构与第二电极层之间界面向上延伸至上一层的第一电极层与第二电极层之间、以及沿所述第二电连接结构与第一电极层之间界面向下延伸至下一层的第一电极层与第二电极层之间。

3、相应的,本发明实施例还提供一种半导体结构的形成方法,包括:提供基底,所述基底上形成有叠层结构,包括多个沿纵向依次交替堆叠的第一目标层和第二目标层,所述第一目标层和第二目标层中的任一种为第一电极层,另一种为牺牲层;形成贯穿所述叠层结构的第一通孔;在所述第一通孔中形成与所述第一电极层电连接的第一电连接结构;形成所述第一电连接结构后,形成贯穿所述叠层结构的第二通孔;通过所述第二通孔去除所述牺牲层,形成露出所述第一电极层、以及所述第一电连接结构与所述牺牲层相接触的侧壁的沟槽,所述沟槽与所述第二通孔连通;形成保形覆盖所述沟槽和第二通孔的各个面的第一介质层;形成所述第一介质层后,填充所述沟槽和第二通孔,在所述沟槽中形成第二电极层,在所述第二通孔中形成第二电连接结构。

4、与现有技术相比,本发明实施例的技术方案具有以下优点:

5、本发明实施例提供的半导体结构中,第一电连接结构贯穿所述电极叠层且与所述第一电极层电连接,第二电连接结构贯穿所述电极叠层且与所述第二电极层电连接,介质层位于相邻所述第一电极层和第二电极层之间,所述介质层还沿所述第一电连接结构与第二电极层之间界面向上延伸至上一层的第一电极层与第二电极层之间、以及沿所述第二电连接结构与第一电极层之间界面向下延伸至下一层的第一电极层与第二电极层之间;本发明实施例中,利用电容器自身的介质层隔离第一电连接结构与第二电极层、以及隔离第二电连接结构与第一电极层,有利于简化电容器的形成工艺,且相邻第一电极层、第二电极层、以及位于两者之间的介质层均构成电容器,有利于提高等效电容密度,同时,通过电极叠层获得较高的等效电容密度,有利于节约形成各个第一电极层和第二电极层的光罩,从而有利于节约工艺光罩,进而节约工艺成本。

6、本发明实施例提供的半导体结构的形成方法中,通过所述第二通孔去除所述牺牲层,形成露出所述第一电极层、以及所述第一电连接结构与所述牺牲层相接触的侧壁的沟槽,所述沟槽与所述第二通孔连通,形成保形覆盖所述沟槽和第二通孔的各个面的第一介质层,形成所述第一介质层后,填充所述沟槽和第二通孔,在所述沟槽中形成第二电极层,在所述第二通孔中形成第二电连接结构;本发明实施例中,利用电容器自身的介质层隔离第一电连接结构与第二电极层、以及隔离第二电连接结构与第一电极层,有利于简化电容器的形成工艺,且相邻第一电极层、第二电极层、以及位于两者之间的介质层均构成电容器,有利于提高等效电容密度,同时,通过叠层结构获得较高的等效电容密度,从而有利于节约工艺光罩,进而节约工艺成本。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.如权利要求1所述的半导体结构,其特征在于,所述第一电极层和第一电连接结构为一体化结构,或者,所述第二电极层与第二电连接结构为一体化结构。

3.如权利要求1所述的半导体结构,其特征在于,所述半导体结构还包括:刻蚀停止层,位于所述基底与所述第一电极层之间。

4.如权利要求1所述的半导体结构,其特征在于,所述第一电极层的材料包括w、cu、co、tin、ti、ta、tan、ru、run和al中的一种或多种;所述第二电极层的材料包括w、cu、co、tin、ti、ta、tan、ru、run和al中的一种或多种。

5.如权利要求1所述的半导体结构,其特征在于,所述第一电连接结构的材料包括w、cu、co、tin、ti、ta、tan、ru、run和al中的一种或多种;所述第二电连接结构的材料包括w、cu、co、tin、ti、ta、tan、ru、run和al中的一种或多种。

6.如权利要求1所述的半导体结构,其特征在于,所述介质层的材料包括hfo2、hfsio、tio2、hfzro、hfsion、hftao、hftio、ta2o5、zro2、zrsio2、al2o3、srtio3、basrtio和sin中的任意一种或多种。

7.一种半导体结构的形成方法,其特征在于,包括:

8.如权利要求7所述的半导体结构的形成方法,其特征在于,所述第二电极层与第二电连接结构为一体化结构。

9.如权利要求7所述的半导体结构的形成方法,其特征在于,形成贯穿所述叠层结构的第一通孔的步骤包括:形成覆盖所述叠层结构顶部的第一掩膜层;

10.如权利要求7所述的半导体结构的形成方法,其特征在于,形成贯穿所述叠层结构的第二通孔的步骤包括:形成覆盖所述叠层结构和第一电连接结构顶部的第二掩膜层;

11.如权利要求7所述的半导体结构的形成方法,其特征在于,形成贯穿所述电极叠层的第一通孔之前,还包括:形成覆盖所述叠层结构的第二介质层;

12.如权利要求11所述的半导体结构的形成方法,其特征在于,在所述第一通孔中形成与所述第一电极层电连接的第一电连接结构的步骤包括:形成覆盖所述第二介质层、填充所述第一通孔的电连接结构材料层;

13.如权利要求7所述的半导体结构的形成方法,其特征在于,通过所述第二通孔去除所述牺牲层的步骤中,对所述牺牲层与所述第一电极层的刻蚀选择比大于或等于3。

14.如权利要求7所述的半导体结构的形成方法,其特征在于,所述提供所述基底的步骤中,所述牺牲层的材料包括氮化硅、无定形硅、氮化钛或钨。

15.如权利要求7所述的半导体结构的形成方法,其特征在于,采用湿法刻蚀工艺通过所述第二通孔去除所述牺牲层。

16.如权利要求7所述的半导体结构的形成方法,其特征在于,采用原子层沉积工艺形成保形覆盖所述沟槽和第二通孔的各个面的第一介质层。

17.如权利要求7所述的半导体结构的形成方法,其特征在于,采用原子层沉积工艺填充所述沟槽和第二通孔,形成所述第二电极层和第二电连接结构。

18.如权利要求7所述的半导体结构的形成方法,其特征在于,所述提供基底的步骤之前,还包括:形成覆盖所述基底的叠层材料层,包括多个沿纵向依次交替堆叠的第一目标层和第二目标层,所述第一目标层和第二目标层中的任一种为第一电极层,另一种为牺牲层;

19.如权利要求18所述的半导体结构的形成方法,其特征在于,所述提供基底的步骤中,所述基底和叠层材料层之间形成有刻蚀停止层;

技术总结

一种半导体结构及其形成方法,结构包括:基底;电极叠层,位于所述基底上,所述电极叠层包括多个沿纵向依次交替堆叠的第一电极层和第二电极层;第一电连接结构,贯穿所述电极叠层且与所述第一电极层电连接;第二电连接结构,贯穿所述电极叠层且与所述第二电极层电连接;介质层,位于相邻所述第一电极层和第二电极层之间,所述介质层还沿所述第一电连接结构与第二电极层之间界面向上延伸至上一层的第一电极层与第二电极层之间、以及沿所述第二电连接结构与第一电极层之间界面向下延伸至下一层的第一电极层与第二电极层之间。本发明有利于节约工艺光罩,进而节约工艺成本。

技术研发人员:金吉松

受保护的技术使用者:中芯国际集成电路制造(上海)有限公司

技术研发日:

技术公布日:2024/3/5

- 还没有人留言评论。精彩留言会获得点赞!